# CMOS CURRENT AMPLIFIERS

Giuseppe Palmisano Gaetano Palumbo Salvatore Pennisi

Kluwer Academic Publishers Boston/Dordrecht/London

# THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

# ANALOG CIRCUITS AND SIGNAL PROCESSING

Consulting Editor: Mohammed Ismail. Ohio State University

#### Related Titles:

DESIGN OF LOW-VOLTAGE LOW-POWER CMOS ΔΣΑ/D CONVERTERS, Vincenzo Peluso, Michiel Steyaert, Willy Sansen: ISBN: 0-7923-8417-2

THE DESIGN OF LOW-VOLTAGE, LOW-POWER SIGMA-DELTA MODULATORS, Shahriar Rabii, Bruce A. Wooley; ISBN: 0-7923-8361-3

TOP-DOWN DESIGN OF HIGH-PERFORMANCE SIGMA-DELTA MODULATORS, Fernando Medeiro, Angel Pérez-Verdú, Angel Rodríguez-Vázquez; ISBN: 0-7923-8352-4

DYNAMIC TRANSLINEAR AND LOG-DOMAIN CIRCUITS: Analysis and Synthesis, Jan Mulder, Wouter A. Serdijn, Albert C. van der Woerd, Arthur H. M. van Roermund; ISBN: 0-7923-8355-9

DISTORTION ANALYSIS OF ANALOG INTEGRATED CIRCUITS, Piet Wambacq. Willy Sansen; ISBN: 0-7923-8186-6

NEUROMORPHIC SYSTEMS ENGINEERING: Neural Networks in Silicon, edited by Tor Sverre Lande; ISBN: 0-7923-8158-0

DESIGN OF MODULATORS FOR OVERSAMPLED CONVERTERS, Feng Wang, Ramesh Harjani, ISBN: 0-7923-8063-0

SYMBOLIC ANALYSIS IN ANALOG INTEGRATED CIRCUIT DESIGN, Henrik Floberg, ISBN: 0-7923-9969-2

SWITCHED-CURRENT DESIGN AND IMPLEMENTATION OF OVERSAMPLING A/D CONVERTERS, Nianxiong Tan. ISBN: 0-7923-9963-3

CMOS WIRELESS TRANSCEIVER DESIGN, Jan Crois, Michiel Steyaert, ISBN: 0-7923-9960-9

DESIGN OF LOW-VOLTAGE, LOW-POWER OPERATIONAL AMPLIFIER CELLS, Ron

Hogervorst, Johan H. Huijsing, ISBN: 0-7923-9781-9

VLSI-COMPATIBLE IMPLEMENTATIONS FOR ARTIFICIAL NEURAL NETWORKS, Sied Mehdi Fakhraie, Kenneth Carless Smith, ISBN: 0-7923-9825-4

CHARACTERIZATION METHODS FOR SUBMICRON MOSFETs, edited by *Hisham Haddara*, ISBN: 0-7923-9695-2

LOW-VOLTAGE LOW-POWER ANALOG INTEGRATED CIRCUITS, edited by Wouter Serdijn, ISBN: 0-7923-9608-1

INTEGRATED VIDEO-FREQUENCY CONTINUOUS-TIME FILTERS: High-Performance Realizations in BiCMOS, Scott D. Willingham, Ken Martin, ISBN: 0-7923-9595-6

FEED-FORWARD NEURAL NETWORKS: Vector Decomposition Analysis, Modelling and Analog Implementation, Anne-Johan Annema, ISBN: 0-7923-9567-0

FREQUENCY COMPENSATION TECHNIQUES LOW-POWER OPERATIONAL AMPLIFIERS, Ruad Easchauzier, Johan Huijsing, ISBN: 0-7923-9565-4

ANALOG SIGNAL GENERATION FOR BIST OF MIXED-SIGNAL INTEGRATED CIRCUITS, Gordon W. Roberts, Albert K. Lu., ISBN: 0-7923-9564-6

INTEGRATED FIBER-OPTIC RECEIVERS, Aaron Buchwald, Kenneth W. Martin, ISBN: 0-7923-9549-2

MODELING WITH AN ANALOG HARDWARE DESCRIPTION LANGUAGE, H. Alan Mantooth, Mike Fiegenbaum, ISBN: 0-7923-9516-6

LOW-VOLTAGE CMOS OPERATIONAL AMPLIFIERS: Theory, Design and Implementation, Satoshi Sakurai, Mohammed Ismail, ISBN: 0-7923-9507-7

ANALYSIS AND SYNTHESIS OF MOS TRANSLINEAR CIRCUITS, Remco J. Wiegerink, ISBN 0-7923-9390-2

COMPUTER-AIDED DESIGN OF ANALOG CIRCUITS AND SYSTEMS, L. Richard Carley, Ronald S. Gyuresik, ISBN 0.7923-9351-1

HIGH-PERFORMANCE CMOR CONTINUOUS-TIME FILTERS, Jose Silva Martines, Michiel Steynger, Willy Sussen, ISBN: 0-7921-9339-2

# **CMOS CURRENT AMPLIFIERS**

by

Giuseppe Palmisano Gaetano Palumbo Salvatore Pennisi

Faculty of Engineering University of Catania, Italy

KLUWER ACADEMIC PUBLISHERS Boston / Dordrecht / London

## Distributors for North, Central and South America:

Kluwer Academic Publishers 101 Philip Drive Assinippi Park Norwell, Massachusetts 02061 USA Telephone (781) 871-6600 Fax (781) 871-6528 E-Mail <kluwer@wkap.com>

#### Distributors for all other countries:

Kluwer Academic Publishers Group

Distribution Centre

Post Office Box 322

3300 AH Dordrecht, THE NETHERLANDS

Telephone 31 78 6392 392

Fax 31 78 6546 474

E-Mail <orderdept@wkap.nl>

Electronic Services <a href="http://www.wkap.nl">http://www.wkap.nl</a>

# Library of Congress Cataloging-in-Publication Data

A C.I.P. Catalogue record for this book is available from the Library of Congress.

Copyright © 1999 by Kluwer Academic Publishers

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher, Kluwer Academic Publishers, 101 Philip Drive, Assinippi Park, Norwell, Massachusetts 02061

Printed on acid-free paper.

Printed in the United States of America

To our wives,

Alia

Michela

Stefania

# Contents

| Ac | know          | riedgments                                                   | ix       |  |  |  |  |

|----|---------------|--------------------------------------------------------------|----------|--|--|--|--|

|    | Abbreviations |                                                              |          |  |  |  |  |

| Pr | eface         |                                                              | xiii     |  |  |  |  |

| 1. | OPE           | RATIONAL AMPLIFIERS                                          | 1        |  |  |  |  |

|    | 1.1           | THE OPERATIONAL AMPLIFIER SET                                | 9        |  |  |  |  |

|    |               | OP-AMP CONFIGURATIONS                                        |          |  |  |  |  |

|    |               | THE GAIN BANDWIDTH TRADE-OFF                                 | 14<br>17 |  |  |  |  |

|    |               | CURRENT AMPLIFIERS USING VOLTAGE OP-AMPS                     |          |  |  |  |  |

|    |               | SIGNAL PROCESSING WITH CURRENT OP-AMPS                       |          |  |  |  |  |

|    |               | TOWARDS A TRUE COA                                           |          |  |  |  |  |

|    | 1.7           | PERFORMANCE PARAMETERS OF CURRENT AMPLIFIERS                 | 26       |  |  |  |  |

|    |               | 1.7.1 Further Comments                                       | 33       |  |  |  |  |

|    |               | REFERENCES                                                   | 40       |  |  |  |  |

| 2. | LOV           | V-DRIVE CURRENT AMPLIFIERS                                   | 45       |  |  |  |  |

|    | 2.1           |                                                              | 48       |  |  |  |  |

|    |               | 2.1.1 The CCII                                               | 48       |  |  |  |  |

|    |               | 2.1.2 Class A Input Stages                                   | 51       |  |  |  |  |

|    |               | 2.1.3 Class AB Input Stages                                  | 63       |  |  |  |  |

|    | 2.2           |                                                              | 69       |  |  |  |  |

|    |               | 2.2.1 Output Stages for COAs                                 | 70       |  |  |  |  |

|    |               | 2.2.2 Output Stages for VFCOAs                               | 74       |  |  |  |  |

|    | 2.3           |                                                              | 74       |  |  |  |  |

|    |               | 2.3.1 COA Configurations                                     | 75       |  |  |  |  |

|    |               | 2.3.2 VFCOA Configurations                                   | 79       |  |  |  |  |

|    | 2.4           |                                                              | 84       |  |  |  |  |

|    |               | 2.4.1 High-Speed Approaches                                  | 85       |  |  |  |  |

|    |               | 2.4.2 Design Control Considerations                          | 88       |  |  |  |  |

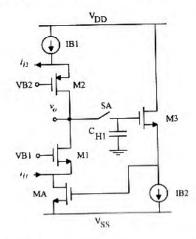

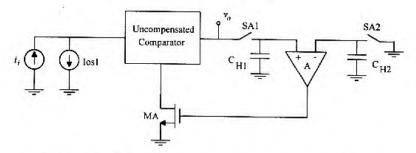

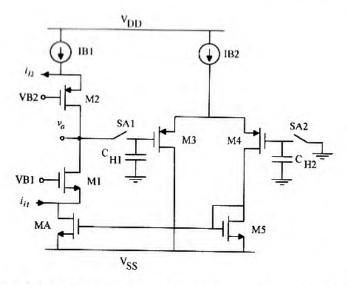

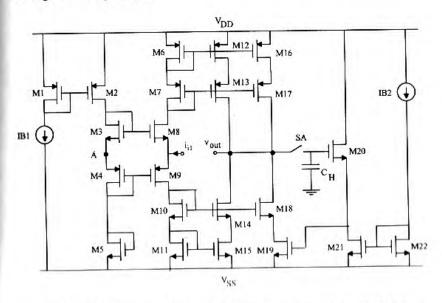

|    |               | 2.4.3 Offset Compensation                                    | 89       |  |  |  |  |

|    |               | 2.4.4 Design Examples                                        | 97       |  |  |  |  |

|    |               | REFERENCES                                                   | 102      |  |  |  |  |

| 3  | . HIG         | SH-DRIVE CURENT AMPLIFIERS                                   | 107      |  |  |  |  |

|    | 3.1           |                                                              | 108      |  |  |  |  |

|    |               | 3.1.1 Configurations                                         | 111      |  |  |  |  |

|    | 3.2           |                                                              | 113      |  |  |  |  |

|    |               | MODULATION                                                   |          |  |  |  |  |

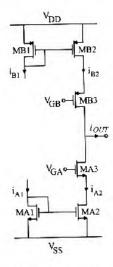

|    |               | 3.2.1 COS Based On Regular Cascoded Mirrors                  | 113      |  |  |  |  |

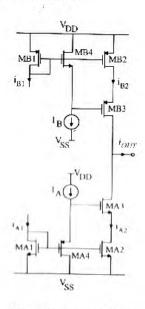

|    |               | 3 2.2 COS Based On Cascoded Mirrors With<br>Dynamic Matching | 115      |  |  |  |  |

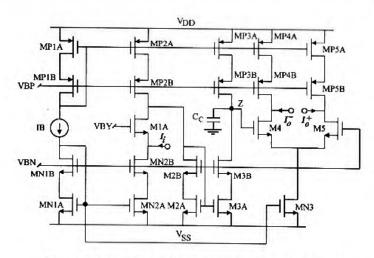

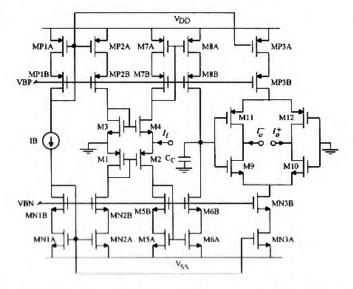

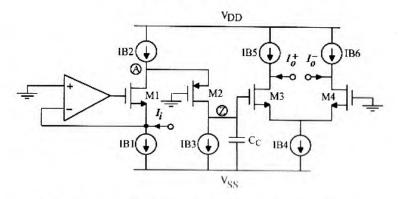

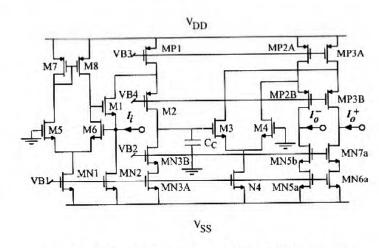

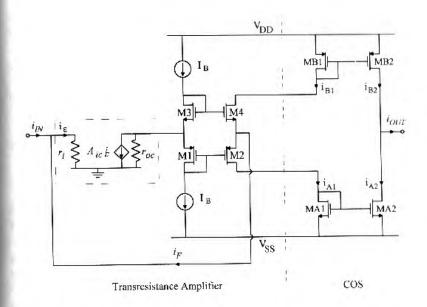

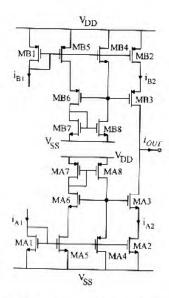

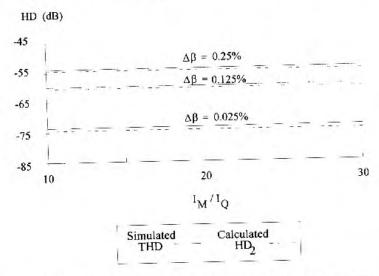

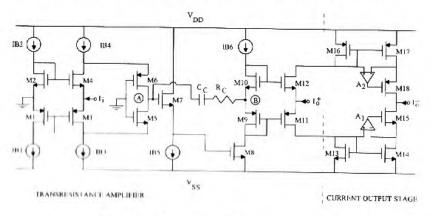

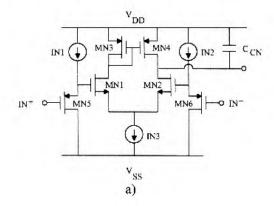

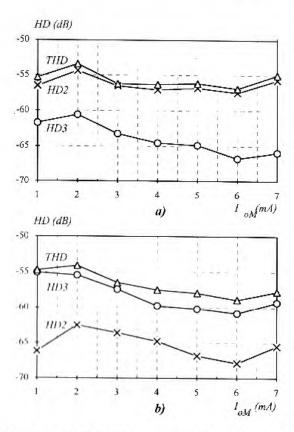

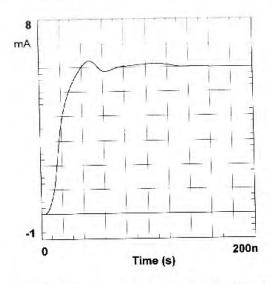

#### 3.2.3 COS Based On Cascoded Mirrors With 116 Improved Dynamic Matching 3.2.4 COS based on Active-Gain Enhanced Cascoded Mirrors 3.2.5 Simulation Results 119 3.3 HARMONIC DISTORTION DUE TO MISMATCHES 121 3.3.1 Threshold Voltage Mismatches 121 3.3.2 Transconductance Parameter Mismatches 124 3.4 DESIGN EXAMPLES 125 3.4.1 A VFCOA Configuration 125 3.4.2 COA Configurations 136 3.5 A VERSATILE FULLY DIFFERENTIAL COA 146 3.6 MEASUREMENT STRATEGIES 150 APPENDIX 3.A Harmonic Distortion in class AB COSs. 153 APPENDIX 3.B Accurate Determination of HD, 155 REFERENCES 157 Index 159

#### ACKNOWLEDGEMENTS

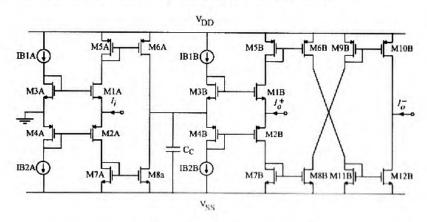

CMOS Current Amplifiers was originally the title of a Doctoral thesis by S. Pennisi with G. Palmisano as supervisor. The thesis dealt mainly with high-drive CMOS current amplifiers for off-chip loads.

This book is an extended version of the thesis. It includes new topics such as Current Comparators and Conveyors, and several published works of the authors in the field of current-mode techniques. In addition, state-of-the-art achievements have been detailed by carefully considering significant contributions from other researchers. Therefore, we would like to thank the many authors who with their original ideas have produced many of the meaningful results in this field.

We would like to acknowledge the CNR (Italian National Research Council) and MURST (Ministero dell'Università e della Ricerca Scientifica e Tecnologica) for providing part of our funding.

We are grateful to EUROPRACTICE and AMS for software CAD support and technology facilities.

A special thanks is due to Prof. Bruun, for our useful exchange of information with him.

Finally, we would like to thank our friend Dr. Papalia, for his precious contribution in revising the style and syntax of the text.

Giuseppe Palmisano Gaetano Palumbo Salvatore Pennisi

# ABBREVIATIONS

| A/D    | Analog-to-Digital Converter                    |

|--------|------------------------------------------------|

| BJT    | Bipolar Junction Transistor                    |

| CCCS   | Current-Controlled Current-Source              |

| CCII   | Second Generation Current Conveyor             |

| CCVS   | Current-Controlled Voltage-Source              |

| CFOA   | Current-Feedback Voltage Operational Amplifier |

| CMRR   | Common-Mode Rejection Ratio                    |

| COA    | Current Operational Amplifier                  |

| COS    | Current Output Stage                           |

| D/A    | Digital-to-Analog Converter                    |

| DUT    | Device Under Test                              |

| GBW    | Gain-Bandwidth Product                         |

| IC     | Integrated Circuit                             |

| MOS    | Metal Oxide Semiconductor                      |

| Op-Amp | Operational Amplifier                          |

| OTA    | Operational Transconductance Amplifier         |

| PSRR   | Power Supply Rejection Ratio                   |

| SR     | Slew Rate                                      |

| TCOA   | Transconductance Operational Amplifier         |

| THD    | Total Harmonic Distortion                      |

| TROA   | Transresistance Operational Amplifier          |

| VCCS   | Voltage-Controlled Current-Source              |

| VCVS   | Voltage-Controlled Voltage-Source              |

| VFCOA  | Voltage-Feedback Current Operational Amplifier |

| VOA    | Voltage Operational Amplifier                  |

|        |                                                |

#### PREFACE

Over the last few years current-mode signal processing has been extensively investigated. Works have been published demonstrating that state-of-the-art current-mode analog design can provide solutions to many circuit and system problems. In this field, current mirrors have been the natural choice for use as elementary building blocks, since they allow simple and elegant open-loop circuits to be designed with low cost processes. On the other hand, the approaching maturity of current-mode techniques and increasing demands on performance have lead to high-gain current-input current-output circuits for use in accurate closed-loop configurations. As can be expected from amplifiers exploiting current-mode techniques, performance in terms of low voltage, slew rate and bandwidth can in principle be maximized.

Furthermore, there is also need for power stages capable of delivering high bipolar currents (several milliamperes) into off-chip loads. To this end, the high-drive current amplifier becomes the natural front-end block for current-mode IC's.

The book presents design strategies for high performance current amplifiers based on the CMOS technology, preferred for VLSI analog processing. After an introduction on various architectures of operational amplifiers, the operating principles of the current amplifier are outlined. The main focus will be to provide the reader with simple and compact design equations for use in a pencil and paper design and the following simulation step. More complex analytical derivations will be introduced only for the evaluation of fundamental non-idealities due to second order effects. Therefore, the length of the book is self-contained and presentation is kept to a reasonably accessible level. The book was written to be used by postgraduate students who are already familiar with voltage operational amplifiers and who want to extend their knowledge to current amplifiers. Moreover, it is a valid reference for analog IC designers who desire to implement this unconventional amplifier and to better comprehend its practical applications and limitations. The outline of the text is as follows:

Chapter 1 introduces the general aspects of Current Amplifiers. After a preliminary classification of operational amplifiers, ideal blocks and models are discussed for different architectures and a first high-level comparison between traditional amplifiers and current amplifiers is made. Analysis and examples of basic circuits as well as signal processing applications involving current amplifiers are also given. Non-idealities and second-order effects causing limitations in performance are then discussed and evaluated.

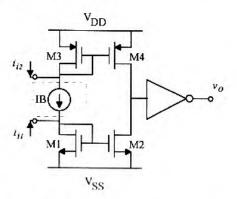

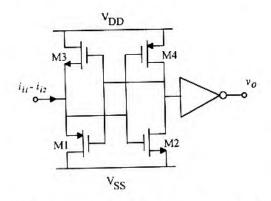

Chapter 2 focuses on low-drive Current Amplifiers. Several design examples for Current Conveyors and class A Current Amplifiers are discussed in detail and design equations are presented for the main performance parameters which allow a good trade-off between requirements. Moreover, high-performance solutions for high bandwidth and low voltage capability are also considered. Finally, Current Comparators with progressively enhanced performance are reported and analyzed critically.

Chapter 3 deals with current amplifiers for off-chip loads. Several class AB current-mode output stages are discussed and design strategies which improve performance are presented. A detailed analysis of non-ideal effects is carried out with particular emphasis on linearity. Design examples are given and circuit arrangements for further developments are included. Experimental measurements are finally reported.

# Chapter 1

# **OPERATIONAL AMPLIFIERS**

Amplifiers with high open-loop gain, most commonly termed Operational Amplifiers (op-amps) [1]-[4], are unquestionably the most useful and flexible building blocks in analog signal processing. Indeed, the use of these devices in a negative feedback loop allows a large variety of transfer functions to be simply implemented, and whose properties and accuracy are essentially independent of the large but inaccurate open-loop usin of the op-amp.

Traditionally, signal processing has been restricted to voltage-mode operations only. As a result, the voltage op-amp (VOA) has been the dominant architecture used by analog designers and the most commercially available from IC manufacturers.

However, in recent years the so called current-mode approach [5]-[8] has attracted ever more attention. Circuits are classified as current-mode if the information medium is represented by time-varying currents. This approach is particularly useful in the IC environment which is predominantly capacitive. Under this condition, speed is maximized by driving currents rather than by voltages. Moreover, low-voltage operations can be associated with current-mode circuits since voltage swings are minimized, while the signal range depends on the impedance level chosen by the designer and is no longer directly restricted by the supply voltage.

In effect, the last decade has been characterized by an increasing number of current-mode applications both in the digital and analog area. For example, current-mode has been profitably employed in high-speed circuits including current-mode logic [9]-[16] current-mode D/A and A/D converters [17]-[27] as well as in linear [28]-[40] and log-domain [41]-[51] filter applications, and in translinear circuits [52]-[58].

In this context, amplifier architectures with current-input current-output capability represent useful building blocks that can play the same role as VOAs do in traditional voltage-mode applications.

In this chapter, after a brief introduction on ideal amplifiers, their models and basic theory, we will review practical amplifier architectures and their high-level behavior. The voltage op-amp, transconductance op-amp and current-feedback op-amp will be discussed together with their favorable features and principal limitations. Then, reported techniques to provide conventional voltage amplifiers with current capability will be reviewed and applications of current amplifiers to signal processing will be also treated. Finally, the internal architecture of true current-mode amplifiers and their main performance parameters will be introduced.

# 1.1 THE OPERATIONAL AMPLIFIER SET

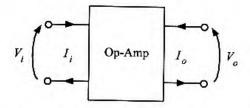

The concept of an ideal operational amplifier was first introduced by Tellegen in 1954 [59]. According to this definition an ideal op-amp is a two-port device with four associated variables,  $V_i$ - $I_i$  and  $V_o$ - $I_o$  at the input and output port, respectively, which exhibits an infinite power gain between the two ports. This means the input variables are both zero whereas the output ones are arbitrary. The input port is consequently said to exhibit a virtual short-circuit. Indeed, the input terminals have the same voltage and no current flows through them. The block diagram of an ideal op-amp is shown in Fig. 1.1.

Fig. 1.1. Block diagram of an ideal op-amp

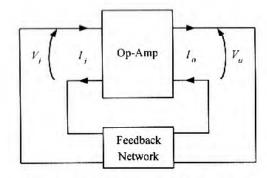

The transfer properties of this device only become well-defined if an external network allows feedback from the output to the input port, as depicted in Fig. 1.2.

Fig. 1.2. Amplifier with feedback network

In practice, an op-amp belongs to one of the four types listed below:

- voltage op-amp (VOA): a voltage controlled voltage source (VCVS) with both infinite voltage gain and input resistance, and zero output resistance

- current op-amp (COA): a current controlled current source (CCCS)

with both infinite current gain and output resistance, and zero input

resistance

- transresistance op-amp (TROA): a current controlled voltage source (CCVS) with infinite transresistance gain, and both zero input and output resistances

- transconductance op-amp (TCOA): a voltage controlled current source (VCCS) with either infinite transconductance gain, input and output resistances

Of course, ideal performance in terms of bandwidth, linearity, input and output swing, etc., are also requirements for any kind of ideal op-amp.

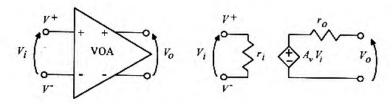

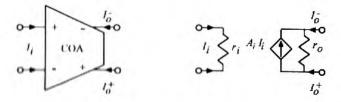

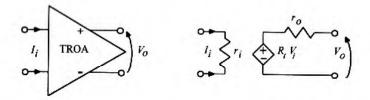

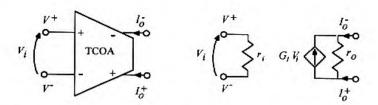

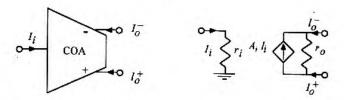

The block diagram and the small-signal equivalent circuit for each of these devices are reported in Fig. 1.3. Input  $(r_i)$  and output  $(r_o)$  resistances are also included. Table 1.1 summarizes the characteristics of the four ideal op-amps which exhibit an infinite power gain between the input and output ports.

It is self-evident that the four devices can be arranged into two dual pairs. The VOA and the COA form one pair, while TROA and TCOA constitute the other pair (this is the particular case of application of the coljoint networks theorem, briefly described in section 1.5). Indeed, from Table 1.1, it is clear that the former pair has an input resistance which is reciprocal to the output resistance and that the gain is the ratio of the same

kind of variable, while the second pair has equal input and output resistances and the gain is a ratio of different variables.

Fig. 1.3a. Voltage op-amp symbol and equivalent circuit

Fig. 1.3b. Current op-amp symbol and equivalent circuit

Fig. 1.3c. Transresistance op-amp symbol and equivalent circuit

Fig. 1.3d. Transconductance op-amp symbol and equivalent circuit

Table 1.1.

Ideal op-amps and their characteristics

| Op-amp type | $r_i$ | ro | Open-loop gain      |

|-------------|-------|----|---------------------|

| VOA         | 00    | 0  | $A_{v}=V_{O}/V_{i}$ |

| COA         | 0     | œ  | $A_i = I_O/I_i$     |

| TROA        | 0     | 0  | $R_t = V_O / I_i$   |

| TCOA        | ∞     | œ  | $G_t = I_O/V_i$     |

Amplification and signal conversion (i.e., voltage to current and current to voltage conversion) are the most frequently encountered functions in analog signal processing. These functions can be implemented with a feedback op-amp by a suitable choice of the external feedback network.

There are four possible types of closed-loop amplifiers which differ in the combinations of input source and output drive

- voltage to voltage (V-V) amplifier

- · current to current (I-I) amplifier

- · voltage to current (V-I) amplifier

- current to voltage (I-V) amplifier

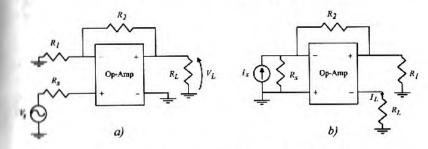

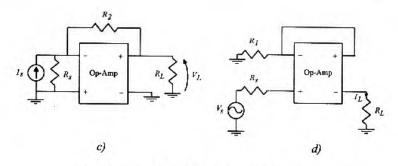

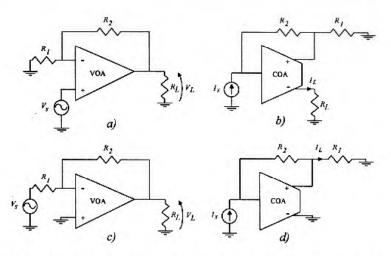

The closed-loop configurations for each kind of amplifier are illustrated in Fig. 1.4, where the symbol of the ideal op-amp was used.

Fig. 1.4. Feedback amplifiers: a) V-V; b) I-I

Fig. 1.4. Feedback amplifiers: c) I-V; d) V-I

Table 1.2 summarizes the transfer functions which result for each kind of feedback amplifier.

Table 1.2.

Transfer functions of amplifiers in Fig. 1.4

| V-V            | 1-1           | I-V   | V-I              |

|----------------|---------------|-------|------------------|

| $+R_{2}/R_{1}$ | $1 + R_2/R_1$ | $R_2$ | 1/R <sub>1</sub> |

It can be observed that the above transfer functions only depend on the values of  $R_1$  and/or  $R_2$  regardless of the source and load resistances. This is a desirable feature which closely approximates the performance of an ideal amplifier, since it reduces interaction between cascaded active circuits and improves control over the loop gain frequency response (module and phase). This feature greatly simplifies design from the system to circuit point of view.

At this point one may be tempted to conclude that any of the four opamps might alternatively be used to implement the four types of feedback amplifiers. However, this is not the case if we consider non-ideal op-amps with finite (albeit large) open-loop gain, even with ideal internal resistances. In fact, under these assumptions, most of the 16 closed-loop configurations, obtained by replacing the ideal op-amp with one of the four specified opamps in Fig. 1.3, will exhibit a loop gain which is dependent on the source and/or load resistances.

Since the closed-loop gain and bandwidth are strictly related to the loop gain (this important aspect of closed-loop systems will again be briefly reviewed in section 1.3), they will also depend on the source and/or load resistances. More specifically, this detrimental condition characterizes all

the configurations in which the op-amp is a different type to the feedback amplifier [60], [61].

We will give two examples to illustrate this concept. Firstly, we will analyze the loop gain of a I-I feedback amplifier implemented using a VOA and then the loop gain of the same I-I amplifier made using a COA.

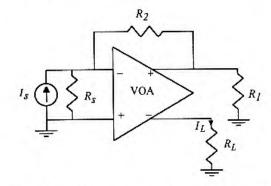

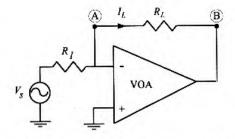

Let us consider the circuit in Fig. 1.5a where the ideal op-amp of Fig. 1.4b is replaced by a VOA.

Fig. 1.5a. VOA employed to realize a I-I amplifier

Fig. 1.5b. Equivalent circuit for the loop-gain computation of a I-I amplifier realized with a VOA

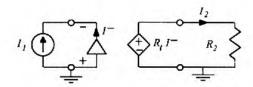

We consider the equivalent circuit in Fig 1.5b (obtained by breaking the loop at the inverting input of the VOA) to evaluate the loop gain, T, which is given by

$$T = -\frac{V_2}{V_1} = A_v \frac{R_1 R_s}{(R_1 + R_L)(R_2 + R_s) + R_1 R_L}$$

(1.1)

The reader can verify this result directly by inspection. The loop gain clearly depends on both source and load resistances.

Let us now consider the implementation of the same I-I amplifier in a more "natural" mode, i.e. by using a COA. In this case the loop gain can be computed by considering the equivalent circuit in Fig. 1.6.

Fig. 1.6. Equivalent circuit for the loop-gain computation of a I-l amplifier realized with a COA.

In this case the loop-gain is totally free from source or load effects, as (1.2) shows

$$T = -\frac{I_2}{I_1} = A_i \frac{R_1}{R_1 + R_2} \tag{1.2}$$

To preserve simplicity, the above analysis has been restricted to op-amps with finite gain but with ideal input-output resistances. However, it can also be demonstrated that the considerations developed above remain valid with real input-output resistances as well.

To conclude, we can say that the best performance is obtained by following "natural laws" and that the use of a VOA is not the prime choice in implementing current-mode transfer functions. This perhaps represents the principal motivation that lead researchers to design more appropriate opamp architectures which could be profitably used in current-mode signal processing.

## 1.2 OP-AMP CONFIGURATIONS

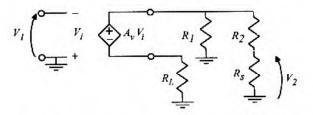

In the previous section we dealt with the four types of ideal op-amps which satisfy the general definition. Moreover, we also showed that, in real cases, each one performs better if used in its natural way (i.e., a VOA to implement a V-V amplifier, a TROA to implement a I-V amplifier, etc.). Nevertheless, given the wide diffusion of voltage signal processing, the VOA has until recently been the dominant architecture for analog designers and the one most commonly available from IC manufacturers. This ubiquitous device mainly bases its popularity on the number of attractive features which it allows. In fact, the differential pair input stage is well suited to rejecting common-mode signals. Moreover, a VOA only requires a single-ended output to provide negative feedback and output drive papability at the same time as shown in Figs. 1.4a and 1.4c. In these figures one of the two output terminals is grounded in both voltage-output applications. Of course, implementing a fully differential output stage is more difficult than designing a single-ended output stage. Figure 1.7 shows the internal architecture of a typical single-ended VOA. It is made up of a transconductance input stage (usually implemented with a differential pair), a second stage to enhance the overall amplifier gain and an output stage (usually implemented with a Class AB voltage follower) to isolate the opamp output from the load.

Fig. 1.7. Typical architecture of a single-ended VOA

Resistance  $r_{eq}$  is the equivalent output resistance of the input stage and  $C_C$  is the compensation espacitor Generally, Miller compensation is

adopted because it leads to a small capacitance and provides the well-known pole splitting [62], [63].

For the circuit in Fig. 1.7 the DC open-loop gain and the pole frequency are

$$A_{\nu} = G_{m} r_{eq} A_{\nu 2} \tag{1.3}$$

$$\omega_o = \frac{1}{r_{eq} A_{v2} C_C} \tag{1.4}$$

However, it is well known that the performance of a VOA is limited by a fixed gain-bandwidth product and by an internal slew-rate whose maximum value is determined by the ratio of a quiescent current to the compensation capacitance.

In the last two decades, emerging MOS technologies (initially NMOS and now almost exclusively CMOS) have lead to the development of transconductance operational amplifiers (commonly termed OTAs) principally for use in fully-integrated filtering. These amplifiers are integrated versions of what we referred to as TCOA in section 1.1. Since OTAs are used in voltage-mode applications, with the exception of fully differential circuits, their design can be simplified to provide a single ended output.

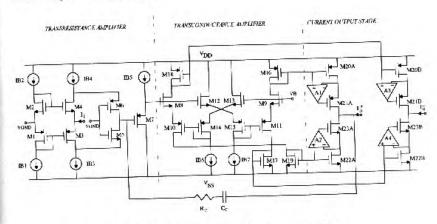

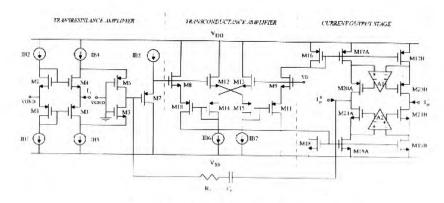

VOA and OTA architectures are strongly related since an OTA can be considered a VOA without the final buffer stage. Indeed, an output stage can be avoided in those applications where the load is a small capacitance requiring only low current levels. Moreover, a capacitive load leaves the DC loop gain unchanged only affecting its phase. The use of CMOS technology has developed continuously because of its ability to support high quality analog and digital circuitry, leading to the design of high-performance opamps for off-chip loads. Due to their reduced drive capability compared to BJT technologies, CMOS power amplifiers have been even better implemented in transconductance output stages (i.e., common source output stages instead of voltage follower stages) [64]-[67]. In these applications the main goals are drive capability and power conversion efficiency. To this end, the output stage has to provide a large input and output swing but without requiring a voltage gain. Usually, it behaves like a low-gain inverting amplifier.

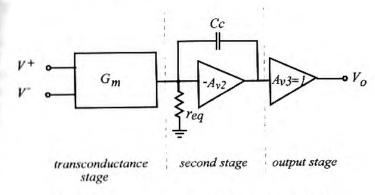

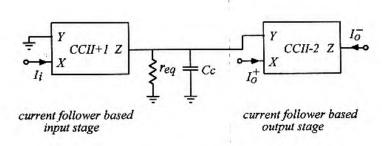

More recently, we have witnessed the affirmation of a novel op-amp architecture now available from several of the specialist analogue semiconductor manufactures. These op-amps are generally referred to as Current-Feedback Operational Amplifiers (CFOAs) [2], [7] and [68]-[70], and represent an evolution in the architecture of the voltage-mode op-amps, which have otherwise remained much the same over the years. Figure 1.8 shows the CFOA symbol and equivalent circuit. Like almost all current-mode circuits, a CFOA can be conveniently described in terms of the well-known Second Generation Current Conveyor (CCII) which essentially somists of two coupled voltage and current unitary buffers (readers who are not familiar with this building block, can refer to the next chapter for a brief introduction).

Fig 1.8. CFOA symbol and equivalent circuit

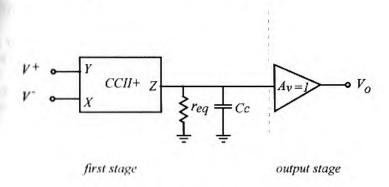

In Fig. 1.9 the typical architecture of a CFOA is illustrated. It is made up of a CCII-based input stage (that performs a voltage following action between terminal Y to X and a current following action between X and Z), and an output stage with the classical buffering function.

Fig.1.9. Typical architecture of a CFOA

By applying a current signal to the (low impedance) inverting input terminal, the DC open-loop transresistance gain can be found

$$R_t = r_{eq} (1.5)$$

The dominant-pole frequency is

$$\omega_o = \frac{1}{r_{eq}C_C} \tag{1.6}$$

Implementations of high-performance CFOAs have become possible thanks to the availability of high quality complementary bipolar transistors provided by advanced BJT processes. Here, the traditional differential pair input stage has been abandoned for a complementary common emitter/common base stage. This non-conventional input stage allows a nominally unlimited slew rate to be achieved thus yielding a large signal response which is superior to that of most voltage op-amps. Moreover, this device provides the well-known constant bandwidth versus variable closed-loop gain property.

These features have led to conventional voltage op-amps being replaced with CFOAs in some high speed applications. However, these op-amps are affected by some drawbacks. First, the input voltage follower works outside the feedback loop and can be a heavy source of distortion especially in unity-gain configurations with high signal levels. Secondly, CFOAs exhibit high input offsets and low common-mode rejection. Partially because of these limitations and given the inherent low transconductance of MOS transistors, only few CFOAs have been presented up to now in CMOS technology.

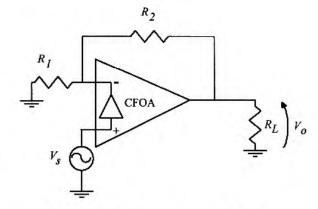

We can simply illustrate the constant-bandwidth property offered by a CFOA by considering the closed-loop configuration shown in Fig. 1.10. The loop gain can be found by shorting the input source and breaking the loop at the inverting input. The equivalent circuit obtained by updating the equivalent resistance levels is shown in Fig. 1.11 (where ideal input and output CFOA resistances are considered).

The loop gain is given by

$$T_o = -\frac{I_2}{I_1} = \frac{R_t}{R_2} \tag{1.7}$$

which shows that the loop gain depends on the transresistance gain,  $R_I$ , and  $R_I$ . Since the closed-loop bandwidth is proportional to the loop gain, and the closed-loop gain can be set by changing only  $R_I$ , a constant bandwidth behavior is achieved.

Fig.1.10. Feedback configuration of a CFOA

Fig. 1.11. Equivalent circuit for the loop-gain computation of the circuit in Fig. 1.10

#### 15

#### 1.3 THE GAIN BANDWIDTH TRADE-OFF

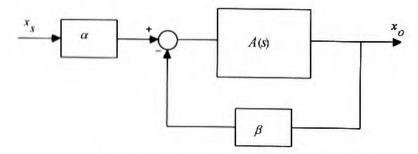

The constant bandwidth property exhibited by the CFOA can easily be explained and generalized using the traditional block diagram for a feedback system shown in Fig. 1.12. We have chosen not use this representation in the future because it is difficult to take into account the loading effects of the feedback network on the basic amplifier. However, this approach is quite suitable from a high-level point of view and helps to get a simple focus on the argument [61].

A(s) represents the open-loop gain of the amplifier,  $\alpha$  is the input attenuation and  $\beta$  the attenuation introduced by the feedback network. A(s) can be one of those listed in the last column of Table 1.1, depending on the type of op-amp chosen.

Fig. 1.12. Block diagram of a feedback system

From this diagram we find the expressions of the loop gain, T(s), and the closed-loop gain,  $A_{CI}(s)$

$$T(s) = \beta A(s) \tag{1.8}$$

$$A_{cl}(s) = \frac{x_o}{x_s} = \frac{\alpha A(s)}{1 + T(s)} \tag{1.9}$$

It can be observed that the loop gain is dimensionless in all possible cases. Moreover, if T(0) is much greater than 1, the DC closed-loop gain can be approximated to

$$A_{cl}(0) = \frac{\alpha}{\mu} \tag{1.10}$$

Assuming that the op-amp is characterized by a single dominant pole its open-loop gain can be expressed as

$$A(s) = A_o \frac{1}{1 + s / \omega_o} \tag{1.11}$$

where  $\omega_o$  is the angular frequency of the dominant pole and  $A_o$  is the DC main.

Substituting (1.11) in (1.9) we obtain the expressions for the closed-loop amplifier bandwidth,  $\omega_{cl}$ , and gain-bandwidth product, GBW,

$$\omega_{cl} = \omega_o [1 + T(0)] \tag{1.12}$$

$$GBW = \frac{|\alpha|A_o}{1+T(0)}\omega_o[1+T(0)] = |\alpha|A_o\omega_o$$

(1.13)

The above equations hold for any feedback system. Provided that parameter  $\alpha$  is constant, (1.13) asserts the well-known property of GBW to be independent of the closed-loop gain (i.e., from  $\beta$ ). Note that GBW has the frequency dimension for the VOA and COA only. For the TROA it has the dimension of the reciprocal of a capacitance, and for the TCOA it has the dimension of the reciprocal of an inductance.

Furthermore, combining (1.8) and (1.12) we see that the closed-loop bandwidth is approximately given by  $\beta A_o \omega_o$ . Therefore, by leaving parameter  $\beta$  (and hence the closed-loop bandwidth) constant, one can change the closed-loop gain simply by changing parameter  $\alpha$ , as according to (1.10). This is exactly what happens in a CFOA. On the contrary, in some applications with VOAs (e.g., a non-inverting configuration where  $\alpha$  is unitary) the closed-loop gain is set by changing  $\beta$  and, hence, the loop gain and the closed-loop bandwidth.

In [60] it was shown that all the four types of op-amps used in their natural mode (i.e. to implement the same type of feedback amplifier) are characterized by  $\alpha$  equal to 1 and consequently, exhibit constant gain-bandwidth properties. For example, we can return to (1.2), expressing the loop-gain of the 1-1 feedback amplifier performed by a COA. We can rewrite (1.2) in terms of the closed-loop gain  $A_{cl}$

$$T = A_i \frac{R_1}{R_1 + R_2} = \frac{A_i}{A_{cl}} \tag{1.14}$$

By comparing (1.8) and (1.14) we get  $\beta = 1/A_{cl}$ , and from (1.10)  $\alpha = 1$  results. Hence, any increase in the closed-loop gain leads to a decrease in the closed-loop bandwidth. The same results and considerations can be extended to the so-called constant gain-bandwidth product configurations.

Moreover, the same authors demonstrated that achieving constant bandwidth properties depends on the possibility to isolate the op-amp input and output from the source and load resistances, respectively, by using ideal current or voltage unity-gain buffers. For instance, the CFOA can be recognized as the result of applying a voltage buffer to a single-ended transresistance amplifier. A further example can be given if we return to (1.1) that expresses the loop-gain of a I-I feedback amplifier performed by a VOA. We can see that adopting two ideal current followers at the input and the output of the amplifier, is equivalent to setting resistance  $R_s$  to infinity and  $R_L$  to zero. Under these assumptions loop gain becomes

$$T(s) = A_{\nu}(s) \tag{1.15}$$

The above relation indicates that parameter  $\beta$  is equal to 1. Therefore, this particular configuration will achieve the maximum closed-loop bandwidth, i.e. the GBW, regardless of the value of closed-loop gain, source and load resistances. This is a very attractive solution which, however, is not real. Indeed, it is no trivial task to design high-performance followers, with approaching ideal input-output resistances and a bandwidth performance which is well beyond that of the final amplifier. Actually, when considering the fundamental process limitations which set the ultimate performance for both unity-gain buffers and op-amps, we see that constant gain-bandwidth product configurations provide higher loop gain than constant bandwidth configurations, as discussed in [71]. This means that, in practical cases, the constant bandwidth property is obtained at the expense of reduced loop gain.

The brief discussion given here reveals that today there is great interest in the op-amp area due to the demand for ever better performance. In addition, advances in process technologies have made possible the integration of novel architectures for use in special applications. However, for the remainder of this book we shall concentrate only on the realization of current operational amplifier architectures, i.e. op amps with well-defined

input and output current-capabilities. We shall start by giving a historical background.

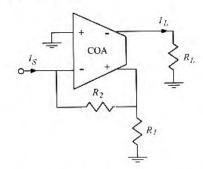

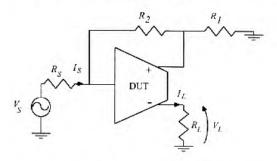

# 1.4 CURRENT AMPLIFIERS USING VOLTAGE OP-AMPS

The need for amplifiers with a well-defined bipolar current output was recognized even when the current-mode approach was in its infancy. In the time when no fully integrated version of current amplifiers was available, the only alternative for system designers was to use a voltage amplifier. neveral voltage-to-current amplifier designs employing the VOA have been reported in literature from the late 1970s to the end of the 1980s. The very first attempts sought to provide only a single current output facility using a VOA. The most common way to do this, as frequently encountered in textbooks [1], is to place the load in the feedback loop of the VOA as shown in Fig. 1.13. This circuit provides a very low input resistance (at the inverting terminal). The current flowing through  $R_L$  is set to  $V_s/R_l$ regardless of the R<sub>L</sub> value. Therefore, the circuit can be seen as a current generator between terminals A and B. Indeed, the equivalent resistance seen at these terminals is equal to  $(r_i / R_1)(1 + A_v)$ , where  $r_i$  and  $A_v$  are the VOA input resistance and voltage gain, respectively. However, in this solution the load cannot be referred to ground, despite this being a general requirement.

Fig. 1.13. Feedback voltage-to-current amplifier

To solve this problem Howland [1] proposed the circuit shown in Fig. 1,14.

Fig. 1.14. Howland voltage-to-current converter

The current-converter will drive the grounded load with a current  $I_L = V_x / R_3$  if the balancing condition  $R_4 / R_3 = R_2 / R_1$  is satisfied. In addition, thanks to the combination of positive and negative feedback, the circuit exhibits a nominal infinite output resistance. Unfortunately, the positive feedback action means the circuit requires very accurate resistor matching. Indeed, even a small deviation from the ideal balancing condition could make the output resistance negative and cause instability.

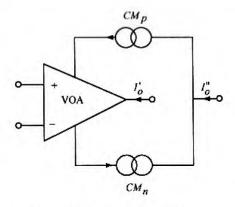

To extend the output capability of conventional VOAs, the most successful technique was using supply current sensing, first introduced by Graeme [72] in 1974 and further refined by Rao and Haslett [73]. The approach exploits the property that the sum of the currents flowing in the VOA supply leads equals the output current, so long as the signal currents in other connections to ground are negligible. In most VOAs this condition is met and a couple of complementary current mirrors can be employed to recombine the two supply currents. The current mirrors provide a single high impedance bipolar output, as shown in Fig. 1.15. Huijsing coined the term Operational Mirrored Amplifier to indicate this circuit [74]. Of course, for proper current-converter operation the structure has to be configured in unity-gain closed-loop (i.e., by shorting the VOA output and inverting input). Under this arrangement the circuit can be used in a number of applications since it realizes the versatile CCII, as will be shown later.

Fig. 1.15. Operational mirrored amplifier

Moreover, by including a resistive feedback network, an accurate current pain is achieved, as illustrated in Fig. 1.16. It is given by

$$\frac{I_L}{I_A} = -\left(1 + \frac{R_2}{R_1}\right) \tag{1.16}$$

Fig. 1.16. Operational mirrored amplifier arranged to provide a current gain

The supply-sensing technique was also generalized by Toumazou et al. [6] who propose that a multi-terminal VOA be implemented leaving the drains (collectors) of the output stage externally accessible. In this manner, output-current sensing rather than whole supply-current is enabled.

G. Palmisano - G. Palumbo - S. Pennisi

Current-sensing techniques have been experimentally tested with a number of well-documented applications. Despite the use of discrete components, these circuits generally provide high bandwidth and slew rate capabilities. However, the critical parameter in these applications is linearity because it depends upon the current transfer properties of the current mirrors which are connected in open loop at the circuit output. This drawback is common to almost all class AB solutions and, due to its importance, it will be dealt with in detail in chapter 3.

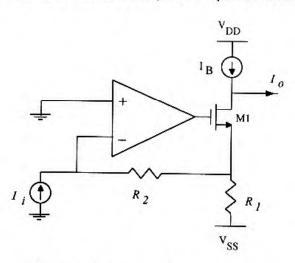

We conclude this review with the simple and well-known class A current amplifier shown in Fig. 1.17. In this circuit transistor M1 and current generator  $I_R$  make up the current output stage. Apart from the sign, it is easy to find that the amplifier gain is given again by (1.16). This circuit exhibits high accuracy and linearity, but it has a very low power conversion efficiency, since the current output stage works in a class A fashion. Moreover, it could be difficult to match current IR with the quiescent current in M1, since they are affected by different process tolerances.

Fig. 1.17. Simple class A current amplifier

On the basis of what we discussed in section 1.2, the application of supply current sensing to VOAs can be recognized in the use of a current

follower in the VOA output. This explains why these architectures were (sometimes surprisingly) discovered as having constant bandwidth properties. However, all these kinds of op-amp structures represent only a partial step towards the implementation of a true current-mode op-amp. In reality, the ideal COA defined in section 1.1 requires a zero open-loop input resistance and a differential current output capability, features which are not provided by the circuits discussed above.

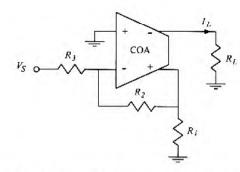

## 1.5 SIGNAL PROCESSING WITH CURRENT OP-AMPS

As already mentioned, a dual relationship exists between voltage-mode and current-mode circuits. This means that almost all transfer functions implemented with active networks based on voltage op-amps can alternatively be implemented with current op-amps. Voltage-mode circuits can readily be transformed into current-mode circuits by using the principle of adjoint networks [75]-[76], that we shall briefly describe in the following.

# The adjoint networks principle

Consider an arbitrary linear network consisting of passive elements (resistors, capacitors and inductors) and controlled sources. Moreover, assume that the network is driven by an Independent voltage source and that the output variable is a specific voltage. By replacing each element of the network with its adjoint (or dual), the adjoint network is found, according to the following rules. The adjoint of a passive element is itself (i.e., resistors, capacitors and inductors remain unchanged). The adjoint of a voltage source is a short circuit (and viceversa). Similarly, a current source turns into a open circuit (and viceversa).

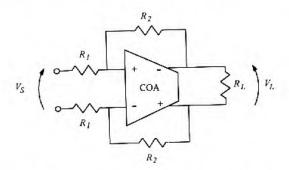

Figure 1.18 illustrates the adjoint network principle applied to the wellknown non-inverting and inverting closed-loop VOA configurations.

Fig.1.18. Non-inverting, a) and b), and inverting, c) and d), feedback configurations using VOAs and COAs

It is easy to verify that the closed-loop gain for the upper and lower circuits in Fig. 1.18 are respectively

$$A_{cl} = 1 + \frac{R_2}{R_1} \tag{1.17a}$$

$$A_{cl} = -\frac{R_2}{R_1} \tag{1.17b}$$

The current amplifiers in Fig. 1.18 possess the interesting feature which is the possibility of using non-linear resistances in the feedback network. In fact, since the voltage drop across  $R_I$  and  $R_2$  is the same, non-linearities are compensated for [77]. Arbel first reported this property and described a COA employing a transistorized feedback network. To achieve a gain of n+1 in the non-inverting configuration, resistances  $R_I$  and  $R_2$  are implemented with a single and a parallel of n triode-biased transistors, respectively.

The properties of an adjoint network can be inferred from the properties of the original network, without requiring any further analysis. For instance, the popular voltage-mode RC-active circuits can be transformed into their current-mode counterparts using the COA. The adjoint circuits have

identical sensitivities and, hence, design rules and optimization strategies, developed for voltage-mode circuits, can be used directly.

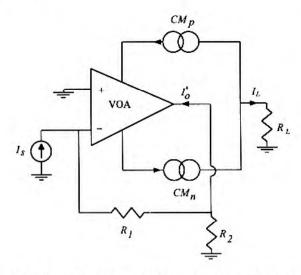

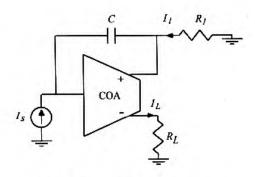

An example of a current-mode integrator is given in Fig. 1.19. Two transfer functions are obtained by considering output currents  $I_I$  or  $I_L$

$$\frac{I_1}{I_s} = \frac{1}{sR_1C} \tag{1.18a}$$

$$\frac{I_L}{I_s} = \frac{1 + sR_1C}{sR_1C} \tag{1.18b}$$

Fig. 1.19. Current-mode integrator

#### 1.6 TOWARDS A TRUE COA

We have already introduced the ideal current op-amp in section 1.1 and recognized that, according to the adjoint network theorem, it can be represented as the dual of an ideal VOA. The theorem can be also exploited to obtain one possible COA internal architecture from that of a VOA. To this end, we noted that the design of a VOA can be considerably simplified if a single output device is considered. In fact, a single ended VOA is able to drive the load and the feedback network simultaneously. With this observation in mind it is easy to understand that a similar condition would also hold for the input port of a COA. Indeed, a COA only needs one input terminal to be connected to the input source and to the feedback network. This aspect of a current amplifier can be further exemplified by returning to Figs 1.4 b and c working as amplifiers with input current capability. It can be seen that in such applications one op-amp input terminal is always grounded, this is due to the general rule that summing or subtracting

currents only requires one single node. The symbol and the circuit model of a single-input COA are reported in Fig. 1.20.

Fig 1.20. Single-input current op-amp symbol and equivalent circuit

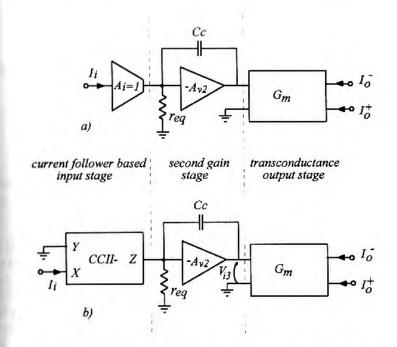

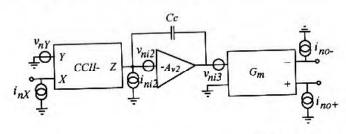

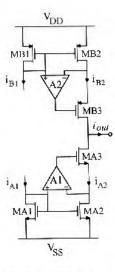

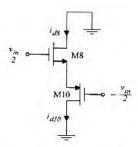

Finally, we can apply the adjoint theorem to the VOA internal architecture, shown in Fig. 1.7, and obtain a block model of the COA as depicted in Fig. 1.21. The output voltage buffer of the VOA turns into a input current buffer. The current buffer can be also realized by using a CCII- with a grounded Y terminal. The differential input stage turns into a differential transconductance output stage. The second gain-stage can remain the same. The current gain and bandwidth of this circuit are exactly the same as the voltage gain and bandwidth of the VOA

$$A_i = A_{v2}G_m r_{eq} \tag{1.19}$$

$$\omega_o = \frac{1}{r_{eq} A_{v2} C_c} \tag{1.20}$$

where  $r_{eq}$  and  $C_C$  are the equivalent resistance at terminal Z of the CCIIand the Miller compensation capacitor, respectively. Note that the second stage, used to increase gain, is not necessary for the implementation of a current amplifier, although it allows Miller compensation to be profitably achieved. The input current buffer (possibly together with the second stage) can be also regarded as a transresistance amplifier. In fact, it accepts a low input current and provides a high output voltage.

It is curious to note that, the very first proposals of high-current-gain amplifiers [78-79] adopted differential-input devices. However, as it turned out, this was an unnecessary condition revealing how strong the voltage opamp heritage and the voltage-mode way of thinking was.

Fig. 1.21. COA internal architecture a) with current buffer; b) with CCII

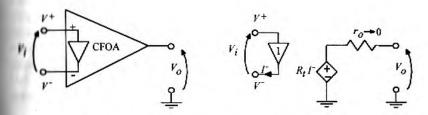

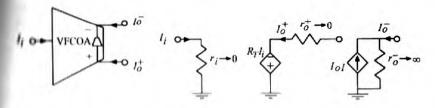

The COA is the dual counterpart of a VOA and therefore will exhibit constant gain-bandwidth property when used in closed-loop configurations. In order to obtain a structure with constant bandwidth property, the adjoint network theorem can be applied to a CFOA as well. If we convert the squivalent circuit and block diagram of a CFOA (already depicted in Figs. 1.11 and 1.9) to current-mode we obtain a novel structure which we term the Voltage-feedback Current Operational Amplifier (VFCOA). Figures 1.22 and 1.23 report the symbol, equivalent circuit and block diagram of a VFCOA.

Fig 1.22. Voltage feedback current op amp symbol and equivalent circuit

26

Fig. 1.23. VFCOA internal architecture

The first stage in Fig. 1.23 is the same as in a COA. The output stage is a current follower which is the dual of the input voltage follower of a CFOA. Of course, given duality the DC transresistance gain and bandwidth are the same as in a CFOA so that (1.5) and (1.6) still hold.

A final consideration is that the circuit can be regarded as the result of applying a current follower to the output of a transresistance op-amp. Consequently, the constant bandwidth versus variable gain property is explained on the basis of what was discussed in section 1.3.

# 1.7 PERFORMANCE PARAMETERS OF CURRENT AMPLIFIERS

In the previous sections we dealt with ideal amplifiers. This approximation is very useful in a first-order analysis and design. For example, assuming ideal open-loop gain in a real amplifier gives accurate results as long as low frequencies and low closed-loop gains are considered. However, under critical operating conditions such as high closed-loop gain, high frequency, non-ideal sources, large signal swing, etc., real values of performance parameters have to be accounted for, since they represent the final limits of operation. Therefore, we conclude the chapter by investigating the real parameters of current amplifiers which properly address the performance of this kind of circuit.

## Differential-mode Gain

The differential gain  $(A_d)$  sets the accuracy of the closed-loop transfer function in low frequency operations. It is defined by

$$A_d = \frac{i_o^+ - i_o^-}{i_i} \tag{1.21}$$

where  $i_o^+ - i_o^-$  is the differential-mode output. Referring to the three-stage architecture in Fig. 1.21b, the differential-mode gain can be expressed

$$A_d = r_{eq} A_{v2} \frac{i_o^+ - i_o^-}{v_{i3}} = r_{eq} A_{v2} G_{md}$$

(1.22)

where  $G_{md}$  is the differential-mode transconductance gain of the output stage.

# Common-mode Gain

Due to the duality with voltage amplifiers, the common-mode gain ( $A_c$ ) is defined with respect to the output common mode which is  $\frac{i_o^+ + i_o^-}{2}$

$$A_c = \frac{i_o^+ + i_o^-}{2i_i} \tag{1.23}$$

Again, referring to the circuit in Fig.1.21b,  $A_c$  can be rewritten as

$$A_c = r_{eq} A_{v2} \frac{i_o^+ + i_o^-}{2v_{i3}} = r_{eq} A_{v2} G_{mc}$$

(1.24)

where  $G_{mc}$  is the common-mode transconductance gain of the output stage. Output currents,  $i_o^*$  and  $i_o^-$ , can be expressed in terms of both the differential and common mode gains

$$i_o^+ = \left(\frac{1}{2}A_d + A_c\right)i_i$$

$$i_o^- = \left(-\frac{1}{2}A_d + A_c\right)i_i$$

(1.25)

$$i_o^- = \left(-\frac{1}{2}A_d + A_c\right)i_i$$

(1.26)

If the common-mode gain is zero, the output currents are equal in module and with opposite direction flow.

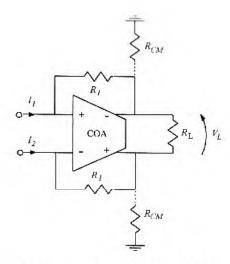

# Common-mode Rejection Ratio

As expected from the duality principle, the common-mode rejection ratio (CMRR) depends only on the performance of the output stage (the input stage in a voltage amplifier). It expresses the ability of the output stage to reject common-mode signals coming from its input (when it is operated in a fully-differential mode) or spurious signals from the supply lines and the substrate. CMRR is defined as

$$CMRR = \frac{A_d}{A_c} \tag{1.27}$$

For the typical architecture of COA in Fig. 1.21b, it is obtained by combining (1.22) and (1.24) which yields

$$CMRR = \frac{G_{md}}{G_{mc}} \tag{1.28}$$

# Input Resistance

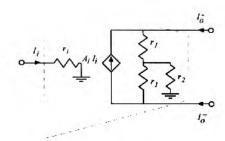

The input resistance (ri, in Fig. 1.24) should ideally be zero since the circuit has to accept current signals. In most amplifiers, the input resistance is set by the transistor transconductance which, in a CMOS design, is not sufficiently low to be neglected. The input resistance is responsible for a further pole in the loop-gain transfer function which can greatly affect either stability or the closed-loop bandwidth.

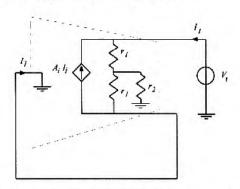

Fig. 1.24. Current amplifier with output resistances

# Differential and Common-mode Output Resistances

The differential  $(r_{od})$  and common-mode  $(r_{oc})$  output resistances can be defined by referring to Fig. 1.24. It is easy to find that

$$r_{od} = 2r_1 \tag{1.29}$$

$$r_{oc} = \frac{r_1}{2} + r_2 \tag{1.30}$$

To approximate an ideal current generator both the differential resistance and the common-mode resistance have to be high, as shall be explained in more detail later.

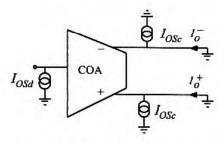

#### Offset Currents

There are two offset current components, i.e. the differential and the sommon-mode offset currents. Referring to Fig. 1.25 where the amplifier outputs are short-circuited to ground, the differential offset, IOSd, is the input current needed to set the differential output current  $(I_0^+ - I_0^-)$  to zero and the common-mode offset,  $I_{OSc}$ , is the output current which sets to zero

the common mode output current (

$$\frac{I_o^+ + I_o^-}{2}$$

).

Fig. 1.25. COA with offset currents

Of course, the common-mode offset is an inherent parameter of the output stage. In fact, it depends on the mismatches in the output stage and, hence, cannot be compensated by any input current.

#### Input Offset Voltage

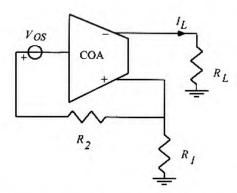

Ideally, the input bias voltage of a current amplifier is the reference (ground) voltage. As can be seen in Fig. 1.26, any deviation,  $V_{OS}$ , of the input bias voltage from the ideal value causes a DC current to flow through the resistor  $R_L$

Fig. 1.26. Feedback COA with input offset voltage

Hence, the current in the load is given by

$$I_L = \frac{V_{OS}}{R_1} \tag{1.31}$$

Of course, the offset voltage does not contribute to the output offset current if  $R_1$  is infinitely large, as in the unity-gain buffer configuration.

# Input and Output Current Ranges

The input current range (ICR) is the maximum input current which allows the circuit to work properly. This range is generally set by the overall transresistance gain and the voltage range at internal high impedance nodes. Like the differential input voltage range in voltage amplifiers, it is not a parameter of interest. Indeed, with high loop gain the required input range is nearly zero.

The output current range (OCR) is the maximum differential current which can be delivered by the output stage in short-circuit conditions. It depends on the current-drive capability of the output stage.

#### Slew Rate

Like in voltage amplifiers, the slew rate (SR) sets the maximum variation of the output current. In principle, a current amplifier with a class AB input stage (i.e., the input current buffer) behaves like a CFOA. In Fig. 1.21b, the input stage can deliver unlimited current to the internal node Z. Therefore, if a dominant-pole compensation is adopted by putting the compensation appacitor between node Z and ground, no slew-rate limitation arises. However, gain requirements with decreasing supply voltages lead to solutions with cascaded gain stages that require Miller compensation, as shown in Fig. 1.21b. In these cases, to preserve the high slew rate performance, the inverting stage (i.e.,  $A_{V2}$ ) should also be implemented with a class AB topology. Unfortunately, this is an expensive approach.

# **Power Supply Rejection Ratio**

Like in conventional amplifiers, the power supply rejection ratio (PSRR) describes the ability of the amplifier to reject spurious signals coming from either the positive or negative power supply lines. It can be defined as

$$PSRR^{(+,-)} = \frac{\frac{I_o}{I_i}}{\frac{I_o}{(V_{dd}, V_{ss})}}$$

(1.32)

and its unit is  $\Omega$ .

#### Noise

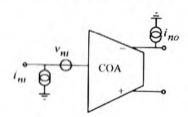

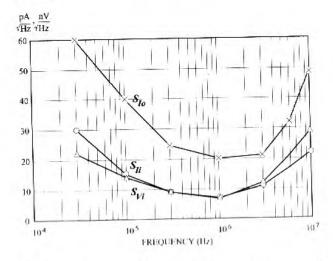

Noise in current amplifiers can be modeled by means of three noise generators (a voltage and a current generator at the input and a current generator at the output), as illustrated in Fig. 1.27 [79]. The motivations behind this representation will be discussed in detail in sec. 1.7.1.

Fig. 1.27. Noise model of a COA

Here it is sufficient to say that unlike conventional VOAs, where only the input referred noise is important, in current amplifiers the noise produced by the output stage can also be significant since the output terminal connected to the load works outside the feedback loop.

We conclude this description by pointing out that the above performance parameters strictly refer only to COA. Due to its different output stage a VFCOA is characterized by a different set of parameters. Of course, differential- and common-mode gain and resistances are no longer suitable in the latter case. In addition, parameters such as offset and *PSRR* have slightly changed definitions. Aside from the above, most parameters of a COA can be extended to a VFCOA, so we shall not deal with this item any further. Instead, we shall conclude the chapter by specifying some features presented above in more detail and by providing some examples of how they affect overall closed loop performance.

#### 1.7.1 Further Comments

Most of the performance parameters of VOA and COA are very similar in their definition. However, due to duality some parameters in the COA auch us offset current, differential- and common-mode gain and resistances belong to the output rather than the input. Noise needs also to be further detailed since it depends heavily on the specific features of the COA. In the following, we consider the properties of the output resistance and noise in typical feedback configurations. Moreover, we make final considerations regarding the constant-bandwidth property of the VFCOA.

# A. Evaluation of the output resistance in a feedback amplifier

Considering the COA in a current buffer feedback configuration as shown in Fig. 1.28, the output resistance becomes

Fig. 1.28. Equivalent circuit for the output resistance calculation in a feedback COA

$$r_o = \frac{V_t}{I_t} = r_1 + \frac{r_1(1 + 2A_i)}{1 + \frac{r_1}{r_2}(1 + A_i)}$$

(1.33)

If  $r_2 \to \infty$ , the common-mode output resistance in (1.30) is infinite and (1.33) simplifies to

$$r_o = 2r_1(1 + A_i) \tag{1.34}$$

Operational Amplifiers

that from (1.29) can be written as

$$r_o = r_{od}(1 + A_i) \tag{1.35}$$

This is the expected result for the output resistance of a shunt-series feedback amplifier: the differential output resistance is increased by the loop gain.

However, for finite values of  $r_2$  and assuming  $A_i >> 1$ , (1.33) can be approximated to

$$r_o \cong r_1 + 2r_2 = 2r_{oc} \tag{1.36}$$

This means that the common-mode output resistance sets an upper limit to the maximum achievable output resistance in a feedback COA. The same result can be obtained for the input resistance by using the popular voltage buffer implemented with a VOA.

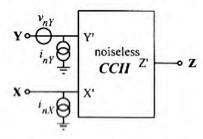

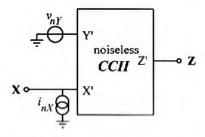

## B. Noise contributions

Let us consider the typical architecture of a COA shown in Fig. 1.29.

Fig. 1.29. Equivalent noise generators of the COA stages

The noise in a CCII is characterized by a voltage and a current generator (see section 2.1.1) modeled at the input by  $v_n y$  and  $i_n x$ . Voltage and current generators  $v_{ni2}$  and  $i_{ni2}$  account for the noise of the second gain stage. Voltage  $v_{ni2}$  appears at the output node (Z) of the CCII and hence its contribution to the input (X) is heavily attenuated by the high transresistance gain of the CCII. Due to the unitary current gain between X and Z, current  $i_{ni2}$  is added directly to the input stage current. Finally, we have to consider the noise contribution of the output stage. Generally, noise due to a current output stage can be divided into two components:

- the first component is referred to its input and can be represented with a voltage noise v<sub>ni3</sub>. It can be further referred to the input of the input stage. This contribution to the overall noise is negligible due to the first and second stage gains.

- the second component is a noise current that adds directly to the outputs and can be modeled, in general, with two noise current generators ino- and ino+.

However, the non-inverting terminal is usually connected in feedback with the input. Moreover, since no current flows through the op-amp input,  $i_{nO+}$  appears to the inverting output. As a result, both  $i_{nO-}$  and  $i_{nO+}$  can be represented at the inverting output terminal. It is interesting to note that a similar output noise component, but as a voltage generator, is also present in a VOA. However, since the output stage in a VOA is inside the feedback loop, the output noise voltage generator is heavily reduced by the loop gain.

To conclude this analysis, the noise model of a COA can be represented by three noise generators  $v_{ni}$  which is equal to  $v_{ny}$ ,  $i_{ni}$  accounting for  $i_{nX}$  and  $i_{ni2}$  and  $i_{no}$  which in turn accounts for  $i_{nO+}$  and  $i_{no-}$ .

# C. Noise in a feedback amplifier

It is useful to evaluate overall noise power in a typical feedback amplifier based on the COA shown in Fig. 1.30. To simplify calculations, the noise related to  $R_1$  and  $R_2$  have been represented as current and voltage generators, respectively.

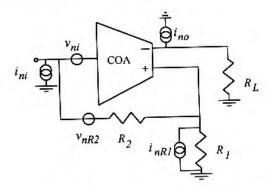

Fig. 1.30. Noise in a feedback COA

The overall output noise power,  $N_O$ , is

$$N_o = A_{cl}^2(0)\overline{i_{ni}^2} + \frac{\overline{v_{ni}^2} + \overline{v_{nR2}^2}}{R_1^2} + \overline{i_{nR1}^2} + \overline{i_{no}^2}$$

(1.37)

where  $A_{cl}(0)$  is the closed-loop gain.

It is interesting to compare (1.37) with the noise power of the typical VOA feedback amplifier in Fig. 1.31, assuming constant gain.

The output noise power for circuit in Fig. 1.31 is

$$N_o = A_{cl}(0)\overline{v_{ni}^2} + R_2^2(\overline{i_{ni}^2} + \overline{i_{nR1}^2}) + \overline{v_{nR2}^2}$$

(1.38)

where  $A_{cl}(0)$  is the non-inverting closed-loop gain.

Similarly to the noise voltage in a VOA, the contribution of the input noise current in a COA is independent of the value of  $R_1$  and  $R_2$ . The contribution of the input noise voltage in a COA is reduced by increasing  $R_1$  while in a VOA the noise current is increased by increasing the feedback resistance ( $R_2$ ). In respect of the noise due to the resistors in the feedback network, their contribution in a COA can be reduced by increasing the resistor values. In contrast, the noise coming from the network resistors in a VOA is increased by increasing the resistor values.

Finally, if  $i_{no}$  is much greater than  $i_{ni}$  (this is the case when both the current and the aspect ratios of the output stage transistors are large), the output stage noise cannot be neglected.

In its conclusion (1.37) asserts that, with a fixed closed-loop gain, the noise performance of a current amplifier can be improved by increasing the values of the feedback resistors. This is not a surprising result since the circuit is a current processor and the noise current of a resistor is inversely proportional to its resistance. Unfortunately, this is in contrast with the need to reduce voltage biasing. Indeed, the increase in  $R_2$  in turn increases the voltage swing at the non-inverting output and consequently a reduction in the dynamic range. Dynamic range, D, is defined as the ratio of the maximum achievable output current to the minimum usable input current. It is limited by noise and non-linearity at the lower and upper bounds, respectively.

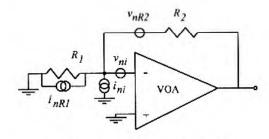

Fig. 1.31. Noise in a feedback VOA

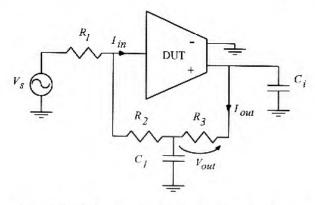

#### D. Constant bandwidth in a VFCOA

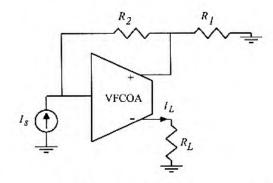

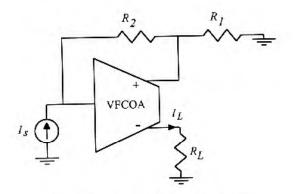

Let us again consider the typical closed-loop VFCOA configuration in Fig. 1.32:

Fig. 1.32. Closed loop VFCOA configuration

The loop gain, T(s) is given by

$$T(s) = R_t(s) \frac{R_1}{(R_2 + r_i)(R_1 + r_{o1}) + R_1 r_{o1}}$$

(1.39)

Equation (1.39) accounts for the input and output resistances,  $r_i$  and  $r_{ol}$ , respectively, of a real transresistance amplifier.

Assuming for  $R_I(x)$  a dominant-pole behavior with pole  $\omega_C$ , the closed-loop bandwidth,  $\omega_{c,I}$ , is approximately given by

$$\omega_{cl} \cong T(0)\omega_o \tag{1.40}$$

If the amplifier is implemented in a bipolar technology, the condition that  $r_i$  and  $r_{oI}$  are much lower than  $R_I$  and  $R_2$  is usually met, so that from (1.39) and (1.40) the bandwidth of the closed-loop amplifier results as:

$$\omega_{cl} \cong \frac{R_t(0)}{R_2} \omega_o \tag{1.41}$$

Equation (1.41) shows the same well-known property of a current feedback voltage amplifier (remember the duality with a voltage feedback current amplifier). The bandwidth of the closed-loop amplifier will remain independent of the closed-loop current gain provided that resistance  $R_2$  is maintained constant.

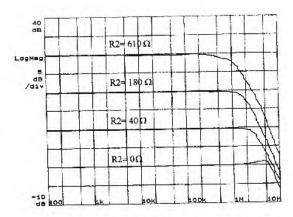

The same result is also valid for low-drive current amplifiers in CMOS technology in which, due to the low output current, feedback resistances are set much higher than internal resistances to achieve (1.41).

In contrast, with high-drive CMOS amplifiers employing a class AB voltage follower as output stage (in the transresistance amplifier),  $R_1$  and  $R_2$  should be made low due to the limited output voltage swing. Therefore, for high-drive CMOS amplifiers, the condition that  $r_i$  and  $r_{o1}$  are greater than  $R_1$  and  $R_2$  is usually assumed. Hence, from (1.39) and (1.40), the bandwidth of the closed-loop amplifier becomes:

$$\omega_{cl} \cong R_t(0) \frac{R_l}{r_i r_{ol}} \omega_o \tag{1.42}$$

which means that the bandwidth is still constant provided that  $R_I$  is kept constant, but the dc loop gain and  $\omega_{cl}$  now depend on the input and output resistances.

It is worth noting, however, that for the unity-gain configuration in which  $R_I$  is infinite and  $R_2$  is zero, (1.39) becomes

$$\omega_{cl} \cong R_t(0) \frac{1}{r_i + r_{ol}} \omega_o \tag{1.43}$$

Of course, to achieve higher closed-loop gains, resistance  $R_2$  has to be increased. However, when  $R_2$  has the same order of magnitude of  $r_i$  the closed-loop gain asymptotically tends to a constant GBW behavior since (1.42) is no longer valid.

# REFERENCES

- S. Franco, Design with Operational Amplifiers and Analog Integrated Circuits, McGraw-Hill, 1988.

- [2] S. Soclof, Design and Applications of Analog Integrated Circuits, Prentice-Hall, 1991.

- [3] J. Wait, L. Huelsman, Introduction to Operational Amplifier Theory and Applications, McGraw-Hill, 1992.

- [4] K. Laker, W. Sansen, Design of Analog Integrated Circuits and Systems, Mc Graw-Hill, 1994.

- [5] Z. Wang, Current-Mode Analog Integrated Circuits and Linearization Techniques in CMOS Technology, Hartung-Gorre Verlag Konstanz, 1990.

- [6] C. Toumazou, F. Lidgey, C. Makris, "Extending Voltage-Mode OP Amps to Current-Mode Performance," *IEE Proc. Part G*, Vol.137, No.2, pp. 116-130, Apr. 1990.

- [7] C. Toumazou, F. Lidgey, D. Haigh (Eds.), Analogue IC design: the current-mode approach, Peter Peregrinus, 1990.

- [8] Z. Wang, "Current-Mode CMOS Integrated Circuits for Analog Computation and Signal Processing: A Tutorial," Int. J. Analog Integrated Circuits and Signal Processing, No.1, pp.287-295, 1991.

- [9] G. Wilson, "Advances in Bipolar VLSI," Proceeding of IEEE, Vol. 78 No. 11, pp. 1707-1719, Nov. 1990.

- [10] M. Kurisu, et al., "A Si Bipolar 21-GHz/320-mW Static Frequency Divider," IEEE J. of Solid-State Circuits, Vol. 26, No. 11, pp. 1626-1630, Nov. 1991.

- [11] C. Stout, J. Doernberg, "10-Gb/s Silicon Bipolar 8:1 Multiplexer and 1:8 Demultiplexer," *IEEE J. of Solid-State Circuits*, Vol. 28, No. 3, pp. 339-343, Mar. 1993.

- [12] K. Ishii, et al. "Very-High-Speed Si Bipolar Static Frequency Dividers with New T-Type Flip-Flops," *IEEE J. of Solid-State Circuits*, Vol. 30, No. 1, pp. 19-24, Jan. 1995.

- [13] Z. H. Lao, et al., "A 12 Gb/s Si Bipolar 4:1-Multiplexer IC for SDH Systems," IEEE J. of Solid-State Circuits, Vol. 30, No. 2, pp. 129-132, Feb. 1995.

- [14] L. I. Andersson, et al., "Silicon Bipolar Chipset for SONET/SDH 10 Gb/s Fiber-Optic Communication Links," *IEEE J. of Solid-State Circuits*, Vol. 30, No. 3, pp. 210-217, Mar. 1995.

- [15] K. M. Sharaf, M. I. Elmasry, "Analysis and Optimization of Series-Gates CML and ECL High-Speed Bipolar Circuits," *IEEE J. of Solid-State Circuits*, Vol.31, No. 2, pp. 202-211, Feb. 1996.

- [16] J. Rabaey, Digital Integrated Circuits (A Design Perspective), Prentice Hall, 1996.

- [17] P. Crolla, "A Fast Latching Current Comparator for 12-Bit A/D Applications," IEEE J. of Solid State Circuits, Vol. 50, 17, No. 6, pp. 1088-1091, Dec. 1982.

- [18] J. Robert, P. Deval, G. Wegmann, "Novel CMOS Pipelined A/D Convertor Architecture Using Current Mirrors," *Electronics Letters*, Vol.25, No.11, pp.691-692, May 1989.

- [19] D. Nairn, C. Salama, "Current-Mode Algorithmic Analog-to-Digital Converters," *IEEE J. of Solid-State Circuits*, Vol.25, No.4, pp.997-1004, Aug. 1990.

- [20] Chu P. Chong, "A Technique for Improving the Accuracy and the Speed of CMOS Current-Cell DAC," *IEEE Trans. on Circuits and Systems*, Vol.37, No.10, pp.1325-1327, Oct. 1990.

- [21] D. Nairn, C Salama "A Ratio-Independent Algorithmic Analog-to-Digital Converter Combining Current Mode and Dynamic Techniques" *IEEE Trans.* on Circuits and Systems, Vol.37, No.10, pp.1325-1327, Oct. 1990.

- [22] Z. Wang, "Design Methodology of CMOS Algorithmic Current A/D Converters in View of Transistor Mismatches," IEEE Trans. on Circuits and Systems, Vol.38, No.6, pp.660-667, June 1991.

- [23] Seong-Won Kim, Soo-Won Kim, "Current-Mode Cyclic ADC for Low Power and High Speed Applications," Electronics Letters, Vol.27, No.10, pp.818-820, May 1991.

- [24] C. Wey, "Concurrent Error Detection in Current-Mode A/D Convertors," Electronics Letters, Vol.27, No.25, pp.2370-2372, Dec. 1991.

- [25] A. Cujec, C. Salama, D. Nairn, "An Optimized Bit Cell Design for a Pipelined Current-Mode Algorithmic A/D Converter," Int. J. Analog Integrated Circuits and Signal Processing, No.3, pp.137-141, 1993.

- [26] C. Wey, S. Krishnan, S. Sahli, "Design of Concurrent Error Detectable Current-Mode A/D Converters for Real-Time Applications," Int. J. Analog Integrated Circuits and Signal Processing, No.4, pp.65-74, 1993.

- [27] K. Wong, K. Chao "Current-Mode Cyclic A/D Conversion Technique," Electronics Letters, Vol.29, No.3, pp.249-250, Feb. 1993.

- [28] S. Pookiyaudom, R. Sitdhikorn, "Current-Differencing Band-Pass Filter Realization with Application to High-Ferquency Electronically Tunable Low-Supply-Voltage Current-Mirror-Only Oscillator," *IEEE Trans. on Circuits* and Systems- part II, Vol. 43, No. 12, pp. 832-835, Dec. 1996.

- [29] R. Zele, D. Allstot, "Low-Power CMOS Continuous-Time Filters," IEEE J. of Solid-State Circuits, Vol. 31, No.2, pp. 157-168, Feb. 1996.

- [30] S. Smith, E. Sanchez-Sinencio, "Low Voltage Integrators for High-Frequency CMOS Filters Using Current Mode Techniques," *IEEE Trans. on Circuits and Systems - part II*, Vol. 43, No. 1, pp. 39-48, Jan. 1996.

- [31] E. El-Masry, J. Gates, "A novel Continuous-Time Current-Mode Differentiator and Its Applications," *IEEE Trans. on Circuits and Systems* part II, Vol. 43, No. 1, pp. 56-59, Jan. 1996.

- [32] Joung-Chul Ahn, A. Fujii, "Current-Mode Continuous-Time Filters Using Complementary Current Mirror Pairs," Int. J. Analog Integrated Circuits and Signal Processing, No. 11, pp. 109-118, 1996.

- [33] J. Ramirez-Angulo, E. Sanchez-Sinencio, M. Howe, "Large foQ Second Order Filters Using Multiple Output OTAS," IEEE Trans. on Circuits and Systems - part II, Vol. 41, No. 9, pp. 587-592, Sept. 1994.

- [34] G. Moschytz, A. Carlosena, "A Classification of Current-Mode Single-Amplifier Biquads Based on a Voltage-to-Current Transformation," IEEE Trans. on Circuits and Systems part II, Vol. 41, No.2, pp. 151-156, Feb. 1994.

- [35] S. Lee, R. Zele, D. Allstot, G. Liang, "CMOS Continuous-Time Current-Mode Filters for High-Frequency Applications," IEEE J. of Solid-State Circuits, Vol. 28, No. 3, pp. 323-328, Mar. 1993.

- [36] A. Wyszynski, R. Schaumann, "A Current-Mode Biquadratic Amplitude Equalizer," Int. J. Analog Integrated Circuits and Signal Processing, No. 4, pp. 161-166, 1993.

- [37] W. Serdijn, "A Low-Voltage Low-Power Current-Mode High-Pass Leapfrog Filter," Int. J. Analog Integrated Circuits and Signal Processing, No. 3, pp. 105-112, 1993.

- [38] J. Ramirez-Angulo, M. Robinson, E. Sanchez-Sinencio, "Current-Mode Continuous-Time Filters: Two Design Approaches" *IEEE Trans. on Circuits* and Systems - part II, Vol. 39, No. 6, pp. 337-341, June 1994.

- [39] R. Brennan, T. Viswanathan, J. Hanson, "The CMOS Negative Impedance Converter," IEEE J. of Solid-State Circuits, Vol. 23, No. 5, pp. 1272-1275, Oct. 1988.

- [40] J. Haslett, M. Rao, L. Bruton, "High-Frequency Active Filter Design Using Monolithic Nullors," *IEEE J. of Solid-State Circuits*, Vol. SC-15, No.6, pp.955-962, Dec. 1980.

- [41] W. Serdijn, M. Broest, J. Mulder, A. van der Woerd, A. Roermund, "A Low-Voltage Ultra-Low-Power Translinear Integrator for Audio Filter Applications," *IEEE J. of Solid-State Circuits*, Vol. 32, No. 4, pp. 577-581, Apr. 1991.

- [42] J. Mulder, A. van der Woerd, W. Serdijn, A. Roermund, "General Current-Mode Analysis Method for Translinear Filters," IEEE Trans. on Circuits and Systems part I, Vol. 44, No. 3, pp. 193-197, Mar. 1997.

- [43] Y. Tsividis, "Externally Linear, Time-Invariant Systems and Their Applications to Companding Signal Processor," *IEEE Trans. on Circuits and Systems - part II*, Vol. 44, No. 2, pp. 65-85, Feb. 1997.

- [44] D. Perry, G. Roberts, "The design of Log-Domain Filters Based on the Operational Simulation of LC Ladders," *IEEE Trans. on Circuits and Systems* - part II, Vol. 43, No. 11, pp. 763-774, Nov. 1996.

- [45] D. Frey, "Log Domain Filtering for RF Applications," IEEE J. of Solid-State Circuits, Vol. 31, No. 10, pp. 1468-1475, Oct. 1996.

- [46] D. Frey, "Exponential State Space Filters: A Generic Current Mode Design Strategy," *IEEE Trans. on Circ. and Syst - part I*, Vol. 43, No. 1, pp. 34-42, Jan. 1996.

- [47] J. Mahattanakul, C. Toumazou, "Modular Log-Domain Filters," Electronics Letters, Vol. 33, No. 13, pp. 1130-1131, 1997

- [48] D. Frey, "Log-Domain Filtering: an Approach to Current-Mode Filtering," IEE Proc. Part G, Vol.140, No.6, pp. 406-416, Dec. 1993.

- [49] D. Frey, "Log Filtering Using Gyrators," Electronics Letters, Vol.32, No. 1 pp. 26-28, 1996.

- [50] A. Thanachayanont, S. Pookaiyaudom, C. Toumazou, "State-Space Synthesis of Log-Domain Oscillators," *Electronics Letters*, Vol. 31, No. 21, pp. 1797-1799, 1995.

- [51] E. Seevinck, "Companding Current-Mode Integrator: A new Circuit Principle for Continuous-Time Monolithic Filters," *Electronics Letters*, Vol.26, No. 24, pp.2046-2047, 1990.

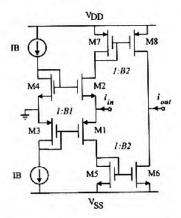

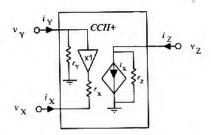

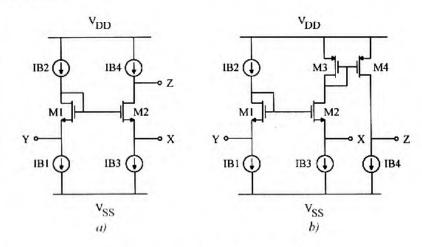

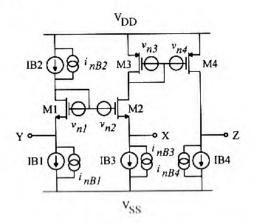

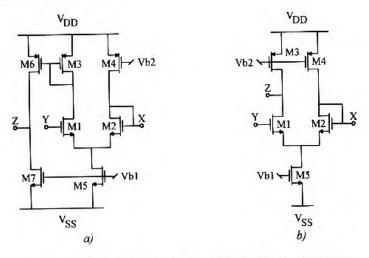

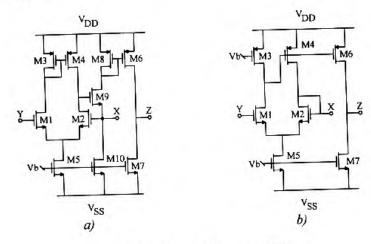

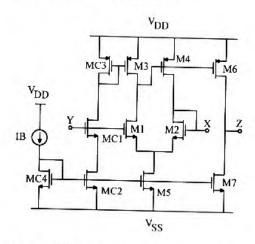

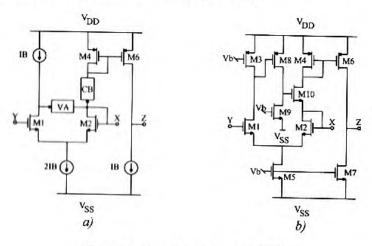

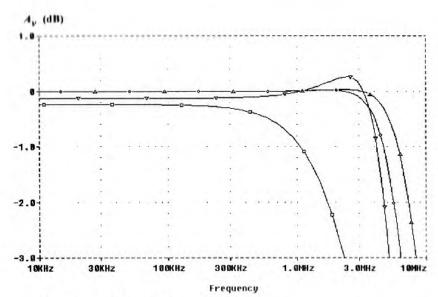

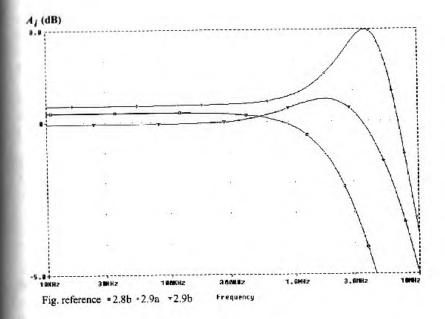

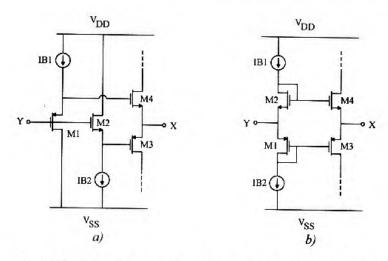

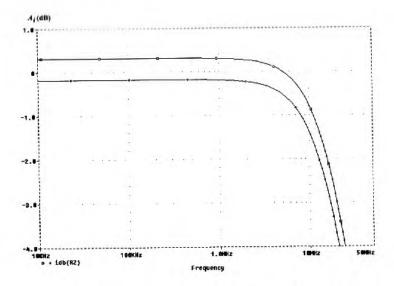

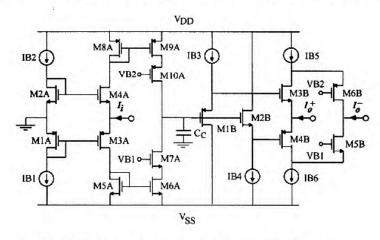

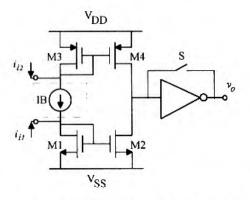

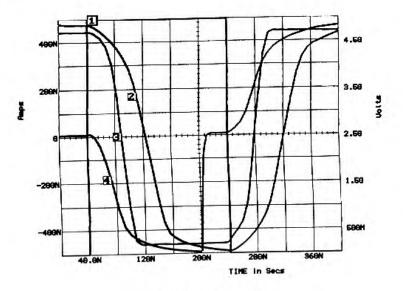

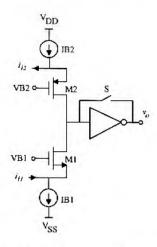

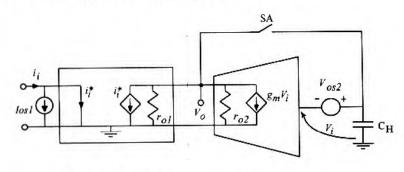

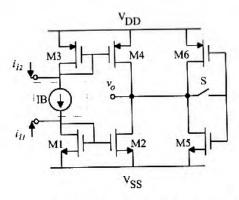

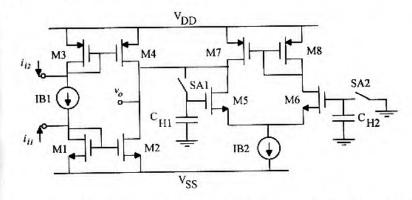

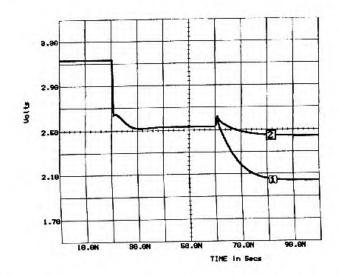

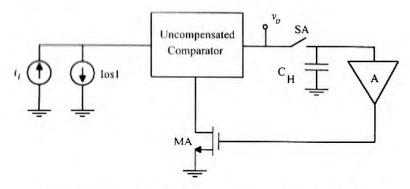

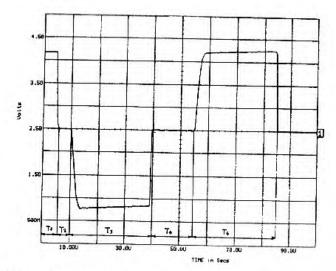

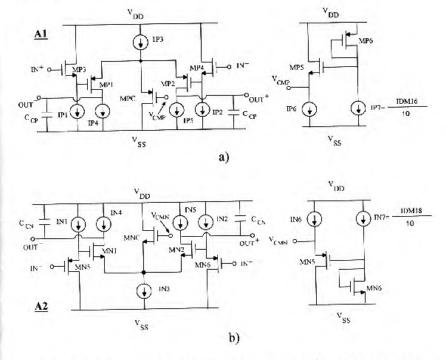

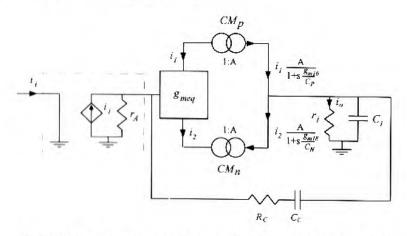

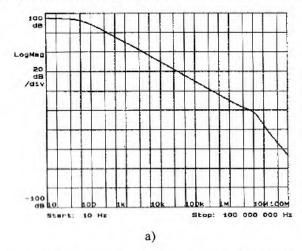

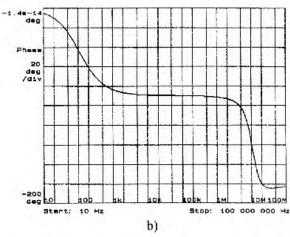

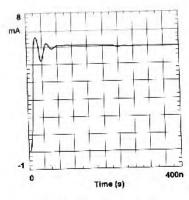

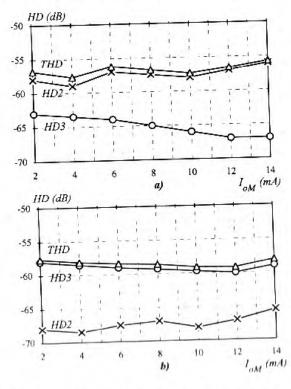

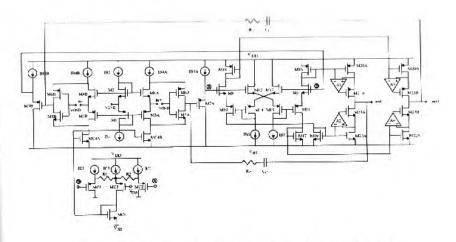

- [52] B. Gilbert "Translinear Circuits: An Historical Overview," Int. J. Analog Integrated Circuits and Signal Processing, No.9, pp. 95-118, 1996.