# ADVANCED FIELD-EFFECT TRANSISTORS

THEORY AND APPLICATIONS

Edited by Dharmendra Singh Yadav, Shiromani Balmukund Rahi, and Sukeshni Tirkey

# **Advanced Field-Effect Transistors**

Advanced Field-Effect Transistors: Theory and Applications offers a fresh perspective on the design and analysis of advanced field-effect transistor (FET) devices and their applications. The text emphasizes both fundamental and new paradigms that are essential for upcoming advancement in the field of transistors beyond complementary metal–oxide–semiconductors (CMOS). This book uses lucid, intuitive language to gradually increase the comprehension of readers about the key concepts of FETs, including their theory and applications.

In order to improve readers' learning opportunities, *Advanced Field-Effect Transistors: Theory and Applications* presents a wide range of crucial topics:

- Design and challenges in tunneling FETs

- Various modeling approaches for FETs

- Study of organic thin-film transistors

- Biosensing applications of FETs

- Implementation of memory and logic gates with FETs

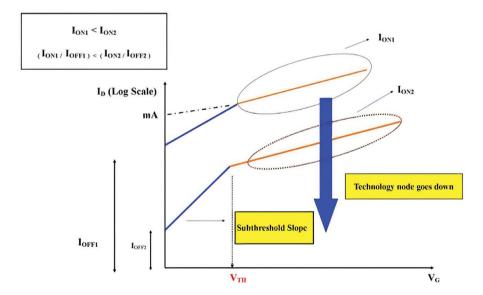

The advent of low-power semiconductor devices and related implications for upcoming technology nodes provide valuable insight into low-power devices and their applicability in wireless, biosensing, and circuit aspects. As a result, researchers are constantly looking for new semiconductor devices to meet consumer demand. This book gives more details about all aspects of the low-power technology, including ongoing and prospective circumstances with fundamentals of FET devices as well as sophisticated low-power applications.

# Advanced Field-Effect Transistors Theory and Applications

Edited by Dharmendra Singh Yadav Shiromani Balmukund Rahi Sukeshni Tirkey

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business Designed cover image © Shutterstock

First edition published 2024 by CRC Press 6000 Broken Sound Parkway NW, Suite 300, Boca Raton, FL 33487-2742

and by CRC Press 4 Park Square, Milton Park, Abingdon, Oxon, OX14 4RN

CRC Press is an imprint of Taylor & Francis Group, LLC

© 2024 selection and editorial matter, Dharmendra Singh Yadav, Shiromani Balmukund Rahi, and Sukeshni Tirkey; individual chapters, the contributors

Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, access www.copyright.com or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. For works that are not available on CCC please contact mpkbookspermissions@tandf. co.uk

**Trademark notice**: Product or corporate names may be trademarks or registered trademarks and are used only for identification and explanation without intent to infringe.

ISBN: 9781032493800 (hbk) ISBN: 9781032493879 (pbk) ISBN: 9781003393542 (ebk)

#### DOI: 10.1201/9781003393542

Typeset in Times LT Std by KnowledgeWorks Global Ltd.

### Dedication

I would like to dedicate this book and express my hearty gratitude toward my respected parents, uncle, aunty, younger brothers, and sisters for their affection and persistent efforts in my education. Also dedicated to my wife and our loving son for their everlasting supports, encouragements, and understanding. This work is dedicated to my family; my teacher, the late Dr. Dheeraj Sharma Sir; my dear student, Prabhat Singh; and others, who have always been a source of my continued efforts for academic excellence.

### -Dr. Dharmendra Singh Yadav

This textbook is dedicated to "almighty GOD and our family members," for their affection, untiring efforts, and patience.

### -Dr. Shiromani Balmukund Rahi

To my revered parents, for their affection and untiring efforts in my upbringing. Also dedicated to my husband, Ashish, and our loving son, Avyan, for their precious time and patience.

-Dr. Sukeshni Tirkey

# Contents

| Editors Biog | ix<br>graphy                                                                                        |

|--------------|-----------------------------------------------------------------------------------------------------|

| Chapter 1    | Future Prospective Beyond-CMOS Technology: From Silicon-<br>Based Devices to Alternate Devices      |

|              | G. Boopathi Raja                                                                                    |

| Chapter 2    | Design and Challenges in TFET23                                                                     |

|              | Soumya Sen, Mamta Khosla, and Ashish Raman                                                          |

| Chapter 3    | Modeling Approaches to Field-Effect Transistors                                                     |

|              | Abhay Pratap Singh, R.K. Baghel, Sukeshni Tirkey,<br>and Bharat Singh Choudhary                     |

| Chapter 4    | Dynamics of Trap States in Organic Thin-Film Transistors<br>(OTFTs)                                 |

|              | Farkhanda Ana, Haider Mehraj, and Najeeb-ud-Din                                                     |

| Chapter 5    | An Insightful Study and Investigation of Tunnel FET<br>and Its Application in the Biosensing Domain |

|              | Priyanka Goma and Ashwani K. Rana                                                                   |

| Chapter 6    | Optimization of Hetero Buried Oxide Doped-Pocket Gate-<br>Engineered Tunnel FET Structures          |

|              | Sirisha Meriga and Brinda Bhowmick                                                                  |

| Chapter 7    |                                                                                                     |

|              | Yuvraj Kadale, Prabhat Singh, and Dharmendra Singh Yadav                                            |

| Chapter 8    | Thermal Behavior of Si-Doped MoS <sub>2</sub> -Based Step-Structure<br>Double-Gate TFETs            |

|              | Priya Kaushal and Gargi Khanna                                                                      |

| Chapter 9  | Implementation of Logic Gates Using Step-Channel TFETs 186                            |   |  |  |  |

|------------|---------------------------------------------------------------------------------------|---|--|--|--|

|            | Varun Bharti, Prabhat Singh, and Dharmendra Singh Yadav                               |   |  |  |  |

| Chapter 10 | CMOS-Based SRAM with Odd-Numbered Transistor<br>Configurations: An Extensive Study    | 6 |  |  |  |

|            | Dharmendra Singh Yadav, Prabhat Singh, and Vibhash Choudhary                          |   |  |  |  |

| Chapter 11 | Gate-All-Around Nanosheet FET Device Simulation<br>Methodology Using a Sentaurus TCAD | 2 |  |  |  |

|            | Anushka Singh and Archana Pandey                                                      |   |  |  |  |

| Chapter 12 | Device Simulation Process on TCAD                                                     | 0 |  |  |  |

|            | Abhay Pratap Singh, R.K. Baghel, and Sukeshni Tirkey                                  |   |  |  |  |

| Index      |                                                                                       | 7 |  |  |  |

# Preface

Complementary metal-oxide-semiconductor (CMOS) technology has evolved as the dominant fabrication process in the past few decades, and it has become the only option for semiconductor industries, but it's not best suited for low-power applications. The uses of developing semiconductor devices in electronic circuits are explored throughout this book. It addresses systematic and comprehensive engineering problems as well as applications of sophisticated low-power devices. The advent of low-power semiconductor devices and related implications for upcoming technology nodes provide valuable insight into low-power devices and their applicability in wireless, biosensing, and circuit aspects. The book gives more details about all aspects of the low-power technology, including ongoing and prospective circumstances. The book also covers the fundamentals of field-effect transistor (FET) devices and highlights new and upcoming FET technologies. An evaluation of the use of FET devices in diverse fields, such as biosensing, wireless, and cryogenics applications, is also included. In the digital and analog realms, the chapters additionally look at device-circuit co-design difficulties. The information is provided in an easy-to-understand approach, making it excellent for those who are new to the subject. For the reader's reference, we have included many device architectures presented by various researchers. This will help readers understand the strategies for improving the properties of FETs. Furthermore, these strategies will inspire readers to create their own device optimization techniques and research FETs to make them appropriate for forthcoming circuit applications. Finally, the book covers how to perform numerical simulations of FETs using the technology computer-aided design (TCAD) tools Silvaco ATLAS and Sentaurus to assist new researchers in the subject of FETs. In addition, this book endeavors to cover all recent scholarly articles on FETs to ensure that it also covers the state of the art. We have emphasized the qualitative qualities of the devices throughout this book. This was done so that readers could obtain a spontaneous grasp of the devices rather than being obstructed by complex equations. This book is projected to accomplish this prerequisite for deviceto-circuit-level research work.

#### SHORT EXPLANATION OF THE CHAPTERS

Effective communication among research scholars working on device processes, device physics and modeling, circuit designs, sensing applications with advanced materials, and quantum mechanics is a critical facilitator for hatching and advancing innovations from investigation to implementation. Chapters in this book cover:

*Chapter 1*: This chapter predicts that the CMOS transistor must be able to scale to at least the 3 nm node by the year 2021 to 2022. CMOS might finally run out of steam, prompting the creation of a new switch technology. In order to continue improving the power and performance of computing, it is crucial for the semiconductor industry to find a new integrated circuit technology that can take us beyond the CMOS era. Devices based on electron spin (spintronics) and nano-magnetism

are examples of fields that are currently being explored, as are quantum electronic devices such as the tunneling field-effect transistor (TFET).

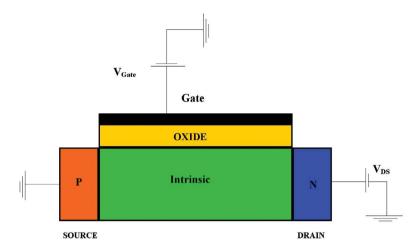

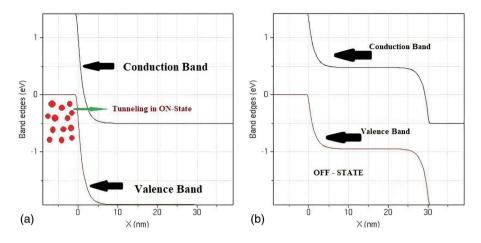

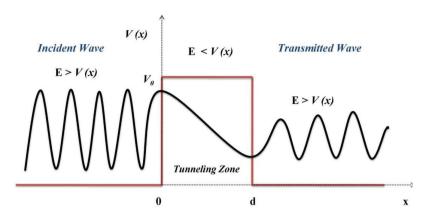

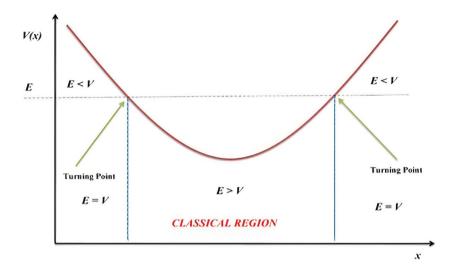

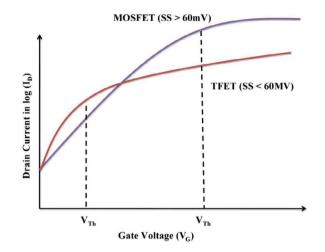

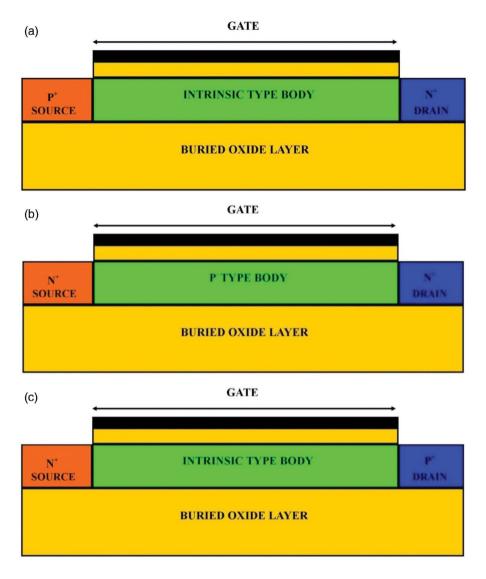

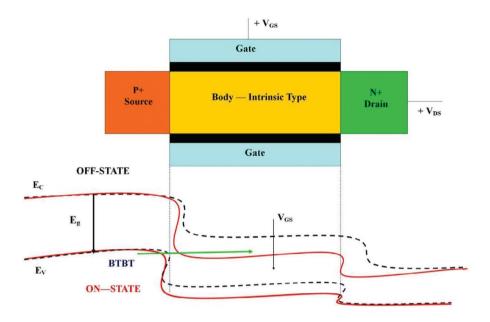

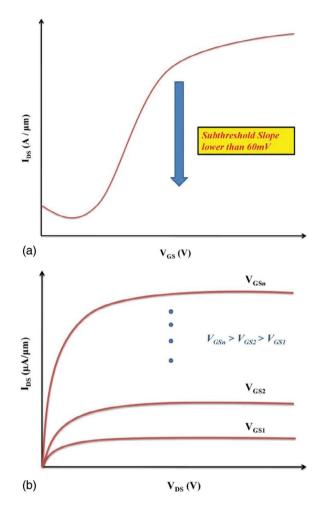

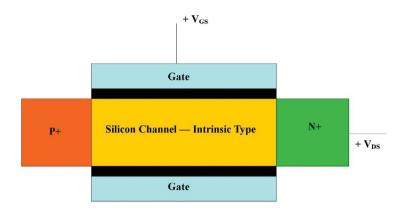

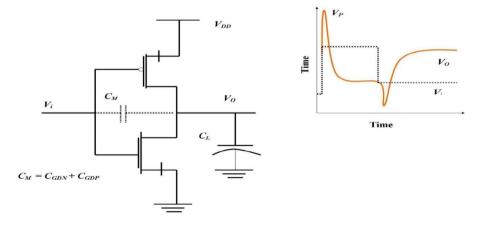

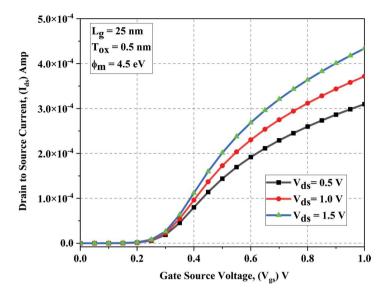

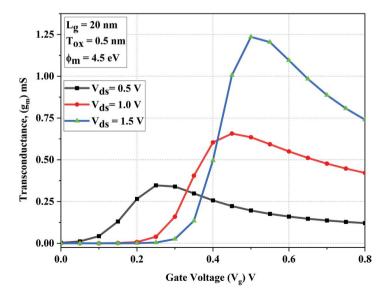

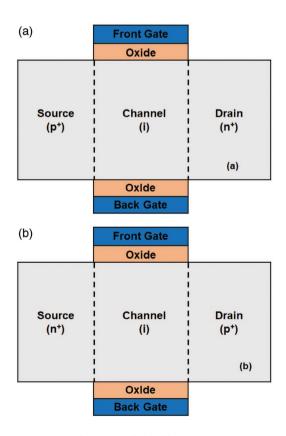

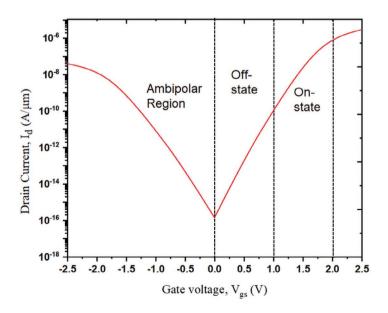

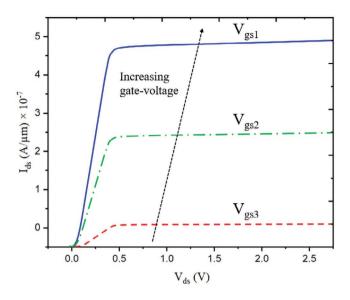

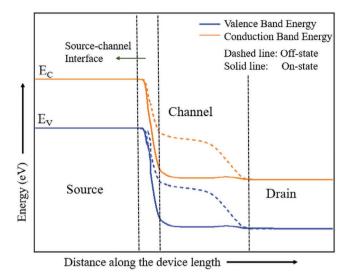

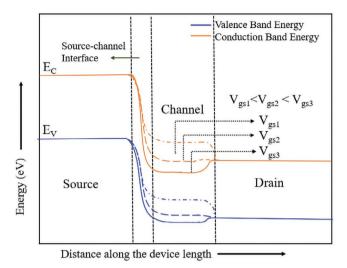

*Chapter 2*: This chapter describes tunneling briefly. The tunneling phenomenon and the methodology for calculating the tunneling rate are also offered. By describing the current–voltage statistics, TFET functioning is explained. Ambipolarity and low ON-state current are two concerns that affect TFET effectiveness; methods to address them, such as gate–drain under- and overlap, hetero gate dielectrics structures, and area-scaled TFET topologies, are detailed. It is shown that III-V TFETs can overcome the diminished  $I_{ON}$  constraint. A TFET-based circuit design methodology is also reported. Ways to deal with these issues, such as prolonged saturation, increased Miller capacitance, and unidirectional conductivity, are discussed.

*Chapter 3*: Modeling a FET requires a detailed understanding of its physical operation and an accurate representation of its behavior. This work shows different approaches to FET device modeling, including analytical models, semi-empirical models, and physics-based models. Each approach has its own advantages and disadvantages.

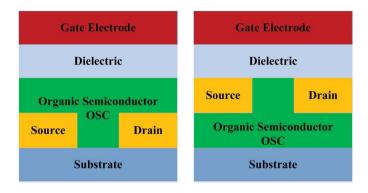

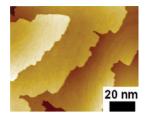

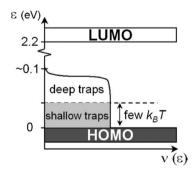

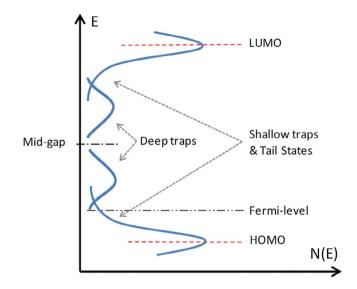

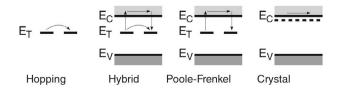

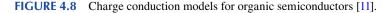

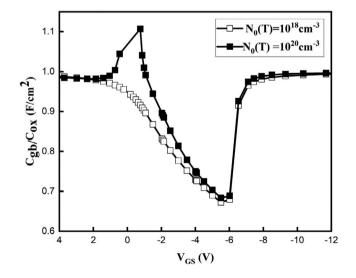

*Chapter 4*: Organic transistors can be fabricated on flexible substrates, resulting in flexible electronic applications that cannot be achieved with conventional silicon-based transistors. Along with this, trap states and mathematical modeling are explained in detail throughout the organic material structure as deep and shallow traps. The current–voltage equation has been reviewed to discuss the effect of trap parameters on the performance metrics of the device. The trap states affect the device capacitance and add a brief hump of short duration due to trap capacitance.

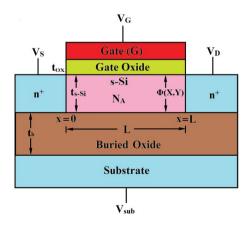

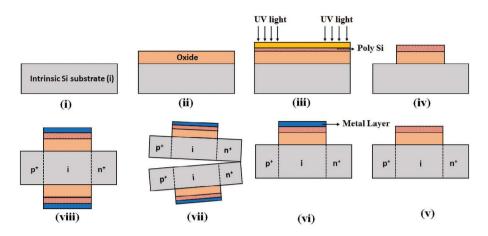

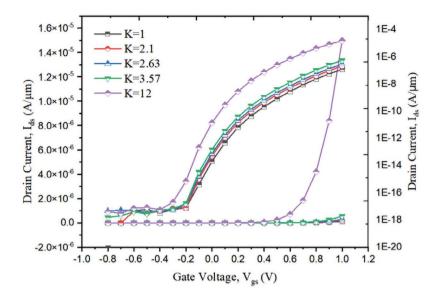

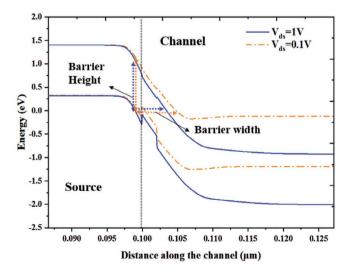

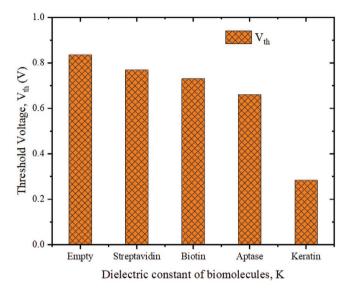

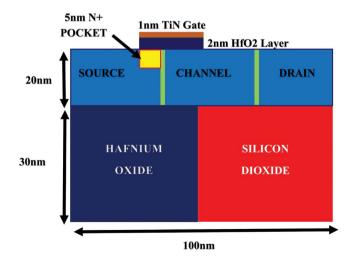

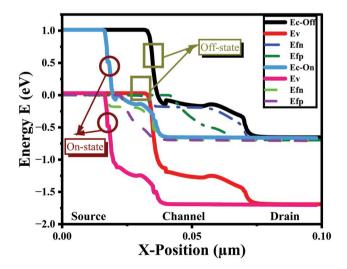

*Chapter 5*: This chapter discusses the basic TFET architecture and its operation using the concepts of energy band diagrams. ON- and OFF-states of the device are explained by adding their band diagrams to help readers grasp an understanding of tunneling junction and barrier width. Various simulation, fabrication, and noise-related challenges and issues are addressed in this chapter. A detailed analysis of a TFET-based biosensor is presented.

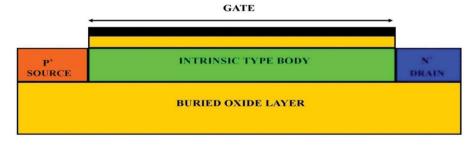

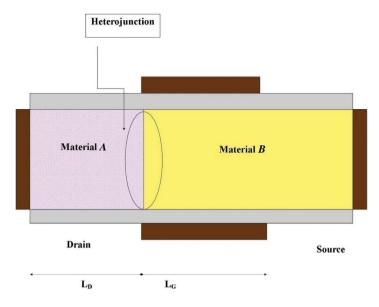

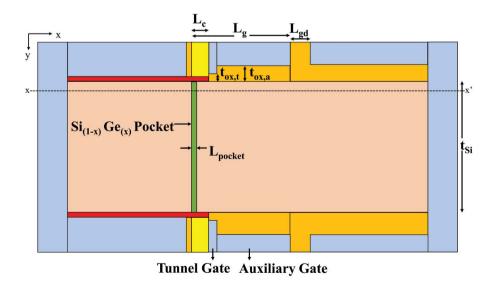

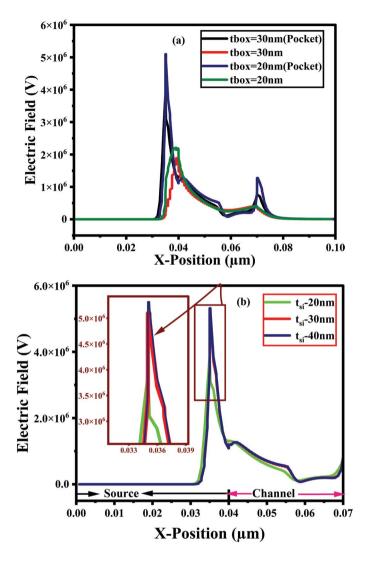

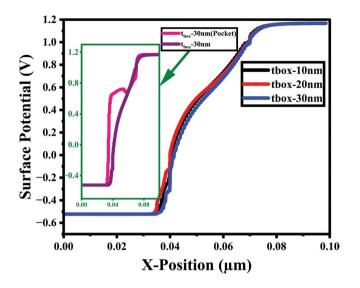

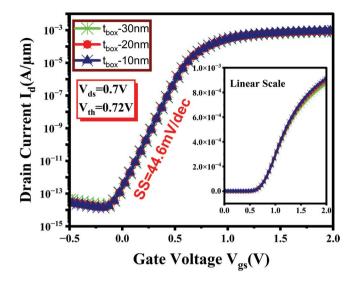

*Chapter 6*: This chapter includes an investigation of hetero buried oxide (HBOX) doped-pocket gate-engineered TFET structures. The low-K and high-K oxide layers that are present in the buried oxide layer at the drain and source terminals of TFETs boost the ON-state current and cause the ambipolar current to recede by varying different parameters such as HBOX and silicon thickness. HBOX-TFET performance is analyzed for direct current (DC) and analog/radiofrequency (RF) performance. The exceptional parameters extracted by the proposed HBOX-TFET prove its applicability for low-power DC and analog/RF applications.

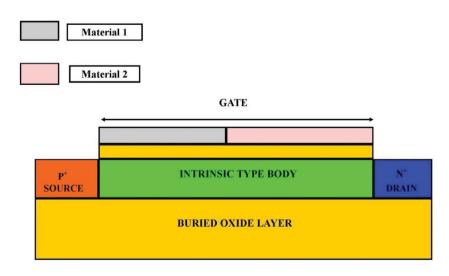

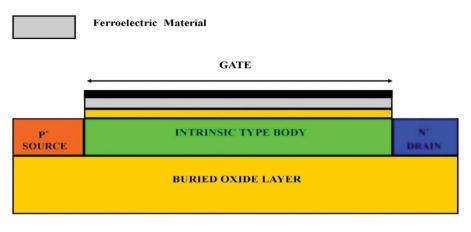

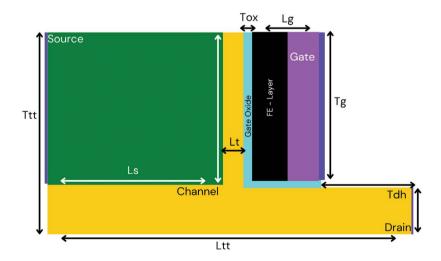

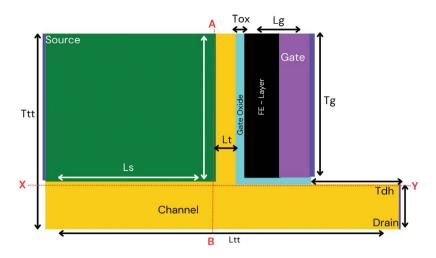

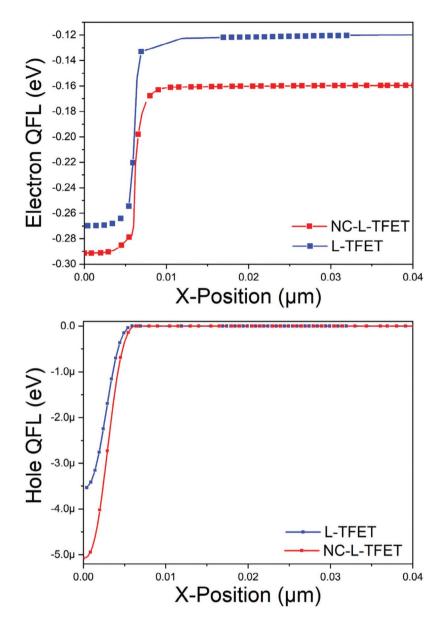

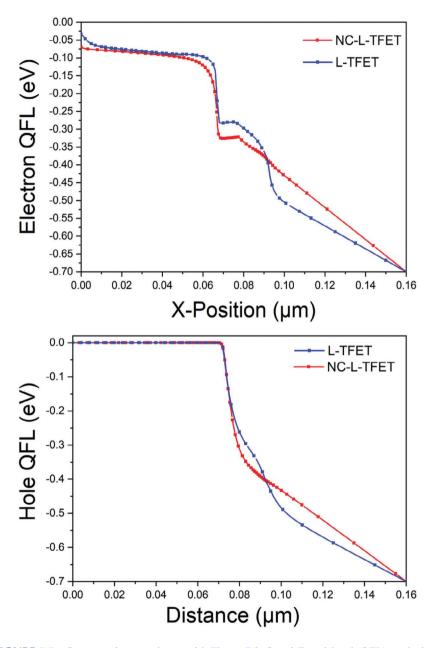

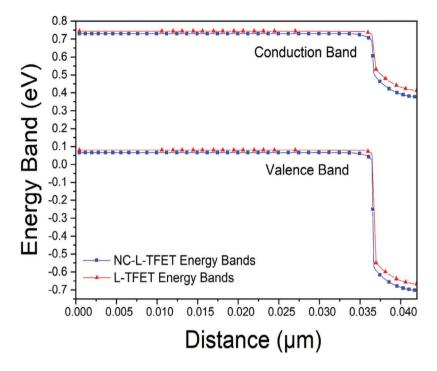

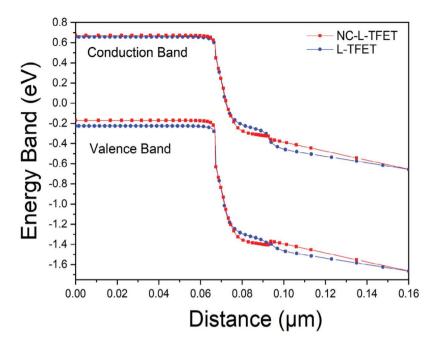

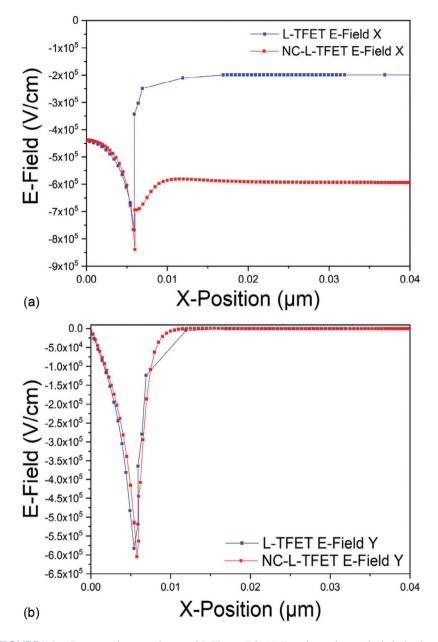

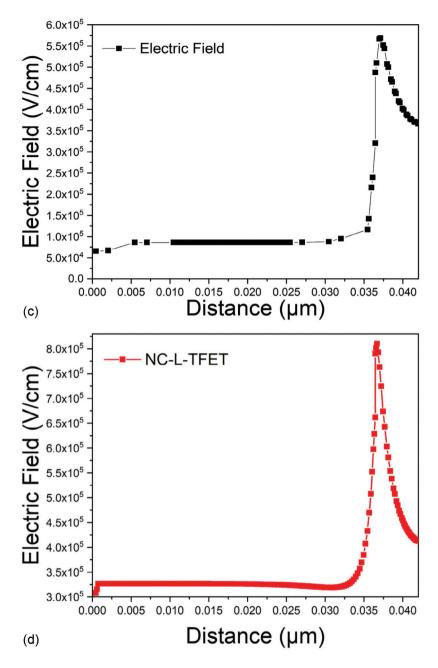

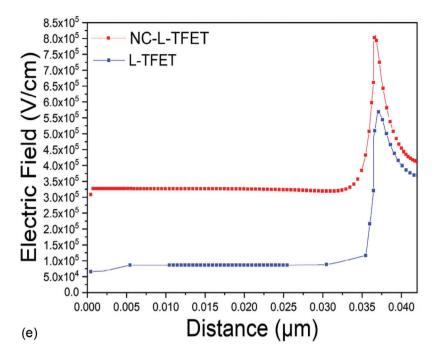

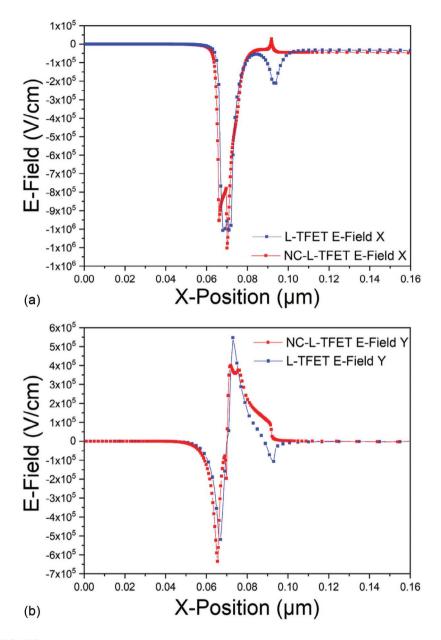

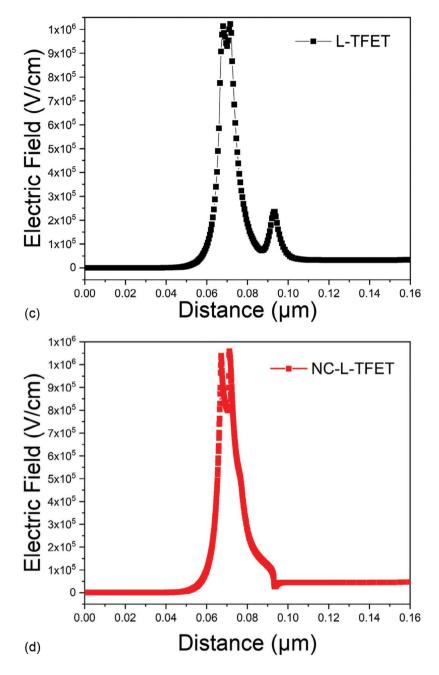

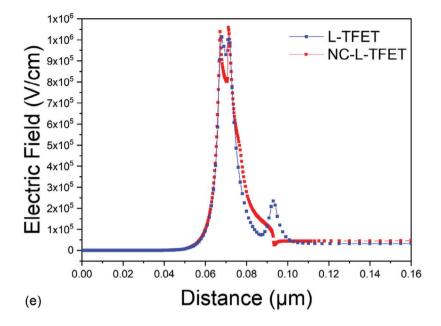

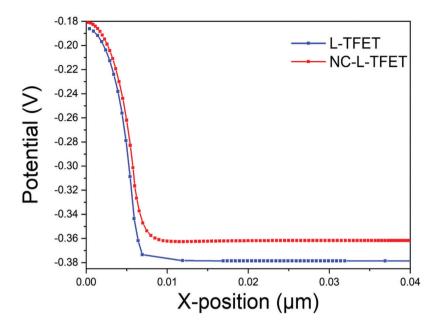

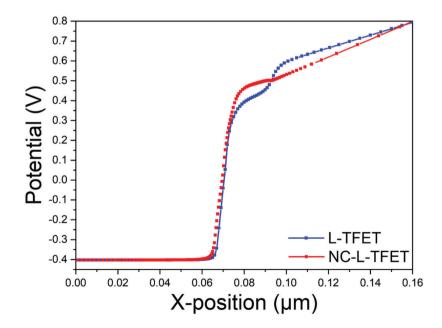

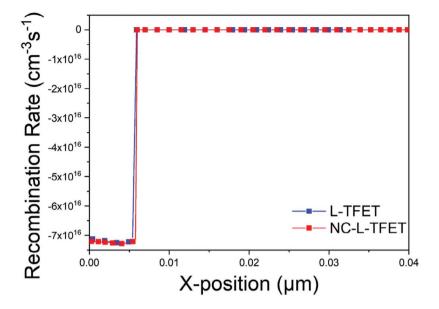

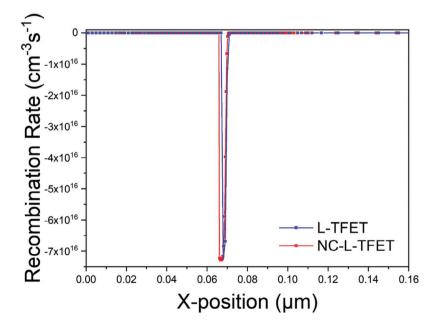

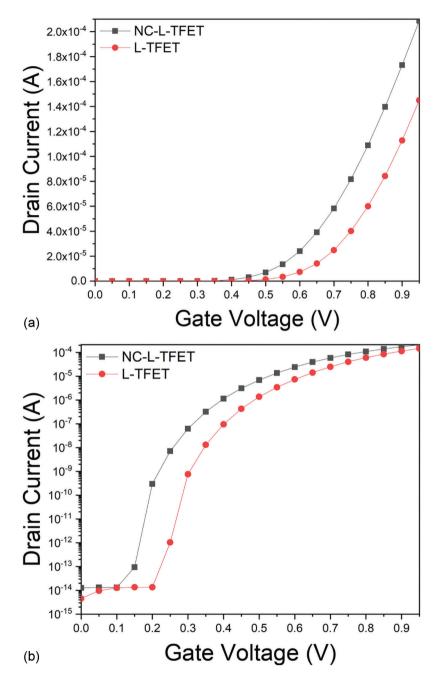

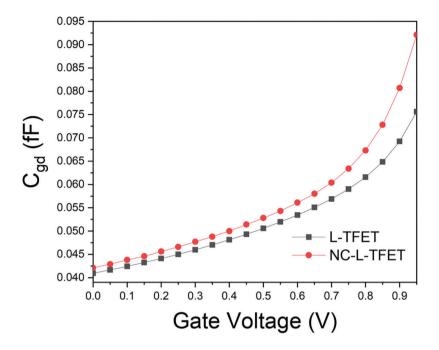

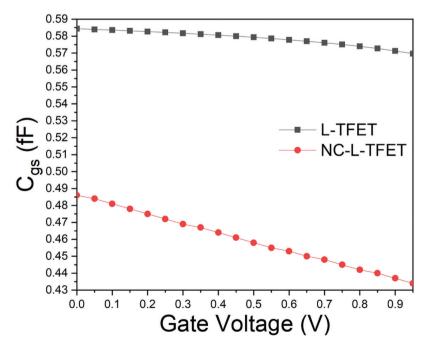

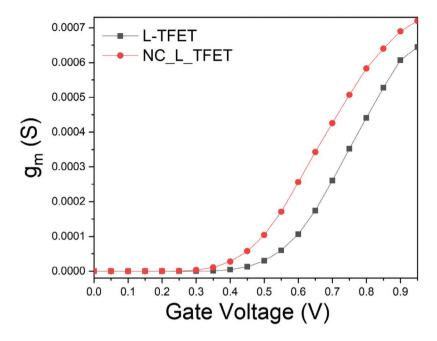

*Chapter 7*: This chapter consists of a brief history of transistors and how they evolved, and it introduces ferroelectric materials and their properties. The addition of a ferroelectric substance to a traditional L-shaped TFET (L-TFET) and its impact are analyzed through the characteristics of the proposed device. The proposed device, a negative-capacitance L-TFET (NC-L-TFET), is compared with L-TFETs in terms of various parameters.

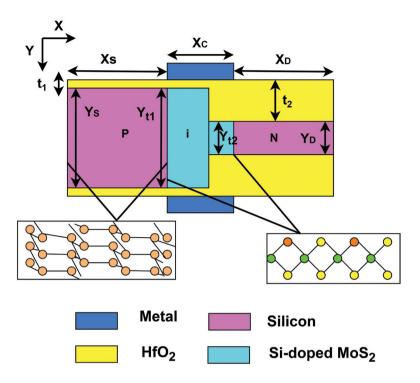

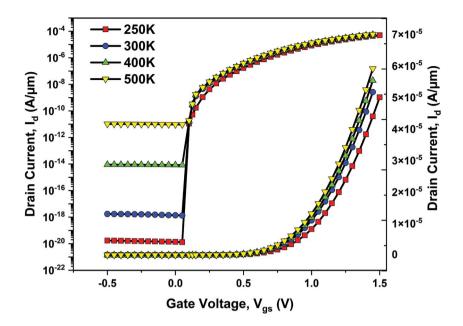

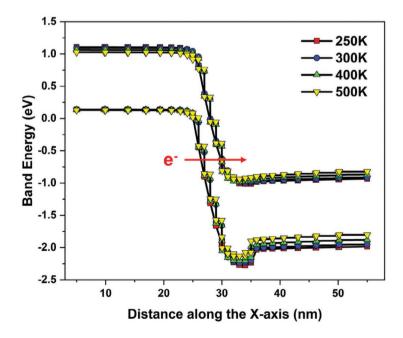

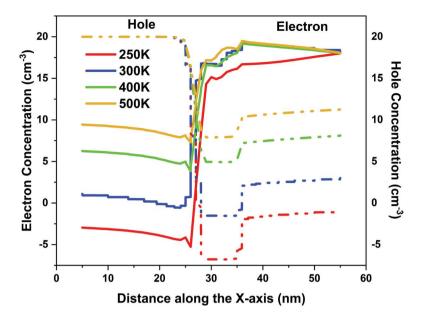

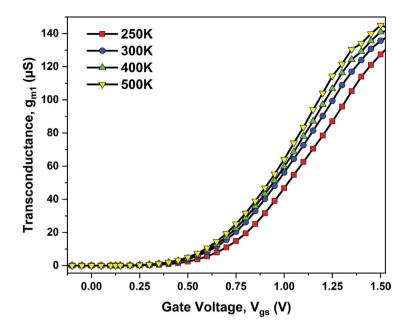

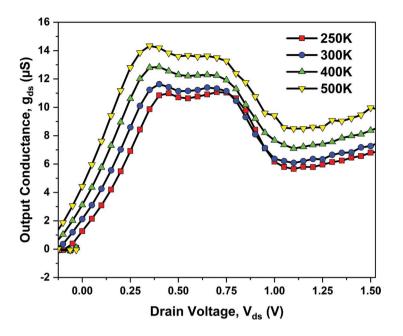

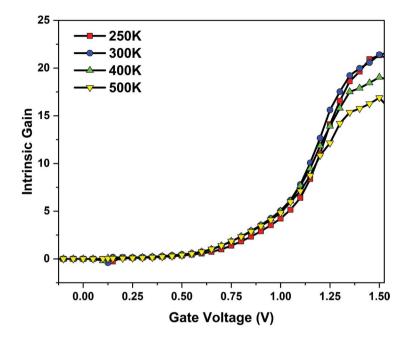

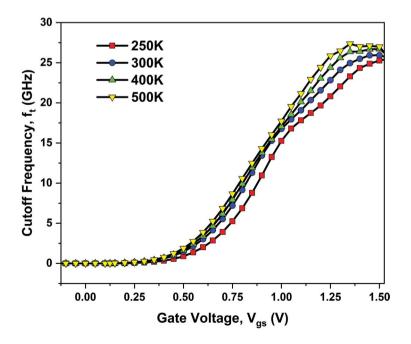

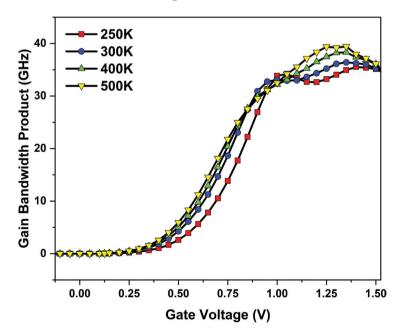

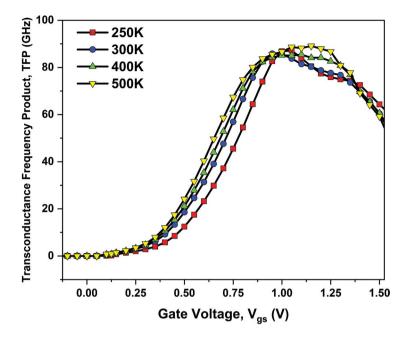

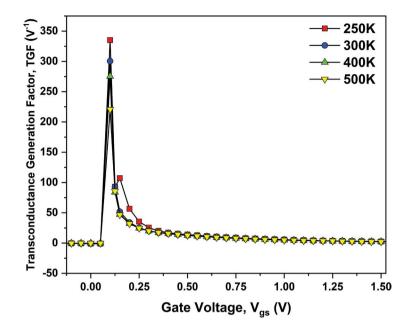

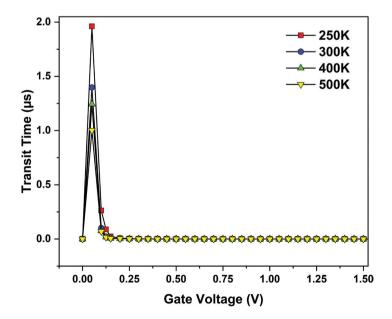

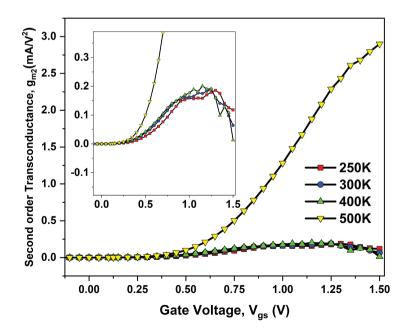

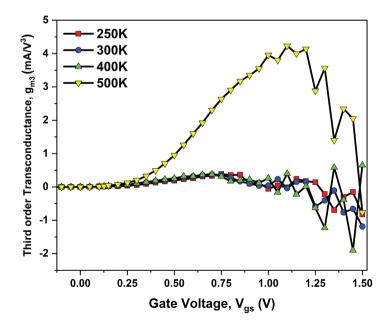

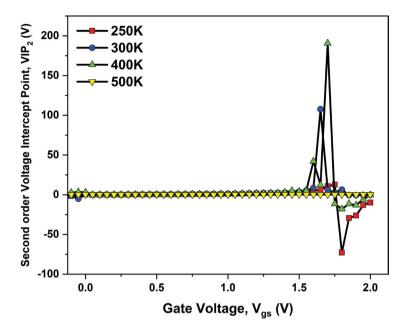

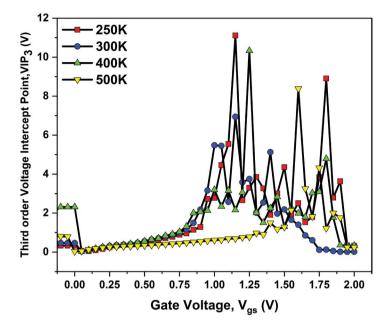

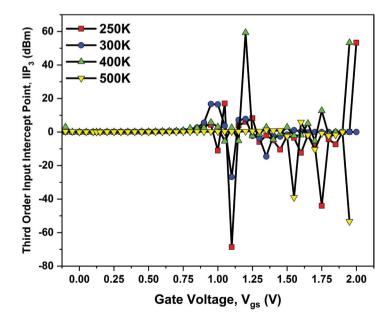

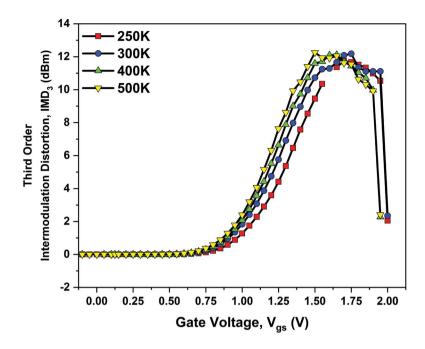

*Chapter* 8: In this chapter, a Si-doped  $MoS_2$ -based step-structure doublegate TFET ( $MoS_2$ -SS-DG-TFET) with a wide variety of properties is examined. To enhance device performance, this device uses a low dielectric thickness at the source–channel junction. The  $MoS_2$  material has a special property: Its energy gap varies with the number of material layers. Using this varied number of layers causes a small energy gap at the source side that improves ON-current and a large energy gap at the drain side that minimizes OFF-current. The suggested device can be employed for high-temperature applications, as evidenced by the fluctuation in DC and analog characteristics. In the TCAD simulator, temperatures between 250 K and 500 K have been examined to measure the device's performance.

*Chapter 9*: In this chapter, compact implementation of logic gates for digital applications using a step-channel TFET (SCTFET) is presented. OR, AND, NOR, and NAND logic gates are implemented by optimizing the gate work function and utilizing the gate-to-source overlap approach. The gate-to-source overlap method is used to implement the AND and NOR logic functions.

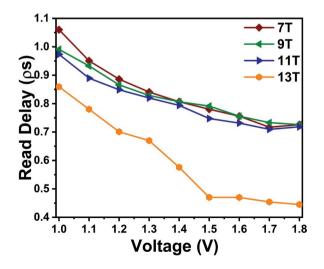

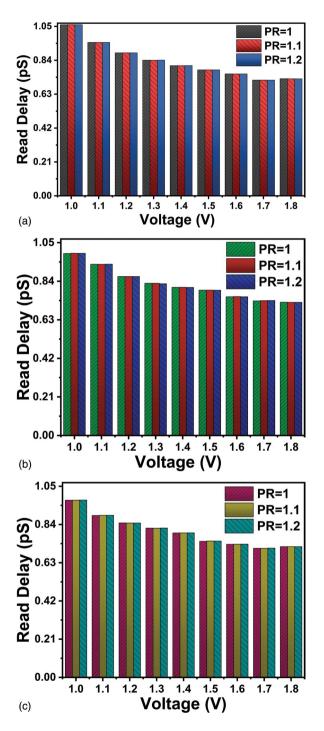

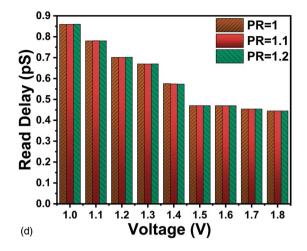

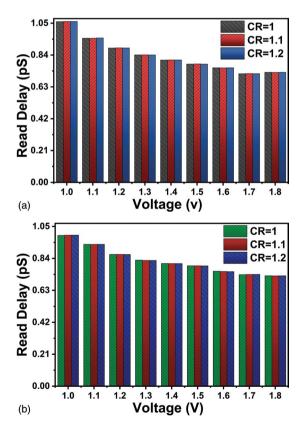

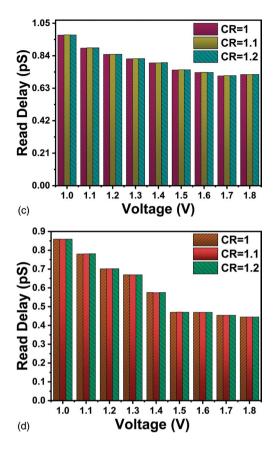

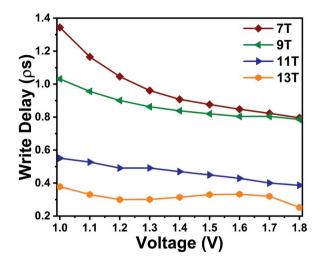

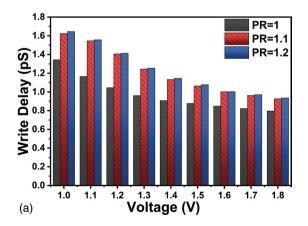

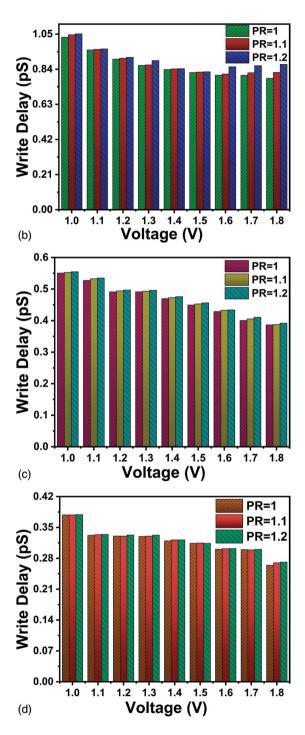

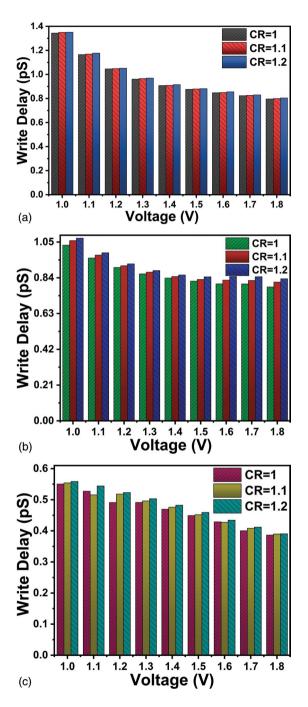

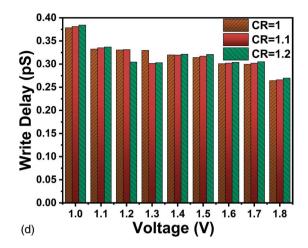

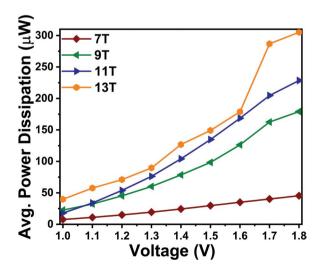

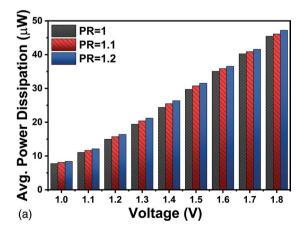

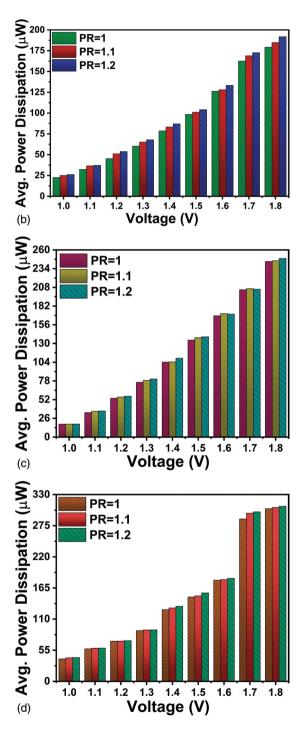

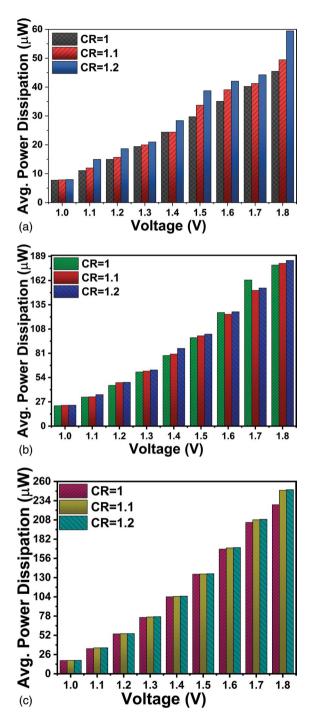

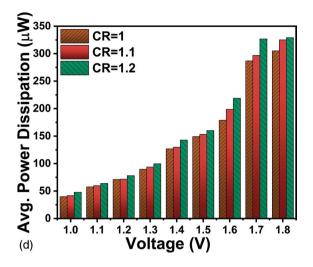

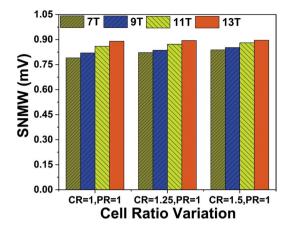

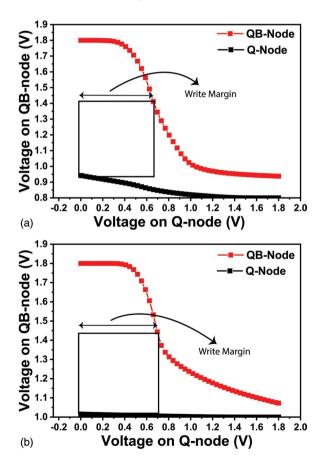

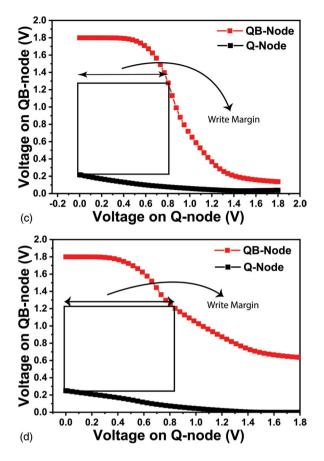

*Chapter 10*: In order to design an effective static random-access memory (SRAM) cell, this chapter provides in-depth research on several SRAM characteristics, including read delay, write delay, read stability, and write stability, of the circuit that is to be designed. Along with these parameters are others like delays, average power dissipation, and stability via changing the cell ratio, the pullup ratio, and different supply voltages. For this, 7T to 13T SRAM (odd numbers of transistors) was investigated to accomplish the improved static noise margin.

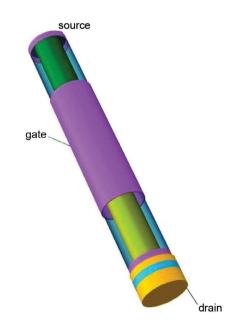

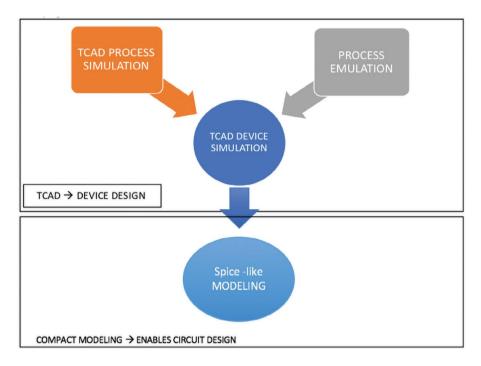

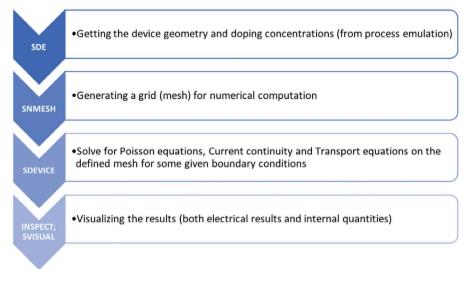

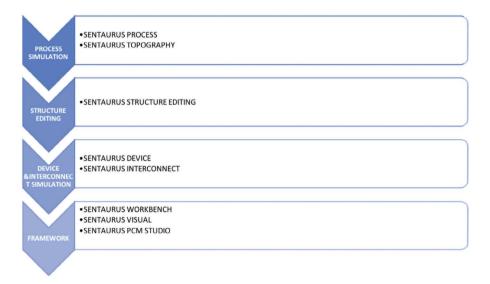

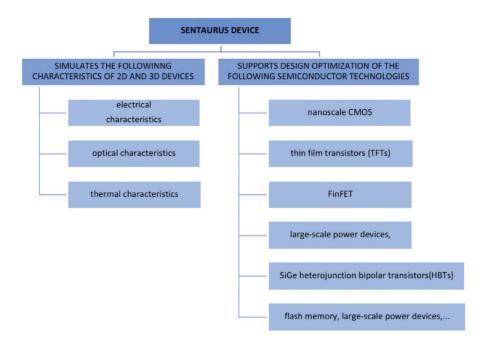

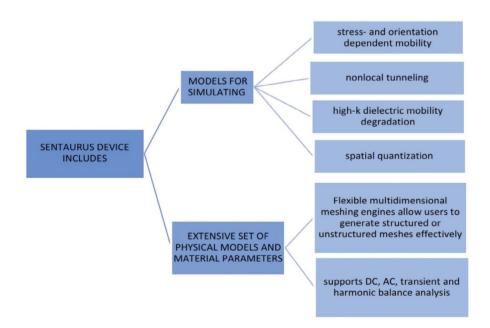

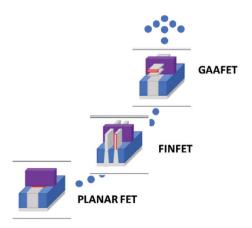

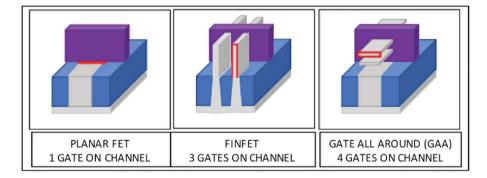

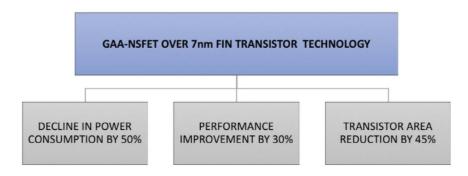

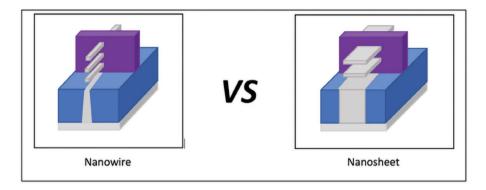

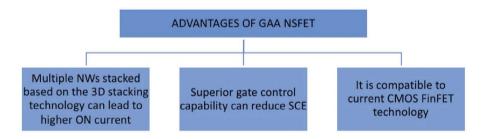

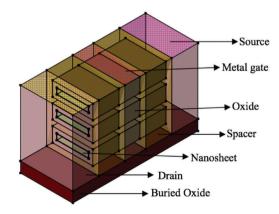

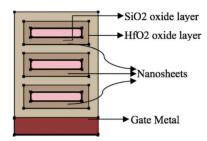

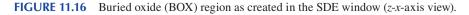

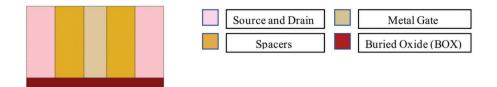

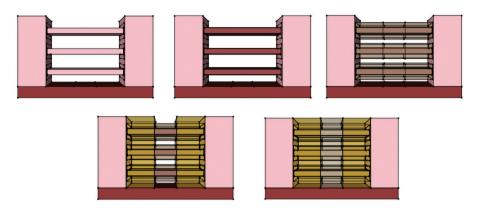

*Chapter 11*: A detailed overview of the Synopsys TCAD software suite (Sentaurus Structure Editor, SDevice, SVisual, and Inspect) is briefly discussed in this chapter. In later sections of the chapter, a novel, vertically stacked, gate-all-around nanosheet field-effect transistor (GAA-NSFET) is designed and simulated. The GAA-NSFET structure enables us to continue metal–oxide–semiconductor field-effect transistor (MOSFET) scaling beyond 10 nm and proves to be a better alternative for the substitution of fin field-effect transistors (FinFETs). The GAA-NSFET structure consists of several stacked channels, thus effectively improving the  $I_{ON}$  (ON-state current) and output characteristics of a MOSFET.

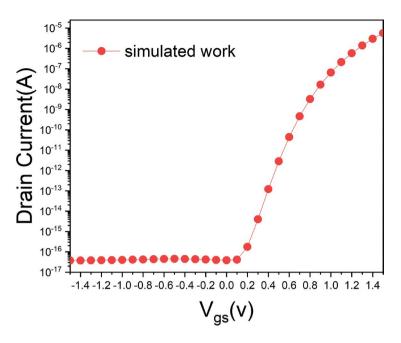

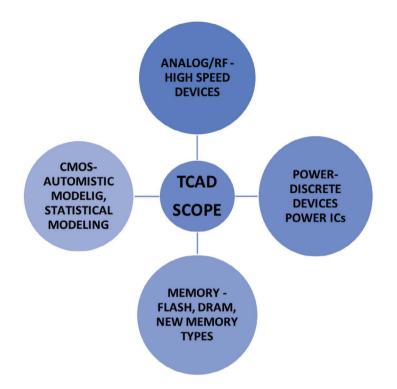

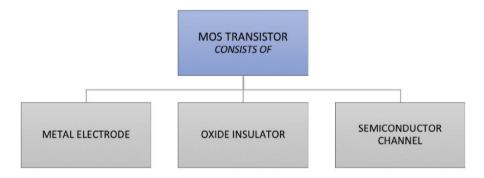

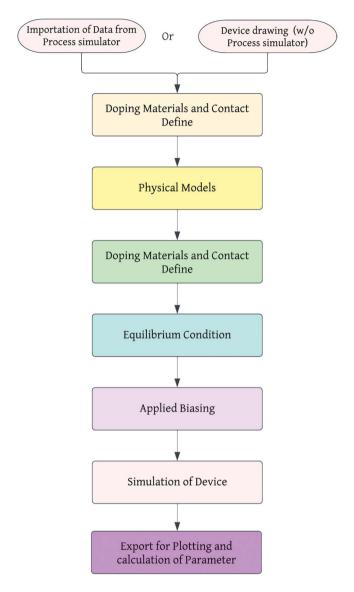

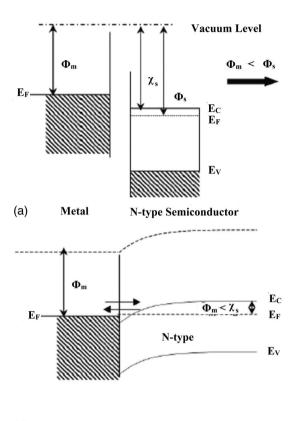

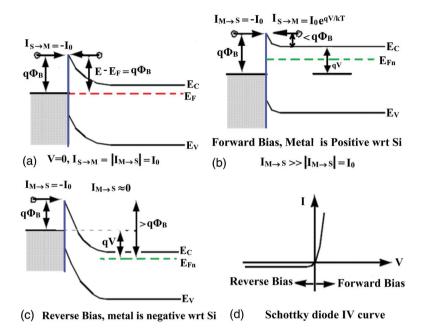

*Chapter 12*: This chapter provides a detailed explanation of basic simulation steps of TCAD tools. This includes basic information on device structure definition, mesh generation, material property assignment, simulation setup, simulation execution, postprocessing, and visualization. Finally, the simulation results are compared to experimental data to validate the accuracy of the simulation. A conventional silicon MOSFET has been designed using a Cogenda TCAD simulator tool to understand the TCAD simulation process.

We believe that learners, researchers, and training engineers in the industry will find this book beneficial.

#### THANKS TO THE CHAPTER AUTHORS

We extend our heartfelt thanks to all the chapter authors for their contributions and diligent work in this book. When the chance arose to begin writing this book on TFET technology, all writers agreed that now was the opportune moment to look back on the previous decade's research on TFETs as well as compile the most recent findings. With this in mind, the respective authors dedicated their time to produce a thorough, comprehensive, and informative new book for sharing and distributing information.

# **Editors Biography**

**Dharmendra Singh Yadav** received his PhD in electronics and communication engineering from the PDPM-Indian Institute of Information Technology, Design and Manufacturing, Jabalpur, India. He is currently working as assistant professor (Grade-I) at the National Institute of Technology (NIT), Kurukshetra, Haryana, India. He has more than 60 international publications in reputed journals and four book chapters. His current research interests include

- Very large-scale integration (VLSI) design: nanoelectronics devices, thinfilm transistors, semiconductor devices, negative capacitance, nanosheet FETS, and circuits.

- Device modeling: MOS device modeling and numerical simulation, analysis of semiconductor devices, and electrical characterization of semiconductor devices in MHz and THz frequency ranges.

- Circuit design: ultra-low-power SRAM/DRAM/RRAM-based memory circuit design from devices to array architecture using CMOS and advanced CMOS device technologies

- Machine learning in semiconductor device/circuit-based applications in research.

Shiromani Balmukund Rahi received his PhD from the Indian Institute of Technology Kanpur, Uttar Pradesh, and did his postdoctoral research work at the Electronics Department, University Mostefa Benboulaid of Batna, Algeria and Korea Military Academy Seoul, Republic of Korea. He is working at University School of Information and Communication Technology Gautam Buddha University Greater Noida, Uttar Pradesh, India. He has published 25 journal articles, 18 book chapters and 2 proceedings. He has edited successfully 7 books. He is also associated for advanced research work at

the Indian Institute of Technology Kanpur and the Electronics Department of the University Mostefa Benboulaid for the development of ultra-low-power devices such as TFETs, negative-capacitance (NC) TFETs, and nanosheet FETs.

**Sukeshni Tirkey** received her PhD in electronics and communication engineering from the PDPM-Indian Institute of Information Technology, Design and Manufacturing, Jabalpur, India. She is currently working at the Maulana Azad National Institute of Technology (MANIT), Bhopal, Madhya Pradesh, India. She has more than 20 international publications in reputed journals and conference proceedings. Her current research interests include VLSI design, nanoelectronics devices, thin-film transistors, semiconductor devices, negative capacitance, nanosheet FETS, and circuits.

# Contributors

#### Farkhanda Ana

Baba Ghulam Shah Badshah University Rajouri, Jammu and Kashmir, India

#### R.K. Baghel

Department of Electronics and Communication Engineering Maulana Azad National Institute of Technology (MANIT) Bhopal, Madhya Pradesh, India

#### Varun Bharti

National Institute of Technology Hamirpur, Himachal Pradesh, India

#### **Brinda Bhowmick**

National Institute of Technology Silchar, Assam, India

#### **Bharat Singh Choudhary**

Department of Electronics and Communication Engineering Maulana Azad National Institute of Technology (MANIT) Bhopal, Madhya Pradesh, India

#### Vibhash Choudhary

Department of Electronics and Communication Engineering National Institute of Technology Hamirpur, Himachal Pradesh, India

#### Priyanka Goma

Department of Electronics and Communication Engineering National Institute of Technology Hamirpur, Himachal Pradesh, India

#### Yuvraj Kadale

National Institute of Technology Hamirpur, Himachal Pradesh, India

#### Priya Kaushal

Department of Electronics and Communication Engineering National Institute of Technology Hamirpur, Himachal Pradesh, India

#### Gargi Khanna

Department of Electronics and Communication Engineering National Institute of Technology Hamirpur, Himachal Pradesh, India

#### Mamta Khosla

National Institute of Technology Jalandhar, Punjab, India

#### Haider Mehraj

Baba Ghulam Shah Badshah University Rajouri, Jammu and Kashmir, India

#### Sirisha Meriga

National Institute of Technology Silchar, Assam, India

#### Archana Pandey

Jaypee Institute of Information Technology Noida, Uttar Pradesh, India

#### G. Boopathi Raja

Velalar College of Engineering and Technology Erode, Tamil Nadu, India

#### Shiromani Balmukund Rahi

University School of Information and Communication Technology Gautam Buddha University Greater Noida, Uttar Pradesh India

#### Ashish Raman National Institute of Technology Jalandhar, Punjab, India

#### Ashwani K. Rana

Department of Electronics and Communication Engineering National Institute of Technology Hamirpur, Himachal Pradesh, India

#### Soumya Sen

National Institute of Technology Jalandhar, Punjab, India

#### **Abhay Pratap Singh**

Department of Electronics and Communication Engineering Maulana Azad National Institute of Technology (MANIT) Bhopal, Madhya Pradesh, India

#### Anushka Singh

Jaypee Institute of Information Technology Noida, Uttar Pradesh, India

#### **Prabhat Singh**

Department of Electronics and Communication Engineering National Institute of Technology Hamirpur, Hamirpur, India

#### Sukeshni Tirkey

Department of Electronics and Communication Engineering Maulana Azad National Institute of Technology (MANIT) Bhopal, Madhya Pradesh, India

#### Najeeb-Ud-Din

National Institute of Technology Srinagar, Jammu and Kashmir, India

#### **Dharmendra Singh Yadav**

Department of Electronics and Communication Engineering National Institute of Technology Kurukshetra, Haryana, India

# 1 Future Prospective Beyond-CMOS Technology From Silicon-Based Devices to Alternate Devices

G. Boopathi Raja

#### 1.1 INTRODUCTION

Manufacturing integrated circuits often involves the use of complementary metaloxide-semiconductor (CMOS) technology as the primary technology. The CMOS technique is used in a wide variety of electronic components, including microcontrollers, batteries, and digital sensors, because of the many significant benefits that it offers. In order to implement a wide variety of logic operations, this technology makes use of both the N and P MOSFET channels (NMOS and PMOS, respectively), which are both intended to have matching qualities when they are developed.

Before CMOS logic came along, PMOS and NMOS logic were the most common ways to build logic gates. Eventually, the NMOS technology, which had been the industry standard for making integrated circuits, took over from the PMOS technology. CMOS started off being a slower and more costly option than NMOS. The primary benefits of NMOS technology are its straightforward physical process, high functional density, lightning-fast processing speed, and cost-effective production. Electrical asymmetry and the loss of static power are two of the most significant drawbacks associated with NMOS technology. Utilizing CMOS technology helps to reduce the impact of these limitations. The fact that power loss is only ever experienced during the switching of circuits is the primary benefit offered by CMOS technology. This results in significantly improved performance, since it makes it possible to integrate a greater number of CMOS gates into an integrated circuit.

Based on the 2001 edition of *The International Technology Roadmap for Semiconductors*(ITRS), which showed how quickly metal–oxide–semiconductor field-effect transistor (MOSFET) technology was getting better, several new technologies have been developed to expand CMOS into nanoscale MOSFET architectures. In 2023, the semiconductor industry will concentrate on lithography and advanced process nodes. Major semiconductor companies might introduce 3nm and 5nm nodes to increase the density and efficacy of transistors. These developments will facilitate the development of processing units, memory modules, and SoCs. The packaging innovations allow for miniaturization and integration, resulting in more efficient and compact devices. There is a growing hope that, with the help of these new technologies, it will be possible to expand MOSFETs to the 22-nm node (which corresponds to a 9-nm physical gate length) by the year 2016, if not before. There will almost certainly be some new, innovative materials in these new devices. New MOSFET topologies that do not need bulk materials have been skillfully crafted using these materials. They will have a ravenous desire for power and be exceedingly quick and dense at the same time. There is a possibility that intrinsic device velocities may be more than 1 THz, and there is also a possibility that integration densities could be greater than 1 billion transistors per square centimeter. However, due to their high power consumption, these high-performance devices ought to be used only in critical pathways where their enhanced performance is required. The roadmap for semiconductors will emphasize energy management and efficiency. Modern electronics contend with heat production and energy usage. Dynamic frequency and adaptive voltage scaling increase energy efficiency and battery lifespan. It is possible to minimize the total power consumption of the device by using two or even three extra MOSFETs that have lesser performance but greater power efficiency. These MOSFETs might be utilized to carry out functions that are less performance-critical.

In addition to CMOS, fundamentally new technologies as well as architectural designs are now being developed for the processing and storage of data in the future. Rather than attempting to "replace" CMOS, a few of these new ideas, when paired with a CMOS platform, could make it possible to employ microelectronics in methods that are not feasible with CMOS on its own. A new technique of processing information that is successful will almost surely need an alternative platform technology. It comprises a fabric of connected primitive logic cells, maybe in three dimensions. This is because the old method of processing information was inefficient. This new logic paradigm might also recommend an updated information-processing architecture that is consistent with the logic fabric and that makes the most of the capabilities of the logic fabric. The Information Society Technology Project of the European Commission developed the *Technological Roadmap for Nanoelectronics*. It gives a good description of nanoelectronics devices (emerging technologies).

"Beyond CMOS" refers to improvements in digital logic that are expected to come in the future and go beyond the scaling limits set by CMOS. These limitations are intended to minimize heat impacts by restricting the speed and intensity of the device. Digital logic is necessary for the creation of electronic and logical devices. It enables us to perform activities critical to the success of a system, such as designing circuits and testing computer chips. CMOS is the acronym for complementary metal–oxide–semiconductors, which are the standard on-and-off switches in modern semiconductor products [1].

In other words, "beyond CMOS" refers to new technologies in digital logic or emerging technologies in general that are used to explain the events and signals in a digital circuit. It is expected that these technologies would get around the scaling problems caused by CMOS [2, 3]. It has already been surpassed by an order of magnitude for feature size and by two orders of magnitude for speed [4, 5].

Moore's law will be partially met by new materials, architectures, devices, and topologies that will be developed over time and referred to as "beyondCMOS." One

illustration of this is the speculation that the 32-nm CMOS integrated circuit will be developed by the year 2020. Its primary purpose is to operate as a supplement to the CMOS technology that is now in use, enabling the production of circuits with a greater switching capacity and an improvement in the information storage capacity of such devices. This is necessary since the CMOS technology that is currently in use will not be able to surpass certain capacity constraints.

Experts say that beyond-CMOS technology will eventually replace silicon because the electrical properties of graphene are better than silicon's physical limits. BeyondCMOS is looking into new technologies like nanostructures made of carbon nanotubes (CNTs) and spintronics, which send information using the charge and spin of electrons.

The following are the primary motivations for launching beyond-CMOS research and development:

- When the amount of power used goes up, the speed at which the circuit works doesn't go up enough to keep up.

- Because of the increase in power, there will also be a rise in the temperature of the gadget, which will harm its functionality.

- An increase in the number of faults at both the lithography and design levels. This is because, when dealing with such tiny scales, it is quite simple to make mistakes in either the printing or the circuit design.

The following is the chapter's organizational structure: Section 2 discusses the various alternatives to beyond-CMOS technology that are based on previous semiconductor technologies. Section 3 elaborates on the role of industries and researchers in the advancement of beyond-CMOS technology. Sections 4 and 5 discuss applications of beyond-CMOS technology and alternatives to CMOS electronics. Section 6 explains futuristic gadgets that use beyond-CMOS technology. Section 7 summarizes, in the conclusion, the important key features of technology beyond CMOS.

### 1.2 BEYOND-CMOS TECHNOLOGY FROM EXISTING AND PAST SEMICONDUCTOR TECHNOLOGIES

"Beyond CMOS" refers to the computer logic techniques. It may be created in the future, and it will be able to scale beyond the CMOS scaling constraints. It will restrict the density and speed of devices since they heat up. Beyond-CMOS technologies will be capable to scale beyond the CMOS scaling limits.

The International Technology Roadmap for Semiconductors (ITRS) 2.0 was indeed a significant document in the semiconductor industry, published in 2013 as a continuation of the original ITRS roadmap. It aimed to provide guidance and predictions for the future development of semiconductor technology. However, ITRS 2.0 was succeeded by the International Roadmap for Devices and Systems (IRDS) in 2017. Within ITRS 2.0 (2013) and its successor, the *International Roadmap for Devices and Systems*(IRDS), there are a total of seven focus groups, and one of them is called Beyond CMOS. It is focused on exploring and defining technologies and devices that go beyond conventional Complementary Metal-Oxide-Semiconductor

(CMOS) technology. CMOS technology has been the basis of semiconductor manufacturing for several decades, but as it approaches its physical limits, the industry is researching and developing new technologies to continue advancing the field.

The Beyond CMOS focus group within IRDS is tasked with assessing and guiding the development of emerging technologies that can potentially replace or complement CMOS technology as it becomes increasingly challenging to scale down. This includes exploring novel materials, devices, and architectures that could pave the way for the next generation of semiconductor technology.

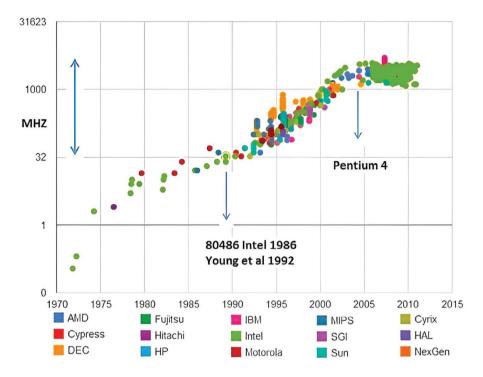

Central processing unit (CPU) clock scaling: Computers with CMOS processors (like the 12 MHz Intel 80386) were first sold to the public in 1986. The clock speeds of CMOS transistors increased in tandem with their dimensions being reduced. The clock speeds of CMOS CPUs have remained stable at approximately 3.5 GHz since approximately 2004.

A comparison of the efficiency gains that could be made with "more Moore" (i.e., more improvements to the current technology) and "beyond CMOS": The following is an excerpt from the IRDS. CMOS device sizes are continuing to shrink; for examples, see Intel Tick-Tock and ITRS: Ivy Bridge at 22 nm was released in 2012, and the first processors at 14 nm were distributed in the fourth quarter of 2014.

Samsung Electronics displayed a 300-mm wafer of 10-nm fin field-effect transistor (FinFET) chips in May 2015. Beyond-CMOS research and development focuses on the extension of integrated circuit technology to truly innovative methodologies in order to construct the optimal paths for technological breakthroughs far beyond the conclusion of CMOS dimensional scaling. Even though semiconductor technology has changed a lot over the years, other technologies that are based on research have also changed a lot.

The primary objective of this chapter is to survey, evaluate, and classify promising new technologies in terms of their long-term viability and technological maturity. This chapter also talks about the scientific and technical problems that keep the semiconductor industry from using them. These problems are seen as acceptable risks for future development. Researchers are developing both nonvolatile as well as volatile memory technologies in an attempt to replace static random-access memory (SRAM) and FLASH in the appropriate applications. Due to present scaling limitations, it is essential to obtain electrically accessible memories that are:

- Embeddable

- · Low power

- · High density

- · High speed

- Possibly nonvolatile

The sizes of modern memory systems vary substantially. Some, especially mobile systems, might be sufficiently small to be gigabyte-based, whereas others might need some extra bytes of storage. Regardless of system size, the issue is the same: The majority of computer systems seldom run at peak demand. Even with modest consumption rates, modern data servers still need a great deal of power.

These kinds of difficulties highlight the potential usefulness of permanent memory. If this capability did not need to be renewed regularly, the operating strain on logic devices could be greatly reduced. Refresh power may use as much as one-third of the energy required by a large computer system; if this power were made available, customers might use it to operate devices that are far faster and more powerful.

#### 1.2.1 MOORE'S LAW

Gordon E. Moore, the cofounder of Intel, hypothesized in 1965 that the total amount of transistors that could be crammed into a given volume would approximately double every two years. This prediction was based on the fact that transistors are used in electronic circuits.

Gordon E. Moore did not refer to his observation as "Moore's law," and neither did he set out to produce a "law" when he remarked. Moore based his comment on observations he made at Fairchild Semiconductor, where he worked, on future trends in the manufacture of chips. Moore's observation was eventually turned into a prediction, which led to the idea that became known as Moore's law [5].

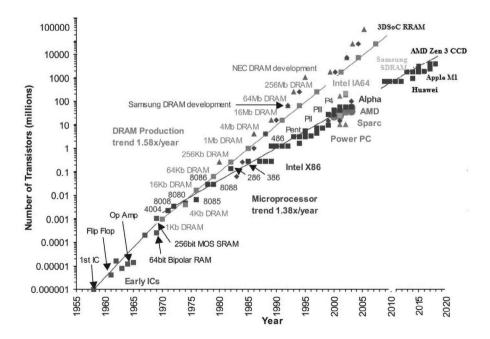

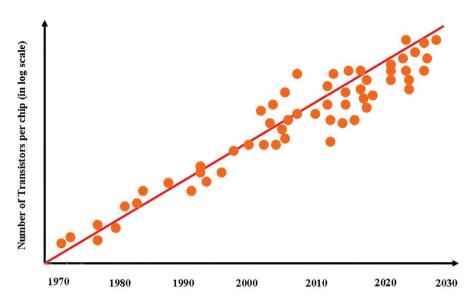

Moore's law states that the number of transistors on a microchip may double every two years. The law ensures that computer speed and capacity will continue to improve at a rate of 100% every two years, while their costs will fall. The second rule of Moore's law states that this growth is happening at an exponential rate. Gordon Moore, who helped build Intel and was once the CEO of the company, is credited with coming up with the idea for the law. Figure 1.1 shows the evolution of Moore's law.

#### 1.2.2 OPINION OF THE IRDS<sup>TM</sup> ON BEYOND CMOS

The goal of the IRDS<sup>TM</sup> is to find beyond-CMOS devices that will help make possible new ways of using computers that go far beyond what is possible with traditional CMOS designs and technology. The Beyond CMOS focus group of the IRDS<sup>TM</sup> was made with the specific goal of finding research opportunities, evaluating existing devices, and mapping future devices [6].

The IRDS<sup>TM</sup> Beyond CMOS section has several pillars on which its projects are built. New gadgets for cognitive processing, logic, and storage receive considerable attention in this chapter. The IRDS<sup>TM</sup> community has a strong interest in many emerging application domains. Elements of big data analytics, device security, and intelligent computing are discussed in this chapter.

The Beyond CMOS study found that the circuit, architect, and device groups are now trying to reach more than one goal. Coordinating the creation of new devices is very important if they want to make big steps forward in the field of computing.

While Moore's law and typical CMOS scaling are expected to continue for the next few years, the IRDS<sup>TM</sup> recognizes that we are fast nearing the limits of conventional scaling. Scaling as we know it will likely stop due to issues such as increasing pricing and fundamental physical effects. The roadmap admits that challenges such

FIGURE 1.1 Evolution of Moore's law.

as gate length (outside system connectivity) are one illustration of how statistical distributions and critical dimensions may impede CMOS scaling attempts.

The IRDS<sup>TM</sup> is designed to provide maximum performance with the lowest energy usage. As a consequence of recent advances and improvements in the technological sector, the emphasis has shifted toward new computing paradigms, capabilities, and applications. Several guiding principles for present and future beyond-CMOS research are stated in the roadmap.

- 1. Nanoscale thermal management

- 2. Nonthermal equilibrium systems

- 3. Computational state variable(s) other than solely electron charge

- 4. Sub-lithographic manufacturing process

- 5. Novel energy transfer interactions

- 6. Alternative architectures

#### 1.2.3 EVOLUTION OF CMOS AND BEYOND CMOS

Even though the performance of integrated circuits has been getting better and better over the past 30 years, CMOS technology has been around for much longer. Frank Wanlass came up with the method in 1963, but it didn't get much use until the 256 Kb CMOS dynamic random-access memory (DRAM) came out in 1984. Since then, CMOS technology has been a key part of the development of many digital circuits, including electronic parts, microcontrollers, embedded systems, sensors, memory, and many more.

Since the unfortunate discovery (made by Gordon Moore in 1965) that integrated circuit transistors quadruple every 18 months, a lot has changed. Researchers have put in a lot of work to find ways to deal with the problems that standard CMOS causes. High gate leakage currents, gate stack reliability, source-to-drain leakage, and channel mobility degradation have all played a big part in how CMOS has changed over time.

A new CMOS technology node (i.e., the advancement of CMOS technology at 32 nm and upwards) has developed about every 24 months during the past 15 years. Each node has its changes, which usually means that density goes down by 2% and performance goes up by 35% per node. Because of limits on power and the ability of chips to use more power, CMOS scaling has become a technology that focuses more on density. Figure 1.2 shows how the number of transistors used in CPUs and memory-integrated circuits has increased over time [7].

**FIGURE 1.2** Illustration of how the number of transistors in central processing units (CPUs) and memory-integrated circuits has grown over time [7].

Nonclassical CMOS structures include improved MOSFETs. Utilizing novel transistor structural designs provides the way for scaling CMOS within the timeframe of the 2001 *Roadmap*. This may be accomplished via the use of nonclassical CMOS structures. Nonclassical submissions include an ultrathin-body silicon-on-insulator (SOI), a band-designed transistor, and three double-gate architectures. These structural alterations are contrasted in Table 1.1, and also their implications are described.

#### 1.2.4 WHAT MAKES BEYOND-CMOS TECHNOLOGY FEASIBLE NOW?

It is important to keep in mind that a lot of beyond-CMOS technology can't be used in the real world right now. Commercially, specialized products are available, although beyond-CMOS capabilities are seldom used by the general population. It is now possible to work toward these capabilities [8].

This study on beyond CMOS is possible right now because of several factors, such as the need for it, external technological innovation and progress, and a very high level of adaptability [9, 10]. Scaling CMOS technology is rapidly losing its potential. Academicians and researchers from across the globe are driven to investigate these technologies due to the lack of alternatives [11–13].

The huge amount of work that has gone into making computers better over the past few decades has also made a big difference in how good they are now. Professional research organizations have a keen interest in resistive-switching electronics, magnetic devices, and a range of other technologies and capabilities that have been studied for a considerable amount of time.

Because the possibilities of beyond-CMOS technologies are so diverse, researchers have a lot of leeway in deciding where to focus their attention and efforts. This means that people who know a lot about circuits and designs, for example, can focus on them and give detailed feedback on development, while other groups can work on building nano- and microelectromechanical systems (NEMS and MEMS, respectively) or improving magnetic logic [14, 15].

Together, these factors, as well as the efforts of forward-thinking individuals and organizations that recognized the need for this technology, made it possible for us to begin developing beyond-CMOS technology. Research and development might stop moving forward if there weren't so many ways to go, so many specialties to choose from, and new ideas coming from outside the field.

"Beyond-CMOS technology" refers to the new materials, structures, devices, and architectures that will be made in the far future (when CMOS technology reaches its physical limits) and should be in used semiconductor industry by 2020. The main goal of this innovation is to work as a supplement to CMOS technology so that it is easier to make circuits with more space to store information.

Table 1.2 provides a review of the documented research efforts that have been made on numerous different memory technologies. As may be observed, current research initiatives are investigating a wide array of fundamental memory systems. These processes consist of charge retention by Coulomb blockade potential, charge retention by magnetic phenomena, surrounding dielectrics, chemical phenomena, and phase alterations in the material. Shortly, the majority of these memory options will likely be integrated into a CMOS-based technology platform. In the context of

### TABLE 1.1

### Nonclassical CMOS

| Device                            | Methodology                                                           | Application/<br>Driver                                                    | Advantages                                                                              | Scaling Issues                                                                                                                          | Design Challenges                                                                                    |

|-----------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Ultrathin-<br>Body SOI            | Fully depleted<br>SOI                                                 | <ul> <li>Higher<br/>performance</li> <li>Higher<br/>transistor</li> </ul> | <ul><li>Improved<br/>subthreshold slope</li><li>Vt controllability</li></ul>            | <ul><li>Si film thickness</li><li>Gate stack</li><li>Worse short-channel effect than bulk CMOS</li></ul>                                | <ul> <li>Device<br/>characterization</li> <li>Compact model and<br/>parameter extraction</li> </ul>  |

| Band-<br>Engineered<br>Transistor | SiGe or strained<br>Si channel<br>Bulk Si or SOI                      | <ul><li>density</li><li>Lower power dissipation</li></ul>                 | <ul> <li>Higher drive current</li> <li>Compatible with<br/>bulk and SOI CMOS</li> </ul> | <ul> <li>High-mobility film thickness, in case of SOI</li> <li>Gate stack</li> <li>Integration</li> </ul>                               | Device     characterization                                                                          |

| Vertical<br>Transistor            | Double-gate or<br>surround-gate<br>structure (no<br>specific temporal |                                                                           | Higher drive current     Lithography-     independent Lg                                | <ul> <li>Si film thickness</li> <li>Gate stack</li> <li>Integrability</li> <li>Process</li> </ul>                                       | <ul> <li>Device<br/>characterization</li> <li>PD versus FD</li> <li>Compact model and</li> </ul>     |

| FinFET                            | sequence for<br>these three<br>structures is<br>intended)             |                                                                           | <ul> <li>Higher drive current</li> <li>Improved<br/>subthreshold slope</li> </ul>       | <ul> <li>Accurate TCAD complexity, including QM effect</li> <li>Si film thickness</li> <li>Gate stack</li> <li>Integrability</li> </ul> | <ul> <li>parameter extraction</li> <li>Applicability to<br/>mixed-signal<br/>applications</li> </ul> |

| Double-Gate                       | _                                                                     |                                                                           | <ul> <li>Improved<br/>short-channel effect</li> <li>Stacked NAND</li> </ul>             | Process     Accurate TCAD complexity, including QM effect     Gate alignment                                                            | -                                                                                                    |

| Transistor                        |                                                                       |                                                                           | gate                                                                                    | <ul> <li>Gate stack</li> <li>Integrability</li> <li>Process</li> <li>Accurate TCAD complexity, including QM effect</li> </ul>           |                                                                                                      |

Note: CMOS: Complementary metal–oxide–semiconductor; FD: Fully Depleted; FinFet: Fin field-effect transistor; PD: Partially Depleted; QM: Quantum Mechanics; SOI: Silicon-on-insulator; TCAD: Technology CAD; Vt: Threshold Voltage.

### TABLE 1.2

### **Emerging Research Memory Devices**

| Storage Mechanism               | Device Types                                 | Availability | General Advantages                                                                                                                                                                                             | Challenges                                                                                   | Maturity     |

|---------------------------------|----------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------|

| Baseline 2002<br>Technologies   | DRAM                                         | 2002         | <ul><li>Density</li><li>Economy</li></ul>                                                                                                                                                                      | • Scaling                                                                                    | Production   |

|                                 | NOR FLASH                                    |              | Nonvolatile                                                                                                                                                                                                    |                                                                                              |              |

| Magnetic RAM                    | Pseudo-spin valve                            | 2004         | Nonvolatile                                                                                                                                                                                                    | Integration problems                                                                         | Development  |

|                                 | Magnetic tunnel junction                     |              | <ul> <li>Long-lasting</li> <li>Rapid reading and writing</li> <li>Hard radiation</li> <li>NDRO</li> </ul>                                                                                                      | <ul><li>Material quality</li><li>Magnetic property management for write operations</li></ul> |              |

| Phase-Change Memory             | OUM                                          | 2004         | <ul><li>Low power</li><li>Nonvolatile</li><li>NDRO</li><li>Hard radiation</li></ul>                                                                                                                            | • New materials and integration                                                              | Development  |

| Nano Floating-Gate<br>Memory    | Barrier-engineered<br>tunnel<br>nanocrystals | 2005         | <ul><li>Nonvolatile</li><li>Fast read and write</li></ul>                                                                                                                                                      | Material quality                                                                             | Demonstrated |

| Single/few Electron<br>Memories | SET                                          | 2007         | <ul><li>Density</li><li>Power</li></ul>                                                                                                                                                                        | <ul><li>Dimensional control (room temperature operation)</li><li>Background charge</li></ul> | Demonstrated |

| Molecular Memories              | Bistable switch<br>molecular devices         | 2010         | <ul> <li>Density</li> <li>Energy</li> <li>Equivalent switches</li> <li>Larger I/O disparity</li> <li>Possibilities for 3D</li> <li>Less difficult to communicate</li> <li>Tolerance-based circuitry</li> </ul> | Volatile thermal stability                                                                   | Demonstrated |

Note: DRAM: Dynamic random-access memory; I/O: Input/output; NDRO: Non-Destructive Read Out; NOR: NOR gate; OUM: Ovonic Unified Memory; SET: Single-Electron Transistor. CMOS platform technology, fabrication may be thought of as a sort of modification or addition. The following technologies are used as benchmarks: DRAM and FLASH NOR. Table 1.2 compares the properties of developing research memory devices with those of present DRAM and FLASH NOR technologies. DRAM and FLASH NOR are the two types of memories that create the most volume at the moment. Magnetic random-access memory (MRAM) and phase-change randomaccess memory (PCRAM) are two of the new memory technologies that may become available in the near future by 2030. Nonvolatility is one of the primary motivating factors for the development of both of these technologies.

BeyondCMOS is being studied in a lot of different ways. Some of the things that are being looked at are magnetic devices, MEMS, response electronics, and devices that use two-dimensional (2D) materials. The following are some of the most note-worthy investigations:

- Circuits and architectures include both circuits that only use new technology and hybrid circuits that use both new and old technology. Research is being done on massively parallel architectures, processors for applications like image processing and pattern recognition, and circuits for radiofrequency (RF) systems.

- *Magnetic logic*: The logic that is built with new magnetic devices is called "mLogic," and it is being looked at as a possible technology for developing electronic systems in a world where energy is a limited resource. Because it is made without semiconductors and only uses magnetic devices, each logic gate can act as its own independent nonvolatile storage element. The mLogic systems can be powered with as little as 100 mV of voltage.

- MEMS and NEMS are embedded and specialized miniature systems that consist of one or more components or micromachined structures that function as sensors or actuators to enable functions at a higher level inside the structure of a more complex system. Embedded and specialized miniature systems can be broken down into two categories: generalized and specific. Whereas MEMS technology operates on a micrometric scale, NEMS technology operates on a nanometric scale.

- Resistive switching electronics: The materials described here can be used to add new features to classic CMOS, like memory cells, nonlinear two-terminal selection devices, RF signal switches, oscillator relaxation, and surge protection devices. These materials might be as simple as metal oxides or as complex as phase-transition chalcogenides.

- *Devices based on 2D materials*: Graphene and other materials have unique electrical and optical properties that can be used to make brand-new electronic devices. These could be used in areas like photonics and neural networks.

In contrast to memory technologies, which are thought to have a wide range of potential applications, beyond-CMOS solutions for logic devices are projected to have a greater emphasis on application specificity. One further key difference between beyond-CMOS memory logic is that, although it is believed that memory alternatives may be incorporated into a CMOS technological platform, it may be more difficult to do so for logic devices. This distinction is one of the most important differences between the two. Table 1.4 provides an overview of published research on key developing logic technologies.

In an approach similar to that of memory devices, contemporary logical technologies need to satisfy some basic needs. In the context of beyond CMOS technology, akin to memory devices, modern logical technologies must fulfill fundamental requirements and exhibit compelling characteristics to justify the substantial investments needed for the development of new infrastructure. This rationale is crucial, as the establishment of fresh infrastructure entails significant resource allocation. Every newly developed information-processing technology needs to first and foremost be capable of satisfying the following requirements:

- Functionally scalable considerably beyond (>100×) CMOS

- A remarkable pace of data processing as well as throughput

- Minimum amount of energy required for each operational function

- The lowest possible scalable cost for each functional activity

Spintronics is the technique that has been used the most in the creation of beyondCMOS. It is used to fix the problem of power loss that can happen in integrated circuits with a lot of transistors. Quantum mechanics, which shows how the spin of an electron can be used, backs up this idea. It is possible to think of it as a brief magnetic moment that is experienced by an electron. Having control over the spin's polarity is a huge benefit. This makes it possible to take into account the amount of energy that is lost in a transistor.

### 1.3 ROLE OF INDUSTRY IN THE ADVANCEMENT OF BEYOND-CMOS TECHNOLOGY

Beyond CMOS would not be where it is now without the enormous contributions made by Intel. When combined with ultralow power while sleeping, the business's unique magneto-electric spin-orbit (MESO) logic circuit can cut voltage by five times and energy use by 10–30 times [16]. The technology was created and presented by the company. Modern semiconductors based on complementary metal oxides are incapable of such feats.

The term "beyond CMOS" refers to digital logic technologies that might be developed in the future. These will be capable of scaling beyond the current CMOS scaling constraints. These scaling limits restrict the density and speed of devices because they heat up; hence, "beyond CMOS" refers to digital logic technologies that will be able to scale beyond these limits [17].

Intel is doing secret research on possible ideas for the time after CMOS, and several other companies and scientists have also helped. The Nanoelectronics Research Initiative (NRI) is going on a journey to evaluate these potential alternatives to one another as semiconductor research organizations throughout the globe scramble to develop a viable successor to CMOS.UCLA's California NanoSystems Institute (CNSI) has pioneered several research programs in the field, recognizing the global

FIGURE 1.3 Advancements in CPU clock scaling.

need for beyond-CMOS technology. CNSI researchers are devoted to producing adaptive, accessible electrical gadgets that enable us to imagine a future without CMOS.

As mentioned earlier, "Beyond CMOS" is the name of one of the seven focus groups of ITRS 2.0 (2013) and its successor, the IRDS. Beginning in 1986, there was a proliferation of CMOS-based CPUs (e.g., the 12 MHz Intel 80386). Figure 1.3 shows the advancements in CPU clock scaling over the years.

### 1.3.1 THE IMPACT OF BEYOND-CMOS TECHNOLOGY DEVELOPMENTS ON OTHER RESEARCH FIELDS

Most likely, the easiest way to find related study disciplines is to look at the IRDS emphasis areas again. Beyond CMOS is a big and important part of the goals that have been set, but there are more important parts for research and development [6, 18, 19]. Several roadmap International Focus Teams (IFTs) were made to see where things stood and how much progress could be made in the following areas:

- Systems and architectures

- Lithography

- Yield enhancement

- Application benchmarking

- More Moore (a term from Moore's law that describes how technology has gotten better over time)

- Making standard integrated circuits

- Outside system connectivity

- Emerging research materials

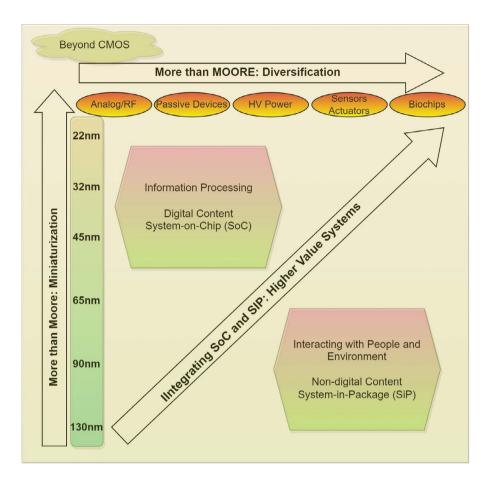

Figure 1.4 presents a performance comparison between "more Moore," which refers to the practice of producing more enhancements to the now-available technology, and "beyond CMOS," which refers to the practice of making significant alterations to how technology operates.

The demand for the creation of new system designs is being driven by the development of innovative technologies for wafer bonding. This is urging both research toward the three-dimensional (3D) integration of silicon devices as well as the

**FIGURE 1.4** A comparison of the potential productivity increases that may be achieved with "more Moore" (that is, more enhancements to the existing technology) versus "beyond CMOS."

construction of new system architectures. Similarly, the creation of optical input/output with the potential for high bandwidth could influence the design of a new architecture that might take advantage of this capacity. This possibility exists because of the progress of optical input/output. As a consequence of this, the development of new processes might be seen as the possibility of new architectures that were not previously realizable. The following research architectures that are on the horizon are outlined in Table 1.3.

#### **TABLE 1.3**

#### **Emerging Research Architectures**

|                                   | Device                                                                                                               |                                                                                                                                      |                                                                                                     |               |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------|

| Architectures                     | Implementation                                                                                                       | Challenges                                                                                                                           | Advantages                                                                                          | Maturity      |

| 3D Integration                    | CMOS employing a<br>variety of different<br>material systems                                                         | <ul> <li>Heat elimination</li> <li>Absence of design tools</li> <li>Challenging test and measurement</li> </ul>                      | <ul> <li>Less interconnect<br/>delay</li> <li>Enables mixed<br/>technology<br/>solutions</li> </ul> | Demonstration |

| Quantum<br>Cellular<br>Automata   | Arrays of quantum<br>dots                                                                                            | <ul> <li>Limited fan<br/>output</li> <li>Dimensional<br/>control (low-<br/>temperature<br/>operation)</li> <li>Background</li> </ul> | <ul> <li>Excellent<br/>functional density</li> <li>No connections<br/>in signal path</li> </ul>     | Demonstration |

|                                   |                                                                                                                      | charge sensitive                                                                                                                     |                                                                                                     |               |

| Defect-Tolerant<br>Architecture   | Intelligently<br>assembles<br>nanodevices                                                                            | Requires     pre-computing     test                                                                                                  | • Helps hardware<br>that has defect<br>densities that are<br>greater than 50%                       | Demonstration |

| Molecular<br>Architecture         | Molecular switches<br>and memories                                                                                   | • Limited functionality                                                                                                              | • Allows for<br>computing that is<br>done in memory                                                 | Concept       |

| Cellular<br>Nonlinear<br>Networks | Single-electron<br>array architectures                                                                               | <ul><li>Subject to<br/>background noise</li><li>Tight tolerances</li></ul>                                                           | Makes it possible<br>to use single-<br>electron devices<br>at room<br>temperature                   | Demonstration |

| Quantum<br>Computing              | <ul> <li>Spin resonance<br/>transistors</li> <li>NMR devices</li> <li>Single-flux<br/>quantum<br/>devices</li> </ul> | <ul><li>Extreme<br/>application<br/>limitation</li><li>Extreme<br/>technology</li></ul>                                              | Enables<br>unbreakable<br>cryptography and<br>exponential<br>performance<br>scaling                 | Concept       |

Note: CMOS: Complementary metal-oxide-semiconductor; NMR: Nuclear magnetic resonance.

#### 1.4 APPLICATIONS OF BEYOND-CMOS TECHNOLOGY

#### 1.4.1 EXISTING BEYOND-CMOS TECHNOLOGY APPLICATIONS

Beyond-CMOS process technology is being used in a variety of specialized applications. For instance, Josephson junctions are essential for the deployment of qubits as well as the management systems that govern them. Due to the temperature sensitivity of qubits, Josephson junctions are the optimal option due to their orders-of-magnitude lower power dissipation per computation than CMOS.

Aside from CMOS, technology has almost always played a significant role in the medical industry. Superconducting quantum interference devices (SQUIDs), which are sensitive superconducting devices, have made noninvasive evaluations of electrophysiological activity feasible. Magnetoencephalography (MEG) is a magnetic-source imaging technique that has a price tag of over \$500 million USD by the year 2020. Aside from CMOS technology, medical professionals can use magnetocardiography to detect major issues, such as abnormalities in the fetal heart rhythm.

#### **1.5 ALTERNATIVES FOR CMOS ELECTRONICS**

In information technology, the performance of microprocessors has gotten a lot better over the last 20 years. Moore's law states that every two years, the device complexity and hence the performance of microprocessors will double. For this performance boost to happen, the size of CMOS transistors, which are the brains of microprocessors, must be greatly reduced. Currently, CMOS electronics are composed of structures of around 100 nm. Consequently, the functionally critical components of the transistor now have just a few dimensions on the atomic-layer scale. Soon, CMOS component designs will approach the sub-100-nm level by the year 2030. Extreme ultraviolet (EUV), X-ray, and electron-beam lithography, as well as scanning probe methods, nanoimprinting, and self-organization processes, are now being investigated for the fabrication of structures smaller than 100 nm.

Conventional CMOS technology suffers from physical restrictions. CMOS will ultimately have a structural width limit of 20–30 nm due to the properties of electron waves. Miniature wires require a reduction in current density to address the electromigration issue. Further circuit miniaturization is also hampered from a financial aspect, since it is projected that manufacturing costs for such microchips would increase faster than their market return. Several technologies, including spintronics, molecular electronics, and quantum information processing, are proposed as possible future alternatives for CMOS technology.

All of these ideas incorporate genuine, practical nanotechnology components. The market could shift in the future to 3D devices that are monolithic or stackable. Surprisingly, 3D electronics, graphene, and CNTs did not meet the requirements according to the most recent performance benchmarks from Intel. The top five technologies on Intel's most promising devices are the spin-majority gate, spinwave devices, III–V tunnel field-effect transistors (TFETs), heterojunction TFETs, and graphene nanoribbon (GNR) TFETs. GNR TFETs are a new type of TFET that uses GNRs as the tunneling material. Decisions need to be taken in the next 10 years to find workable CMOS replacements by the year 2025. Benchmarking techniques and measurements are being utilized to organize and direct the study of materials, devices, and circuits.

#### **1.5.1 MOLECULAR ELECTRONICS**

The main goal of the field of molecular electronics is to use organic and/or biological molecules to make electronic functions and/or parts. Some of the main problems that this field of study tries to solve are how to change switching processes, how fast switching happens, how to make large molecular circuits, how to design good processors, and how molecular circuits interact with the larger world [20, 21]. Approaches to self-organization are being studied, specifically for the development of molecular circuits. These methods should make it possible to produce these circuits at a lower cost. Since fundamental research is still in its infancy, molecule electronics are not yet commercially viable. Due to their unique electrical properties, CNTs are a promising class of materials for molecular nanoelectronics. This includes components for transistors and logic circuits as well as the small wires that connect them.

#### **1.5.2** Spintronics

Magnetoelectronics is frequently viewed as the natural progression that leads to spintronics. For data processing, spintronics uses both the magnetic moment and charge of a potential electron. Existing projections indicate that components that just alter the spin of electrons will process information far more quickly than those that depend on electrical charge for very rapid data processing. In addition, switching would cost less energy compared to an equivalent charge transfer. Due to the magnetic moment providing an extra degree of freedom for the electron, spintronics may indeed be developed alongside charge-based data processing. Quantum computers might be developed more quickly in the long run if they make use of nuclear spin in addition to electron spin. The first component in the field of data storage to make use of electron spin has been successfully manufactured in mass quantities. The most recent generation of the thin-film read heads for hard disc drives makes use of a read head known as a spin valve. It takes advantage of the giant magnetoresistance (GMR)effect. MRAM is a highly promising candidate for the development of future spintronic data storage components. MRAM is an alternative that could be used in place of DRAM or FLASH memory [22-25].

#### 1.5.3 QUANTUM COMPUTING

Quantum effects appear as disconcerting nanoscale effects that decrease the performance of conventional components. Quantum information processing, on the other hand, is based on the exact use of quantum effects for a brand-new sort of massively parallel data processing. The fundamental unit of information in a quantum computer, known as a "qubit" or "quantum bit," is more quaternary than binary. A unique sort of "quantum parallelism" that enables the "simultaneous" exploration of an exponentially large number of computing routes on a single device looks to be realizable by using the superposition and entanglement properties wisely. Since its inception, quantum information processing has made several significant strides forward, such as the creation of two- and three-qubit quantum computers that can carry out fundamental arithmetic operations and sort data. The development of a quantum computer that could compete with the most advanced digital computer available today is hampered by a few potentially major obstacles. Error correction, decoherence, and hardware design are three of the areas that have the potential to be the most challenging.

#### **1.5.4 LOGICS WITH TUNNELING COMPONENTS**

Tunneling components, such as resonant tunneling diodes, take advantage of the very fast quantum mechanical tunneling effect. This provides a substantial gain in speed as compared to components that are more traditionally used. Photodetectors, optoelectronic switches, and high-frequency oscillators in the terahertz region are all examples of applications for resistive temperature detectors (RTDs) manufactured from III–V semiconductors. There are applications for digital electronics with ultrafast, energy-efficient processors in satellite communication systems. Unfortunately, there are now so few RTD-based transistor designs. Nevertheless, the earliest logical circuits were already in existence. Because the qualities of the components depend greatly on the geometry of the component, a rigorous manufacturing process is very difficult.

RTDs will continue to be a specialist application if there is no more research and development done in this field. Si/SiGe RTDs are thought to have more potential because they can be built into standard silicon circuits. However, there are still a lot of technical problems to solve. Their sensitivity to radiation should be taken into account when thinking about how RTDs could be used in space. This research was done in part by working together. Radiation defects significantly reduce the tunneling current, according to early tests on the radiation sensitivity of RTDs.

Table 1.4 shows the performance analysis of different memory technologies such as SRAM, DRAM, FLASH, and so on. The comparison of various memory cells was done based on several parameters, including read time, write time, write power, and full scalability.

A comparative performance analysis of 6T, 7T, 8T, 9T, and 10T SRAM cells is shown in Table 1.5.

The efficiency of graphene nanoribbon field-effect transistor (GNRFET)-based SRAM cells is compared with that of CMOS-, FinFET-, and carbon nanotube field-effect transistor (CNTFET)-based SRAM cells in Table 1.6.

#### 1.6 FUTURISTIC GADGETS USING BEYOND-CMOS TECHNOLOGY

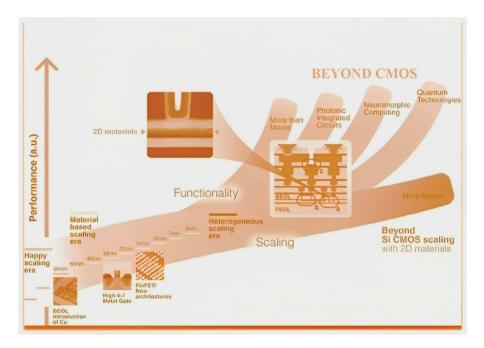

In the near future, several types of novel devices will be crucial for the development of security applications. Since hardware security turns into a greater aspect of the design, it is anticipated that beyond-CMOS technologies will assume the passive function that CMOS technology currently performs in security [17, 27]. Certain characteristics may be useful for simplifying circuit structures to improve protection. Figure 1.5 shows that, around the turn of the 20th century, an era in which silicon technology was scaled geometrically to ever smaller dimensions came to an end [14, 28–30].

|                    | Typical Memory Technology |        |                 | New Memory Technology |        |                 |              |              |

|--------------------|---------------------------|--------|-----------------|-----------------------|--------|-----------------|--------------|--------------|

| Parameters         | DRAM                      | SRAM   | Flash           | FeRAM                 | ReRAM  | PCRAM           | STT-<br>MRAM | SOT-<br>MRAM |

| Cell Size          | 6-10                      | 50-120 | 5               | 15-34                 | 6-10   | 4–19            | 6–20         | 6-20         |

| Nonvolatility      | No                        | No     | Yes             | Yes                   | Yes    | Yes             | Yes          | Yes          |

| Write Time (ns)    | 50                        | ≤2     | 106             | 10                    | 50     | 10 <sup>2</sup> | 10           | ≤10          |

| Read Time (ns)     | 30                        | ≤2     | 10 <sup>3</sup> | 5                     | 1-20   | 2               | 1-20         | ≤10          |

| Write Power        | Low                       | Low    | High            | Low                   | Medium | Low             | Low          | Low          |

| Future Scalability | Limited                   | Good   | Limited         | Limited               | Medium | Limited         | Good         | Good         |

## TABLE 1.4 Performance Comparison of Different Memory Technologies

Note: DRAM: Dynamic random-access memory; FeRAM: Ferroelectric random-access memory; PCRAM: Phase-change random-access memory; ReRAM: Resistive random-access memory; SOT-MRAM: Spin–orbit torque magnetic random-access memory; SRAM: Static random-access memory; STT-MRAM: Spin-transfer torque magnetic random-access memory.

#### **TABLE 1.5**

#### Performance Comparison of 6T, 7T, 8T, 9T, and 10T SRAM Cells

| SRAM Memory Cell | SNM | Write Margin | Dynamic Power | Delay |

|------------------|-----|--------------|---------------|-------|

| 6T SRAM          | 202 | 340          | 10.05         | 5.9   |

| 7T SRAM          | 223 | 360          | 4.87          | 3.6   |

| 8T SRAM          | 397 | 379          | 12.46         | 6.5   |

| 9T SRAM          | 410 | 330          | 16.55         | 7.6   |

| 10T SRAM         | 432 | 475          | 17.58         | 8.0   |

*Note:* SNM: Static noise margin; SRAM: Static random-access memory. *Source:* [12]

#### **TABLE 1.6**

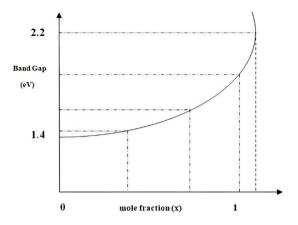

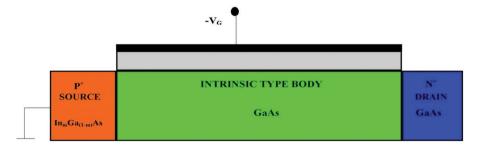

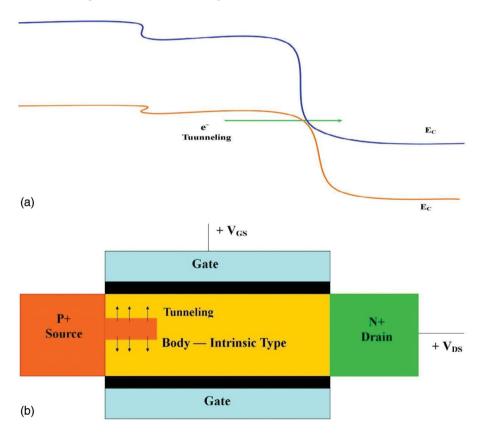

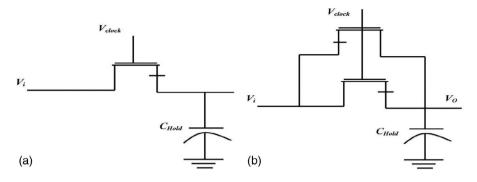

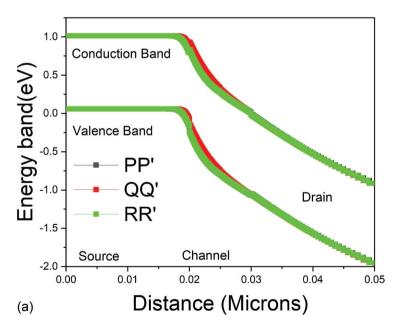

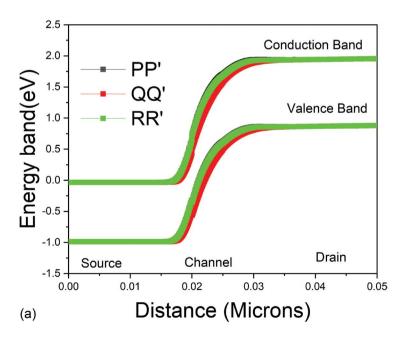

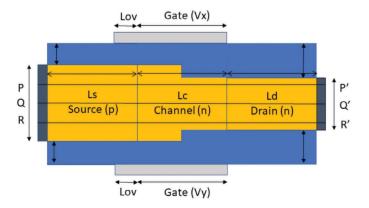

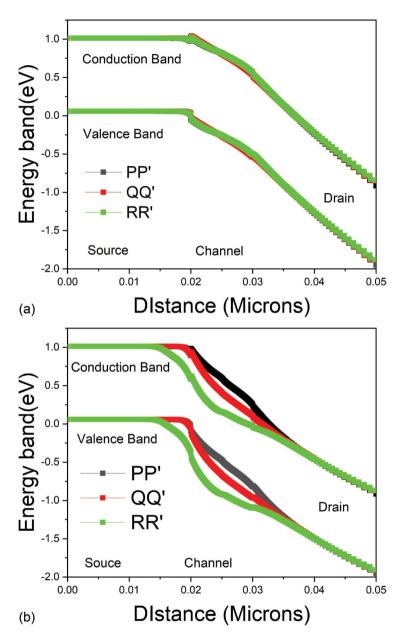

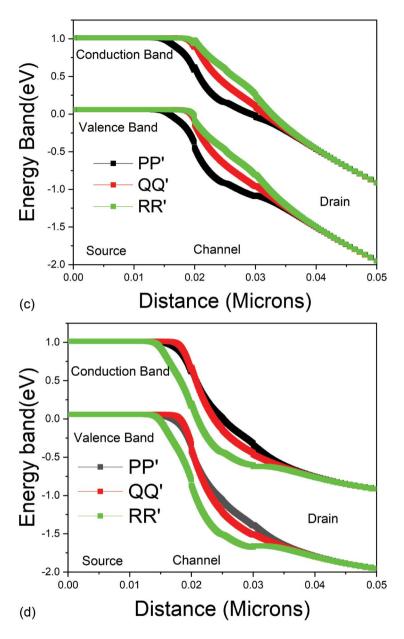

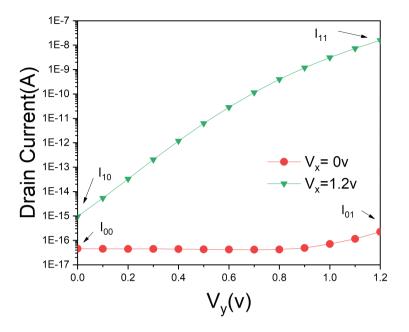

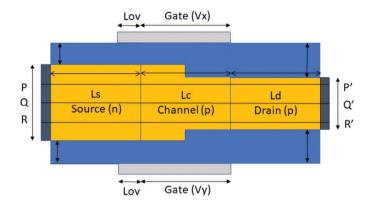

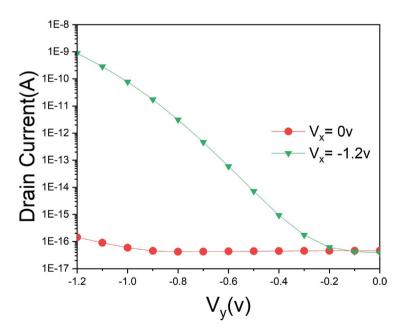

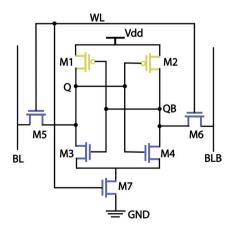

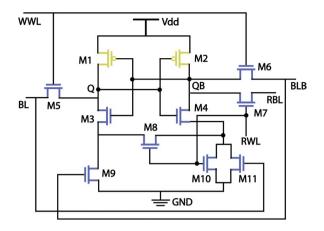

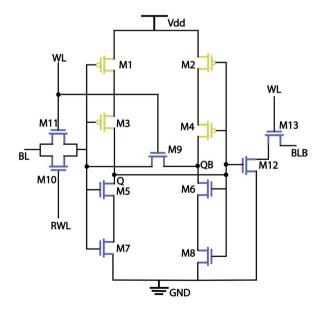

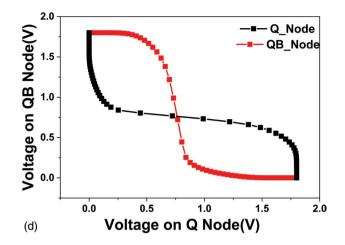

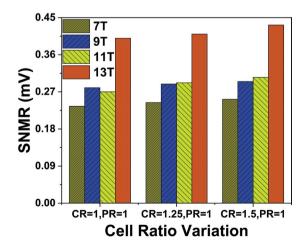

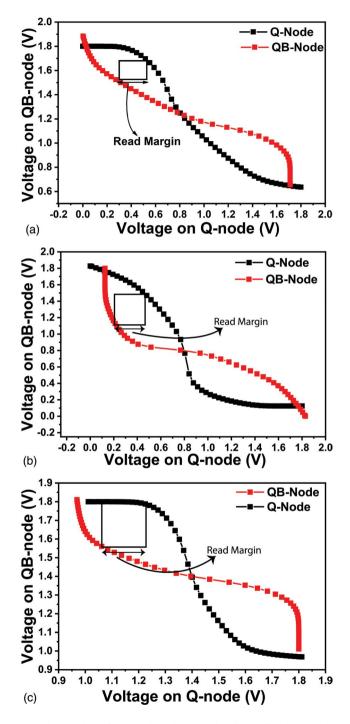

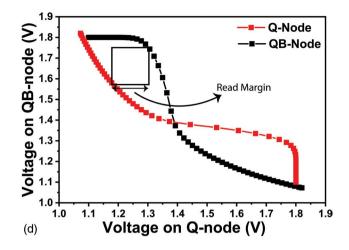

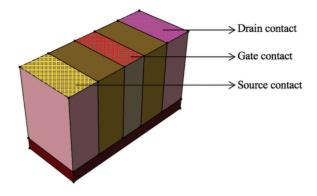

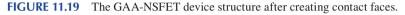

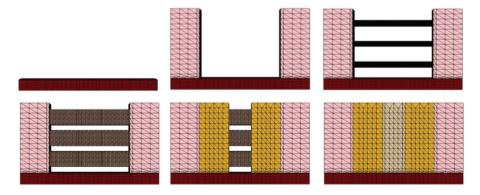

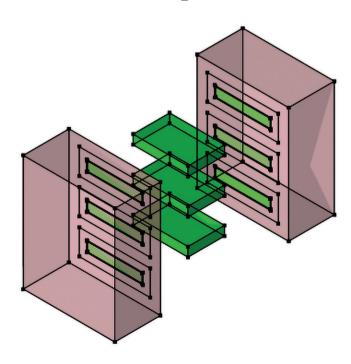

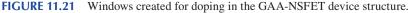

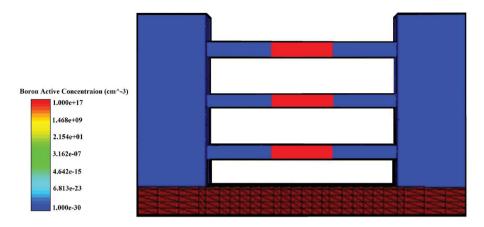

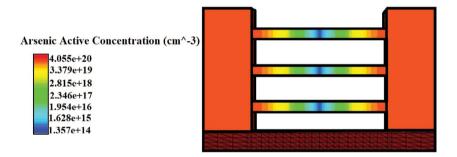

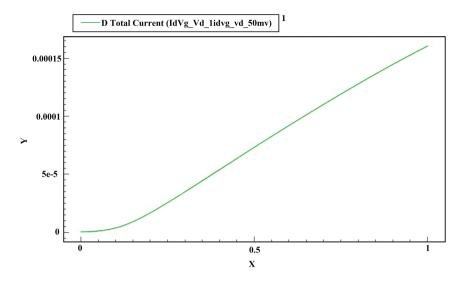

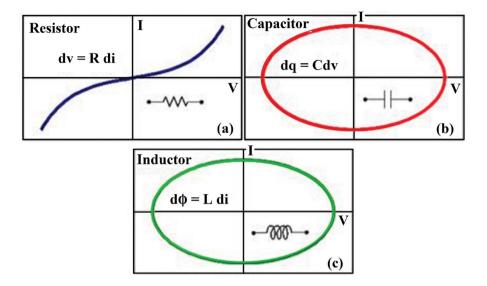

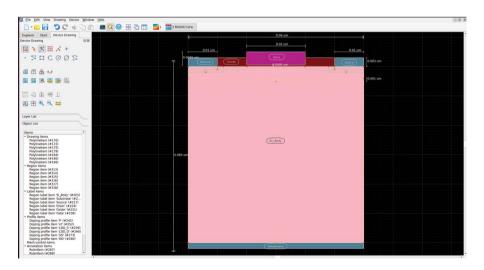

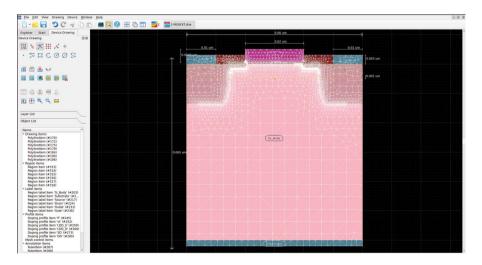

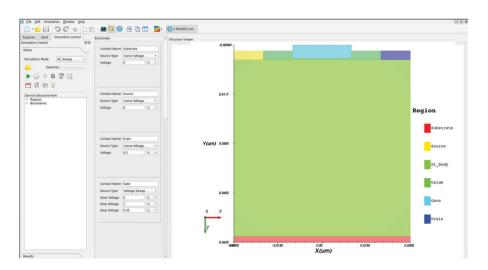

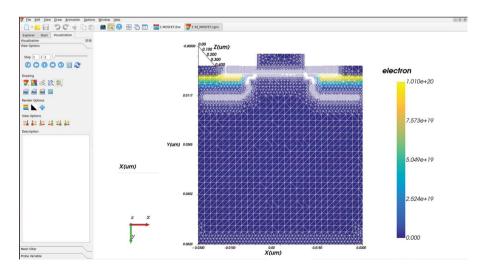

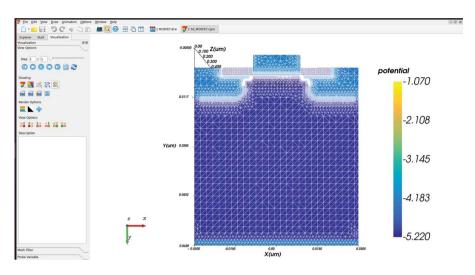

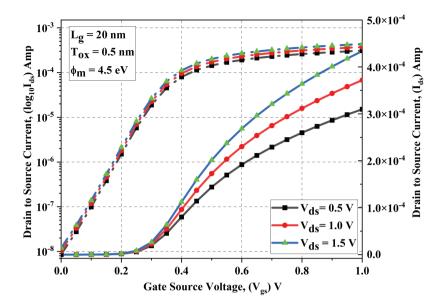

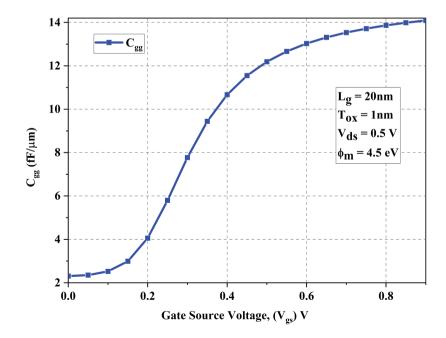

# Performance Comparison of a Standard 6T SRAM Cell at a 32 nm Technology Node [12], [26]