# Embedded Systems Design

## Using the MSP430FR2355 LaunchPad<sup>™</sup>

SECOND EDITION

## **Brock J. LaMeres**

## EMBEDDED SYSTEMS DESIGN USING THE MSP430FR2355 LAUNCHPAD<sup>™</sup>

## EMBEDDED SYSTEMS DESIGN USING THE MSP430FR2355

## LAUNCH PAD<sup>TM</sup>

2<sup>ND</sup> EDITION

**Brock J. LaMeres**

Brock J. LaMeres Department of Electrical and Computer Engineering Montana State University Bozeman, MT, USA

ISBN 978-3-031-20887-4 ISBN 978-3-031-20888-1 (eBook) https://doi.org/10.1007/978-3-031-20888-1

© The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Switzerland AG 2020, 2023

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

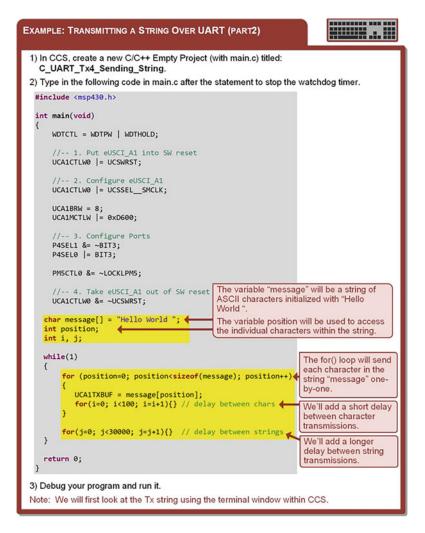

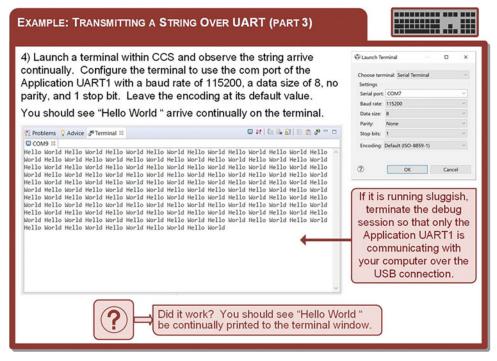

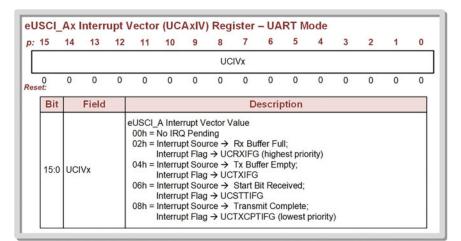

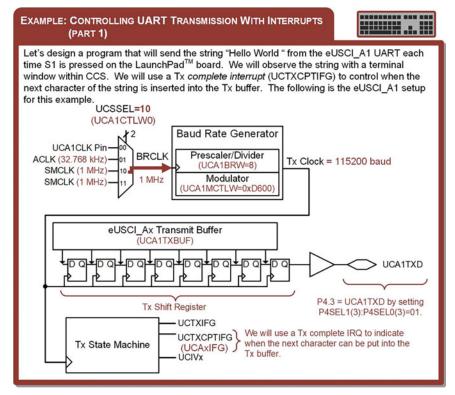

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

## Preface

#### Why Another Book on Embedded Systems?

Embedded computers represent one of the most pervasive technologies of our time. When most people think of computers, they think of their laptops and workstations, or even the servers that are the backbone of the Internet; however, when one begins to contemplate how many technologies around them use small, inexpensive computers embedded as their "brains," one begins to more fully understand the magnitude of how many embedded computers exist in our society. If you look around any room you will see technologies such as appliances, you may not even realize that most of it is run by an internal computer. Technologies such as appliances, thermostats, handheld devices, projectors, televisions, personal assistants, and radios all have small computers within them that control their operation. As one starts to notice all of the embedded computers than the standard general-purpose computers that run Windows® or iOS<sup>™</sup>. As these technologies become *smarter* and are Wi-Fi connected, we move into era called the *Internet of Things*. This next technological paradigm shift will turn all of the embedded computers into a collaborative network in an attempt to make our lives better by automating taking mundane tasks.

Simultaneous to the exponential increase in embedded computers in our society is the need for engineers and software developers that can build and program these systems. Due to the high popularity of embedded computers, there is also a wide range of embedded computer platforms. As such, the textbooks that exist to aid in the education of embedded computers are somewhat fragmented. Textbooks for embedded computers aren't able to be written at only the theoretical level such as circuits and electronics textbooks. Instead, they must identify a computer platform and focus the content on that specific embedded computer technology. This leads to a large number of embedded systems books to support the large number of embedded platforms. This also leads to books becoming obsolete much faster than traditional engineering textbooks.

One reason for a new book in this area is creating comprehensive content around a widely popular embedded computer, the Texas Instruments MSP430. The MSP430 is a modern computer platform that is mature in the market and has a great deal of technical and educational support behind it. This means that this platform will be relevant and supported for at least the next 10–15 years.

A second reason for a new book in this area is to provide content the way people actual learn (i.e., by doing). Current embedded systems books, even those targeting the MSP430, tend to only provide small code segments that can't be directly run on a target platform. This new book approaches content delivery around the model that the reader is sitting at a computer with an MSP430 plugged in and running each of the examples as they move through the book. This *learn-a-little*, *do-a-little* is a proven pedagogical strategy. It also supports both active learning within the classroom and self-regulated learning for individual readers.

A third reason for a new book in this area is to provide a seamless delivery of both assembly language and C language programming of the MSP430. Most embedded systems books are structured in one of three ways: (1) they only cover assembly; (2) they only cover C; (3) they attempt to cover both but don't provide sufficient details of either. This new book will begin in assembly language as a means to show the lower-level operation of the computer hardware. It will then move into C to implement more complex systems that require abstracting the lower-level hardware. With the design of the book consisting of examples in both languages that can be directly coded and run, there will not be a void between the examples and real implementation of the concepts as seen in other books.

The three guiding principles for the design of this book are:

**Learn by example** This book is designed to teach the material the way it is learned, through example. Every concept that is covered in this book is supported by numerous programming examples that provide the reader with a step-by-step explanation for how and why the computer is doing what it is doing.

**Learn by doing** This book targets the Texas Instruments MSP430 microcontroller. This platform is a widely popular, low-cost embedded system that is used to illustrate each concept in the book. The book is designed for a reader who is at their computer with the MSP430 plugged in so that each example can be coded and run as they learn.

**Build a foundational understanding first, then move into abstraction** This book teaches the basic operation of an embedded computer using assembly language first so that the computer operation can be explored at a lower level. Once complicated systems are introduced (i.e., serial communication and analog-to-digital converters), the book moves into the C programming language. Moving to C allows the learner to abstract the operation of the lower-level hardware and focus on understanding how to "make things work." By spending time in assembly to understand the underlying hardware, the transition to C can happen more rapidly while still leaving the reader with a foundational understanding of the underlying hardware.

If this learning model is followed, the reader will come away with much more than knowledge of facts and figures; they will have a skillset and experience with embedded systems that will be both marketable and of key importance to our society.

This second edition adds two highly requested chapters: Chaps. 16 and 17. Both chapters provide example programs on how to configure these systems and observe their operation.

#### How to Use This Book

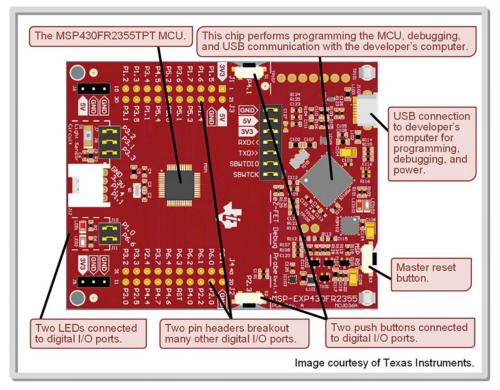

This book is most effective when the reader has the *Texas Instruments Inc. MSP430FR2355* LaunchPad<sup>™</sup> Development Kit and codes along with the material. All examples can be directly run on the LaunchPad<sup>™</sup> board. All programs were created and compiled using the *Texas Instruments Inc. Code Composer Studio (CCS)*. This development environment is free from Texas Instruments and can be run on multiple operating systems. Each of the examples noted with a keyboard are ones that are intended to be coded in CCS and run on the LaunchPad<sup>™</sup> board.

There are three supporting documents that should also be downloaded from Texas Instruments to provide background for the material in this book. The first is the *MSP430FR4xx and MSP430FR2xx Family User's Guide*<sup>1</sup>. This document gives the general concept of operation for the MSP430 architecture that is used on the specific microcontroller targeted in this book. Throughout this book, this document is referred to as the "MSP430 User's Guide." The second document that should be retrieved is the *MSP430FR235x*, *MSP430FR215x Mixed-Signal Microcontrollers Device-Specific Data Sheet*<sup>2</sup>. This second document provides the specific details of the MSP430FR2355 microcontroller device that is used in each example. Throughout this book, this document is referred to as the "Device-Specific Data Sheet." The final document that should be retrieved is the *MSP430FR235x LaunchPad*<sup>TM</sup> Development *Kit User's Guide*<sup>3</sup>. This document describes the circuitry implemented on the LaunchPad<sup>TM</sup> board. This document is critical to understanding the types of input/output and programming capability available on the LaunchPad<sup>TM</sup> board.

#### **Additional Resources**

Supporting videos will be posted to the author's YouTube channel, which can be found at https:// www.youtube.com/c/DigitalLogicProgramming\_LaMeres. This channel contains many other videos beyond embedded systems to help people learn digital logic, basic programming, and robotics. Subscribe to this channel in order to be notified when new videos for this book are posted.

Bozeman, MT, USA

Brock J. LaMeres

## Acknowledgments

Endless thanks to my family for support of this project. JoAnn, Alexis, and Kylie: You are my rocks and rockstars.

A huge thank you to all the Montana State University engineering students that helped with the development of this book. They proofed, made suggestions, helped create examples and labs, created slides, and even drew out explanations for the solutions manual. Go Bobcats!

## Contents

| 1: INTROD  | UCTION TO EMBEDDED SYSTEMS         | 1   |

|------------|------------------------------------|-----|

| 1.1 WнA    | IT IS AN EMBEDDED SYSTEM?          | 1   |

| 2: DIGITAL | LOGIC BASICS                       | 7   |

| 2.1 Num    | BER Systems                        | 7   |

| 2.1.1      | Positional Number Systems          | 7   |

| 2.1.2      | Base Conversion                    | 12  |

| 2.1.3      | Binary Arithmetic                  | 19  |

| 2.1.4      | Unsigned and Signed Numbers        | 22  |

| 2.2 Com    | BINATIONAL LOGIC                   | 29  |

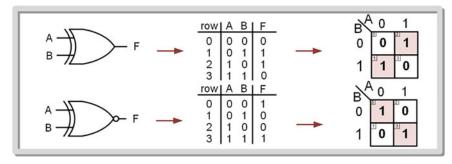

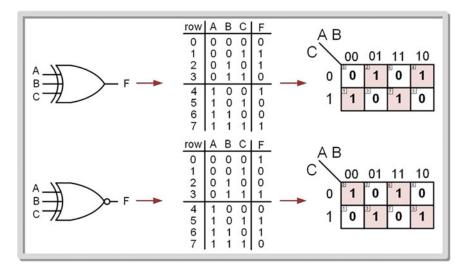

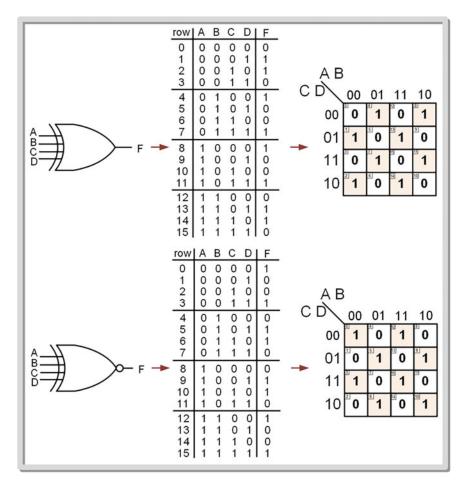

| 2.2.1      | Basic Gates                        | 29  |

| 2.2.2      | Boolean Algebra                    | 31  |

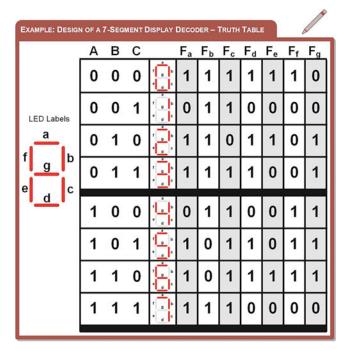

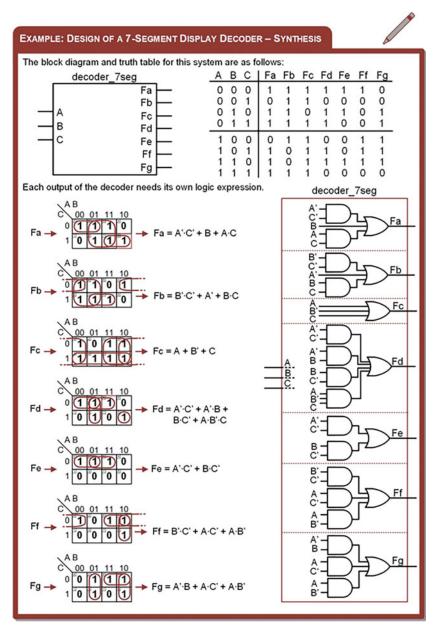

| 2.2.3      | Combinational Logic Synthesis      | 34  |

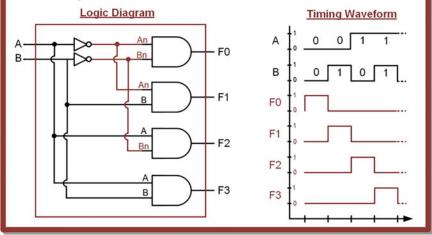

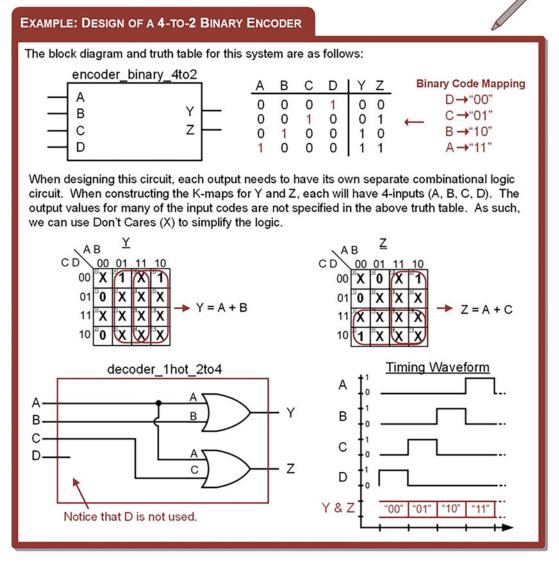

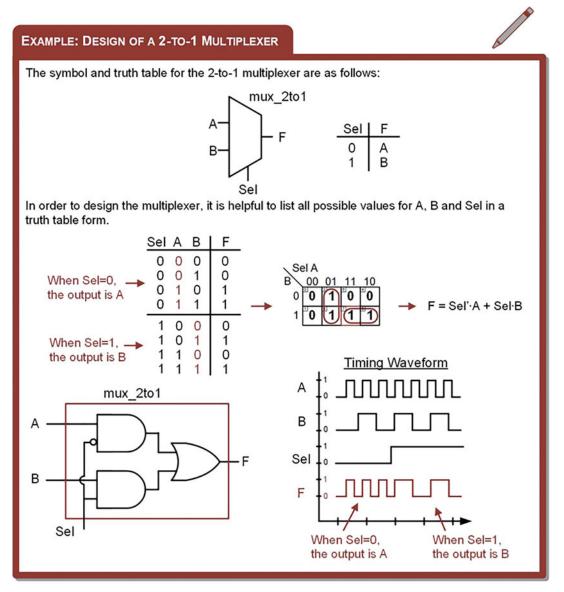

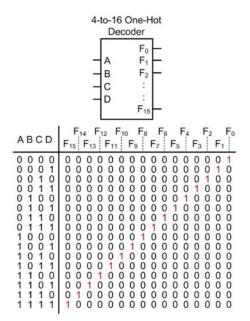

| 2.2.4      | MSI Logic                          | 56  |

| 2.3 SEQ    | JENTIAL LOGIC                      | 71  |

| 2.3.1      | Sequential Logic Storage Devices   | 71  |

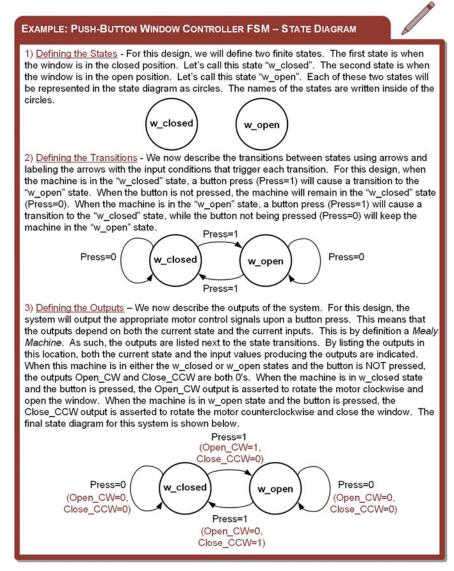

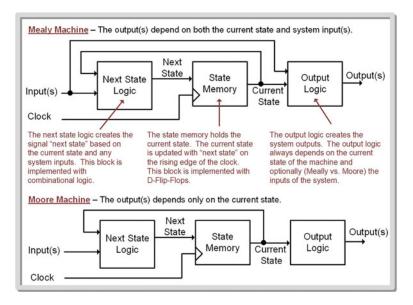

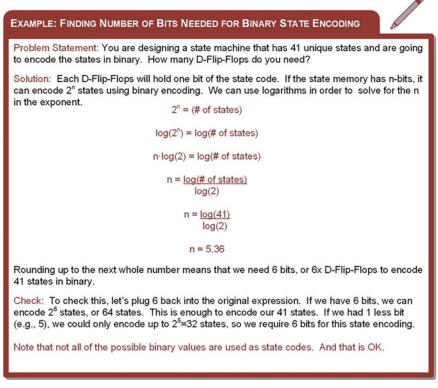

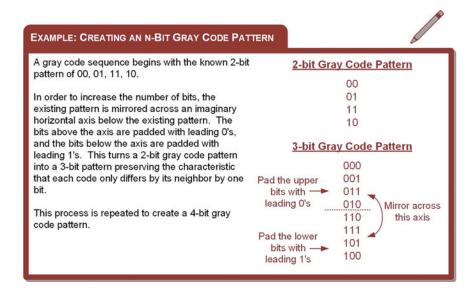

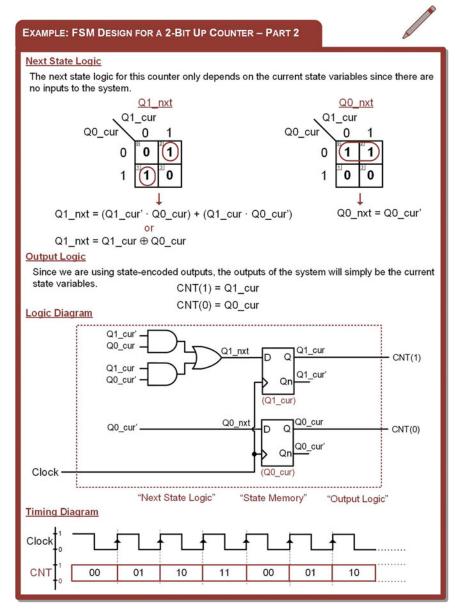

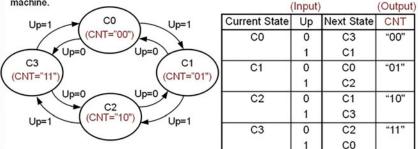

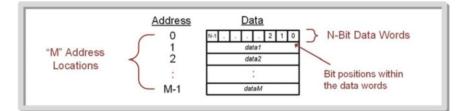

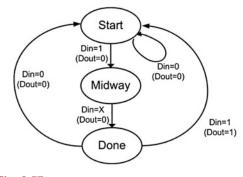

| 2.3.2      | Finite State Machines              | 86  |

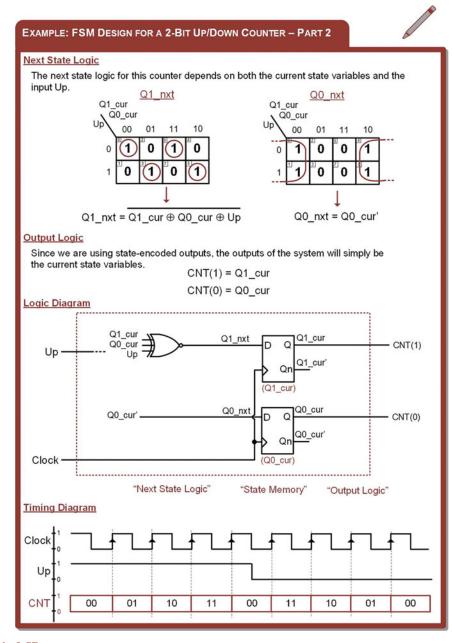

| 2.4 Men    | ORY                                | 104 |

| 2.4.1      | Memory Terminology                 | 104 |

| 2.4.2      | Memory Architecture                | 106 |

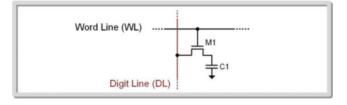

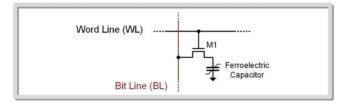

| 2.4.3      | Memory Technologies                | 110 |

| 3: COMPU   | TER SYSTEMS                        | 121 |

| 3.1 Com    | PUTER OVERVIEW                     | 121 |

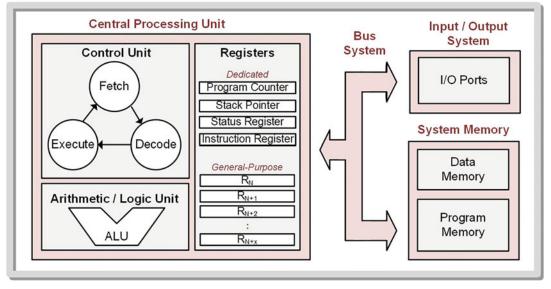

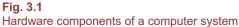

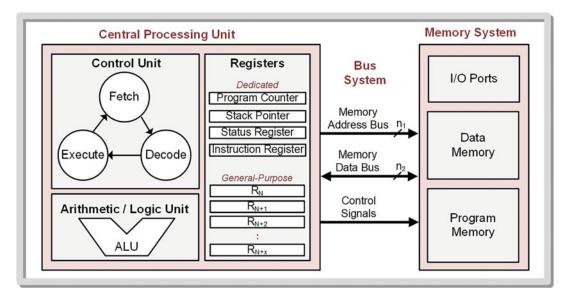

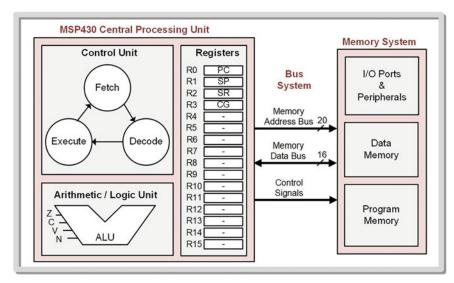

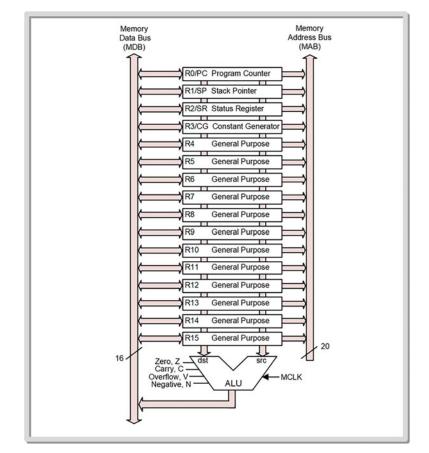

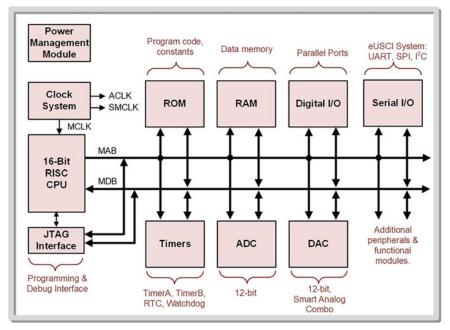

| 3.2 Com    | PUTER HARDWARE                     | 122 |

| 3.2.1      | Program Memory                     | 123 |

| 3.2.2      | Data Memory                        | 123 |

| 3.2.3      | Central Processing Unit            | 123 |

| 3.2.4      | Input/Output Ports                 | 125 |

| 3.2.5      | Bus System                         | 125 |

| 3.3 Com    | PUTER SOFTWARE                     | 126 |

| 3.3.1      | Classes of Instructions            | 126 |

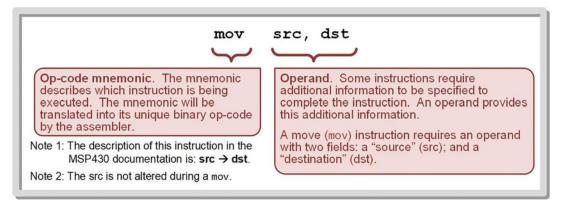

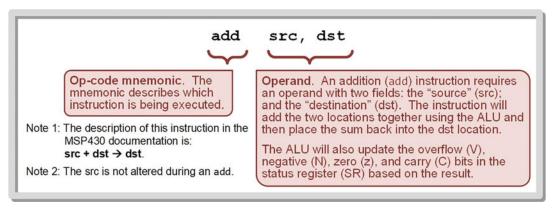

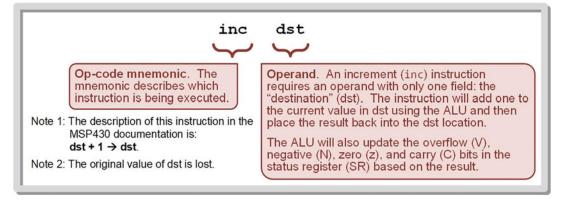

| 3.3.2      | Op-codes and Operands              | 127 |

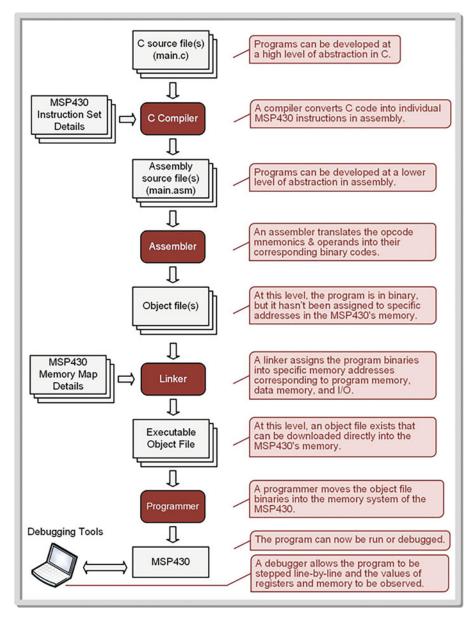

| 3.3.3      | Program Development Flow           | 129 |

| 4: THE MS  | P430                               | 135 |

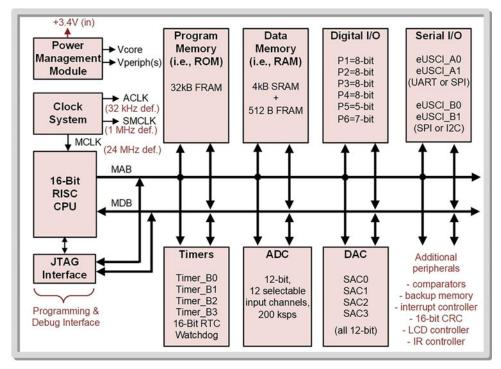

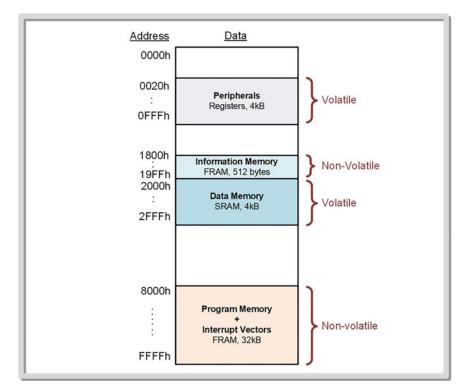

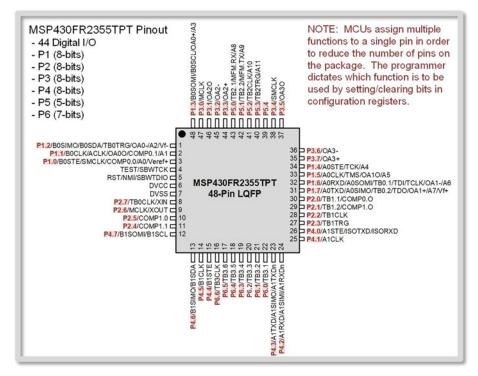

| 4.1 MSF    | P430 Hardware Overview             | 135 |

| 4.1.1      | Word Versus Byte Memory Access     | 136 |

| 4.1.2      | Program Memory                     | 136 |

| 4.1.3      | Data Memory                        | 136 |

| 4.1.4      | Central Processing Unit            | 136 |

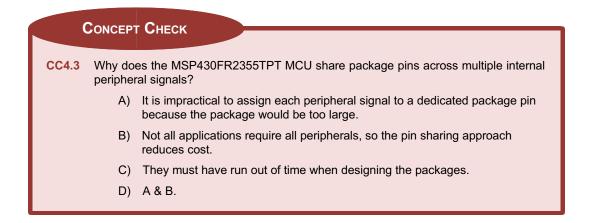

| 4.1.5      | Input/Output Ports and Peripherals | 138 |

| 4.1     | .6 Bus System                                                          | 140 |

|---------|------------------------------------------------------------------------|-----|

| 4.1     | .7 MSP430 Part Numbering                                               | 141 |

| 4.2     | MSP430 Software Overview                                               | 142 |

| 4.2     | .1 The MSP430 Instruction Set                                          | 142 |

| 4.2     |                                                                        |     |

| 4.2     |                                                                        |     |

|         | MSP430FR2355 LaunchPad™ Development Kit                                |     |

|         | TING STARTED PROGRAMMING THE MSP430 IN ASSEMBLY                        |     |

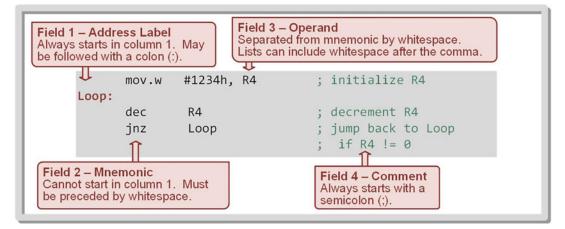

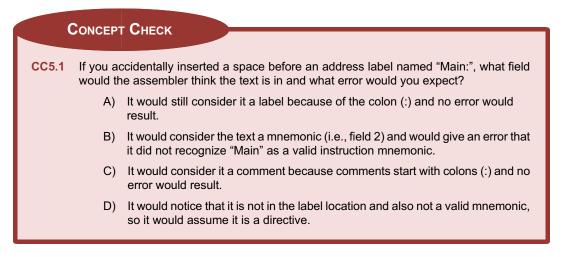

| 5.1     | THE ANATOMY OF AN ASSEMBLY PROGRAM FILE                                | 153 |

| 5.1     | .1 Instruction Statements                                              | 153 |

| 5.1     | .2 Assembler Directives                                                | 154 |

| 5.1     | .3 Miscellaneous Syntax Notes                                          | 157 |

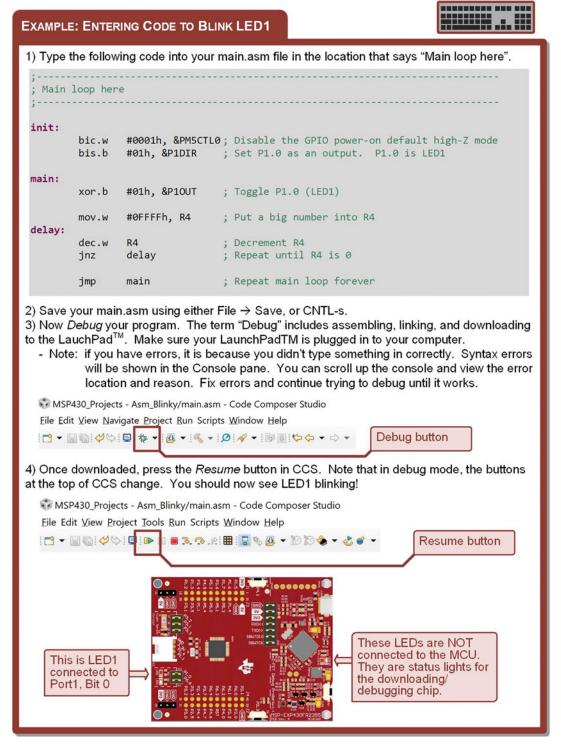

| 5.2     | YOUR FIRST PROGRAM: BLINKING LED                                       |     |

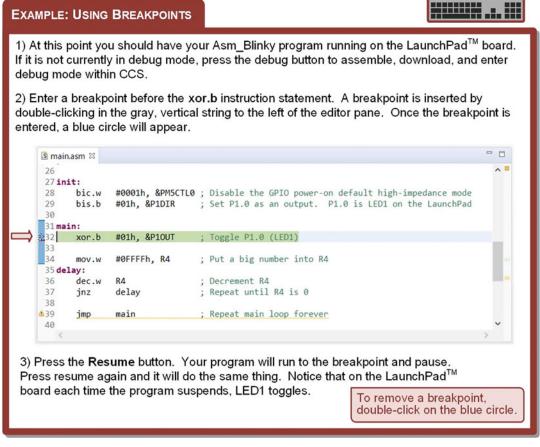

| 5.3 l   | JSING THE CCS DEBUGGER                                                 | 162 |

| 5.3     |                                                                        |     |

| 5.3     |                                                                        |     |

| 5.3     | •                                                                      |     |

| 5.3     |                                                                        |     |

| 5.3     |                                                                        |     |

|         | A MOVEMENT INSTRUCTIONS                                                |     |

|         |                                                                        | 474 |

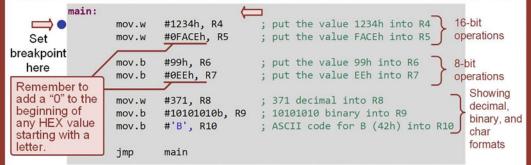

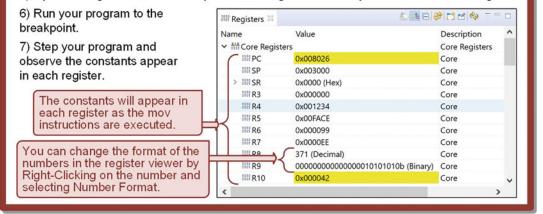

|         | THE MOV INSTRUCTION WITH REGISTER MODE (RN) ADDRESSING                 |     |

|         | THE MOV INSTRUCTION WITH IMMEDIATE MODE (#N) ADDRESSING                |     |

|         | THE MOV INSTRUCTION WITH ABSOLUTE MODE (&ADDR) ADDRESSING              |     |

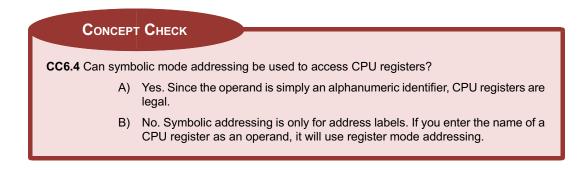

|         | THE MOV INSTRUCTION WITH SYMBOLIC MODE (ADDR) ADDRESSING               |     |

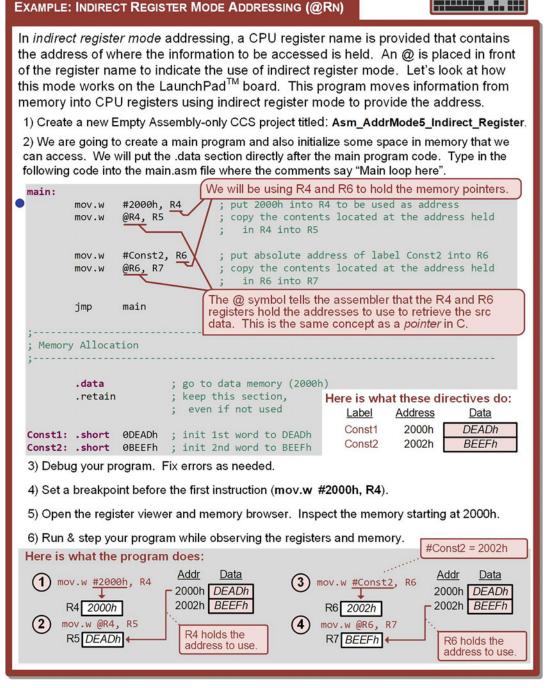

|         | THE MOV INSTRUCTION WITH INDIRECT REGISTER MODE (@RN) ADDRESSING       |     |

|         | THE MOV INSTRUCTION WITH INDIRECT AUTOINCREMENT MODE (@RN+) ADDRESSING |     |

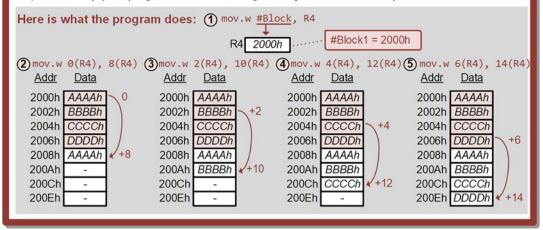

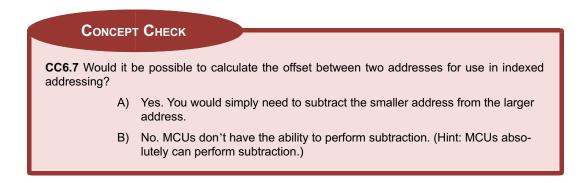

| 6.7     | THE MOV INSTRUCTION WITH INDEXED MODE (X(RN)) ADDRESSING               | 183 |

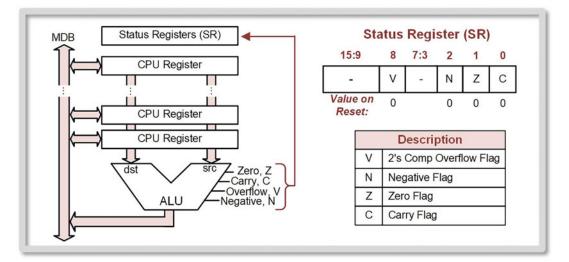

| 7: DATA | A MANIPULATION INSTRUCTIONS                                            | 191 |

| 7.1     | ARITHMETIC INSTRUCTIONS                                                | 191 |

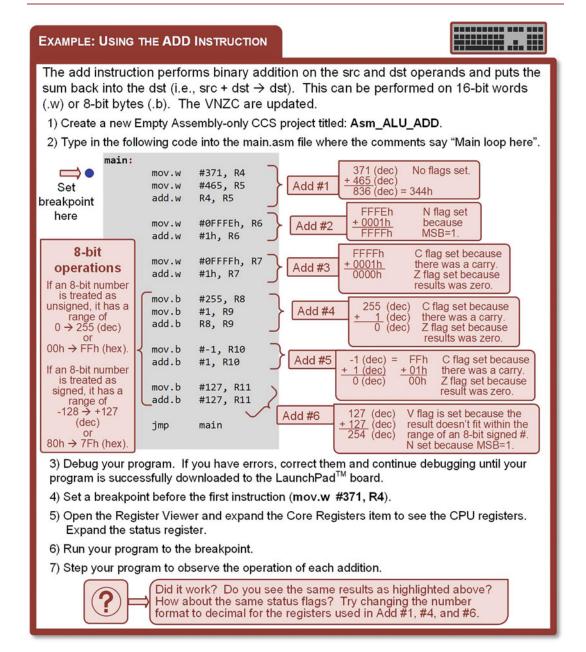

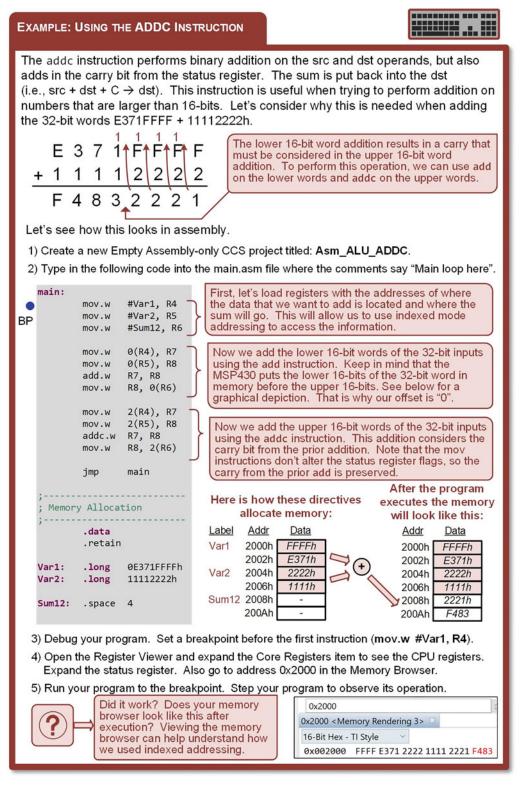

| 7.1     | .1 Addition Instructions                                               | 191 |

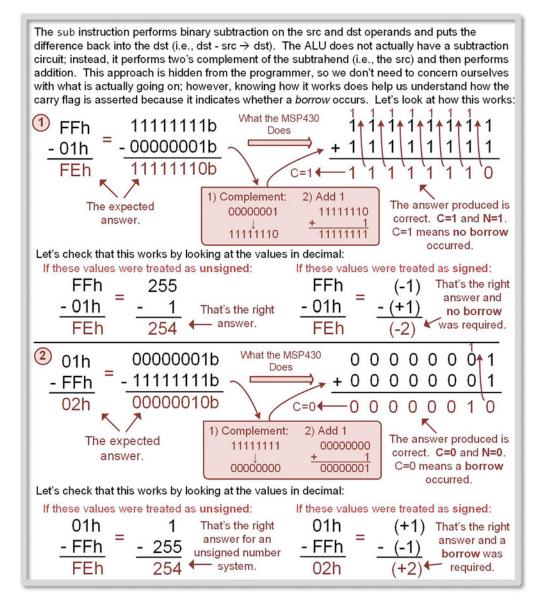

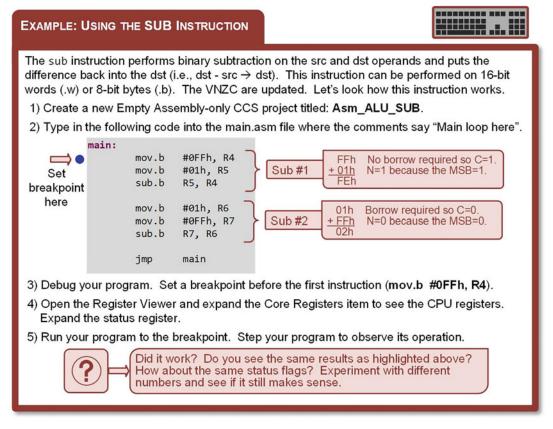

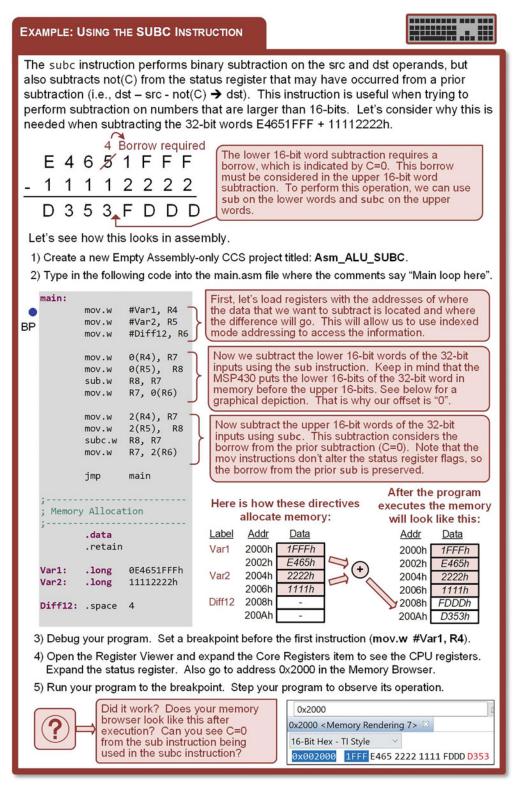

| 7.1     |                                                                        |     |

| 7.1     | .3 Increments and Decrements                                           | 198 |

|         | _ogic Instructions                                                     | 199 |

|         | BIT SET AND BIT CLEAR INSTRUCTIONS                                     |     |

|         | Fest Instructions                                                      |     |

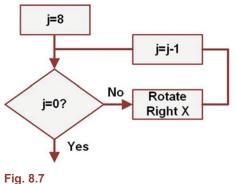

|         | ROTATE OPERATIONS                                                      |     |

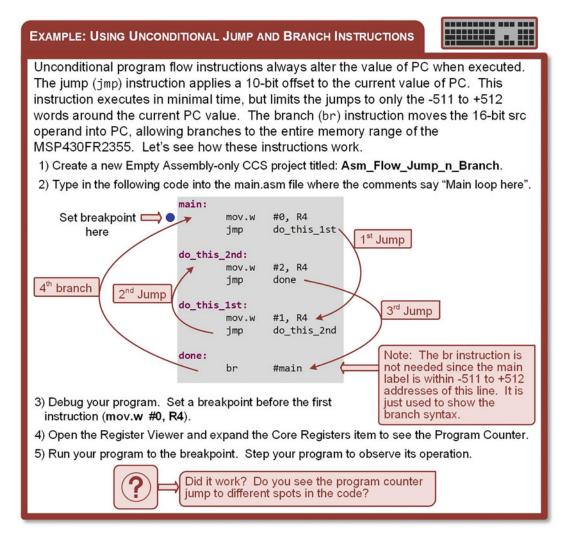

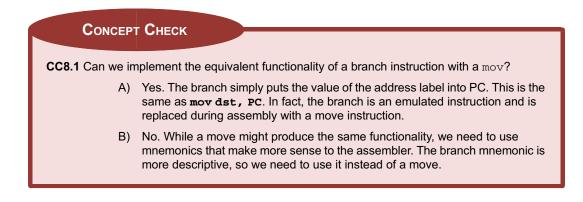

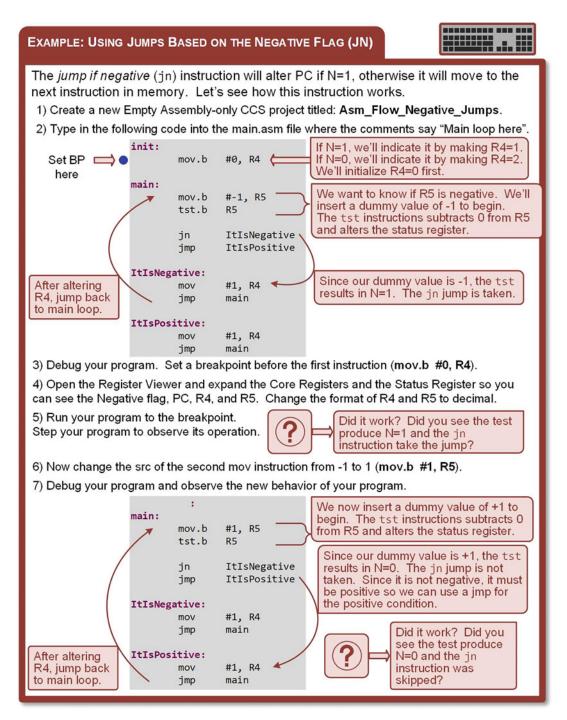

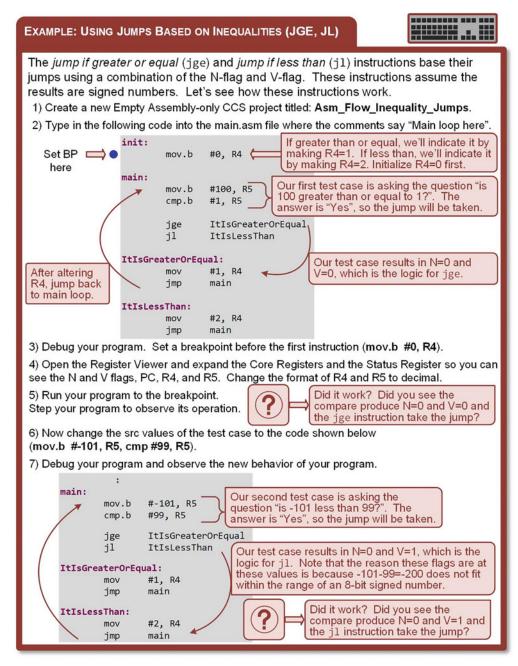

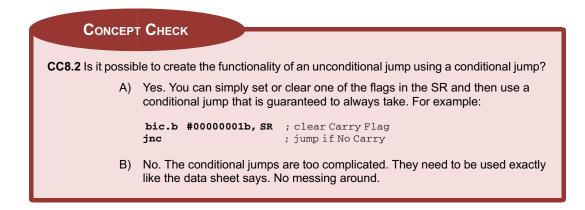

|         | GRAM FLOW INSTRUCTIONS                                                 |     |

|         |                                                                        |     |

|         | JNCONDITIONAL JUMPS AND BRANCHES                                       |     |

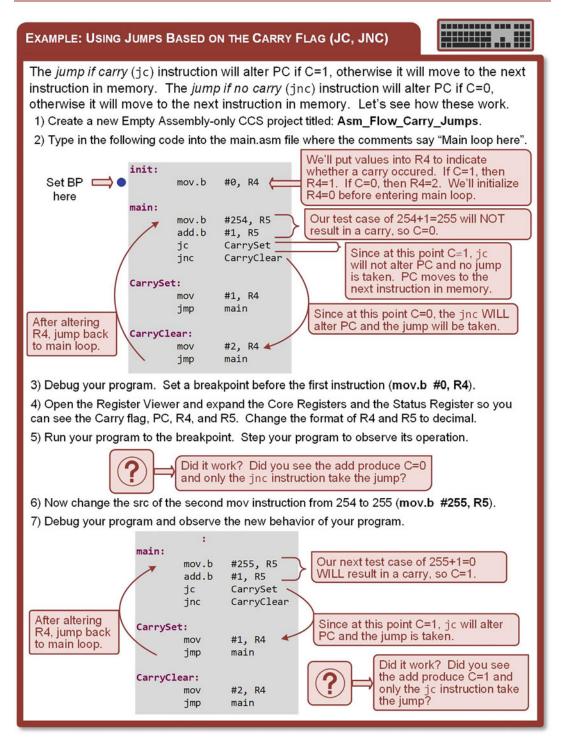

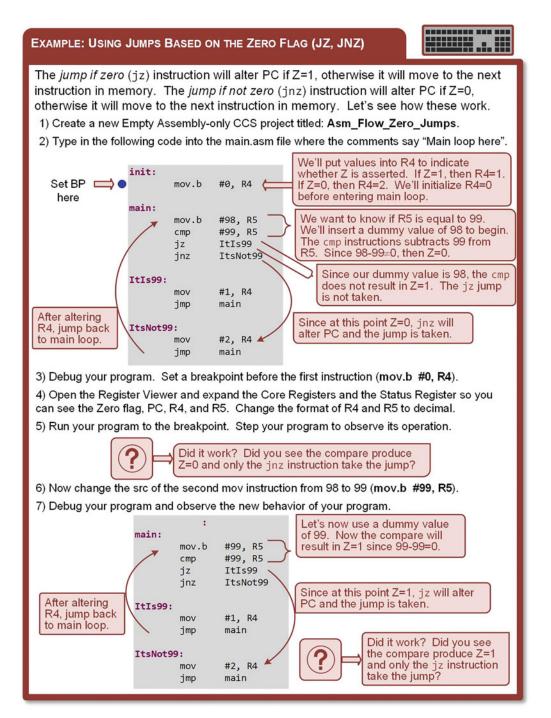

|         | CONDITIONAL JUMPS                                                      |     |

| 8.2     |                                                                        |     |

| 8.2     |                                                                        |     |

| 8.2     | .3 Negative-Based Jumps                                                | 218 |

| 8.2.4            | Overflow-Based Jumps                                        | 219 |

|------------------|-------------------------------------------------------------|-----|

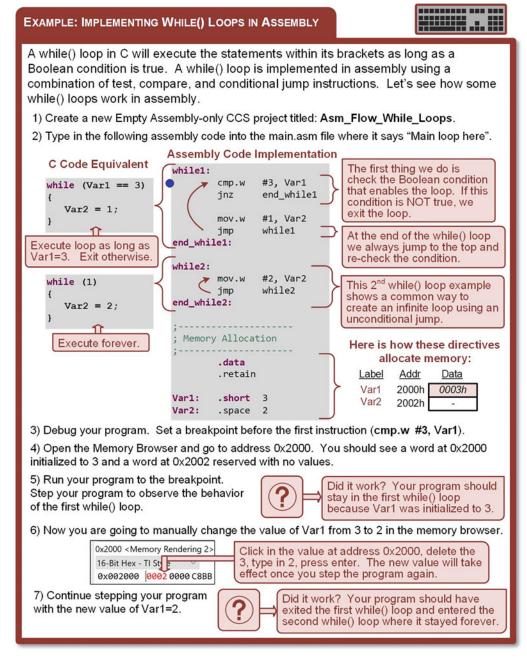

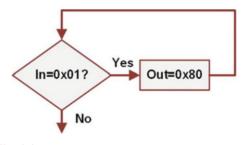

| 8.3 IMPLE        | EMENTING COMMON PROGRAMMING CONSTRUCTS IN ASSEMBLY          | 220 |

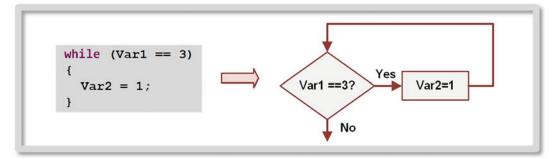

| 8.3.1            | Implementing While() Loop Functionality                     | 220 |

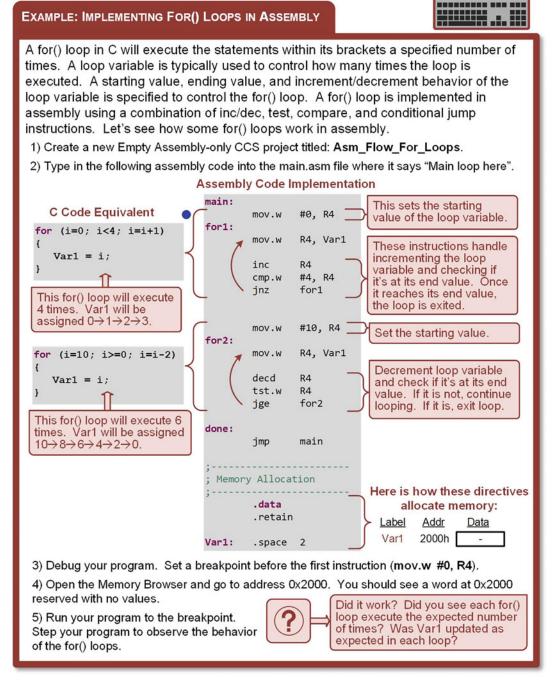

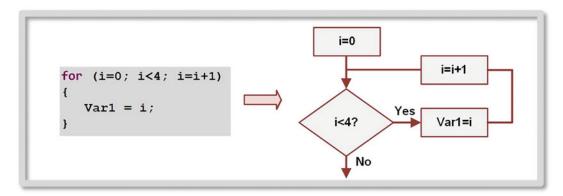

| 8.3.2            | Implementing For() Loop Functionality                       | 221 |

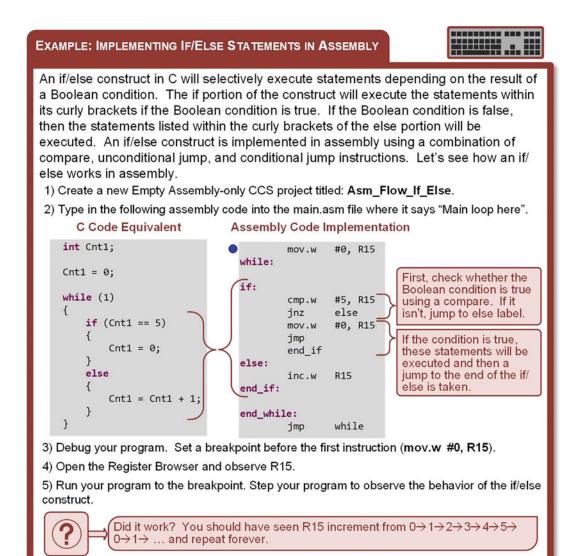

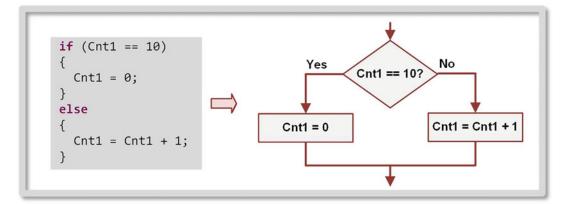

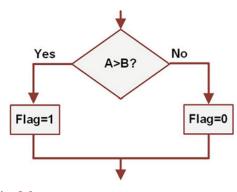

| 8.3.3            | Implementing If/Else Functionality                          | 223 |

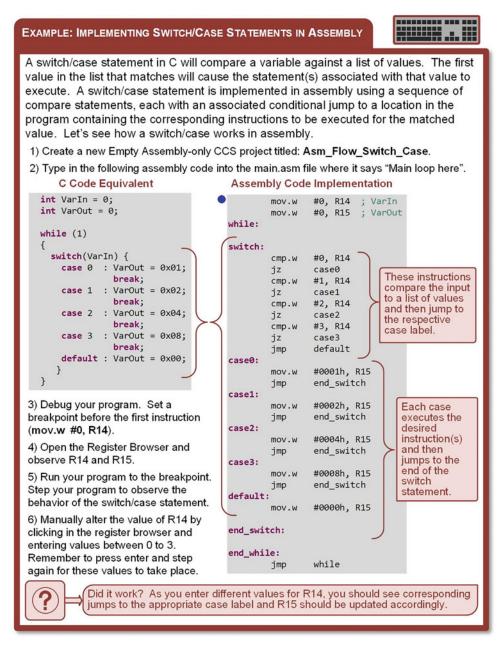

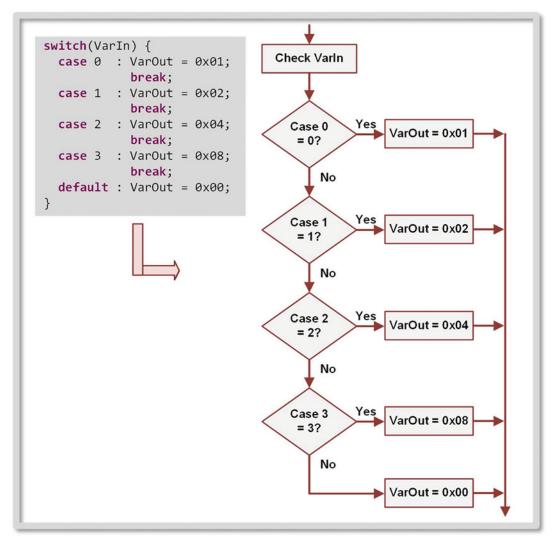

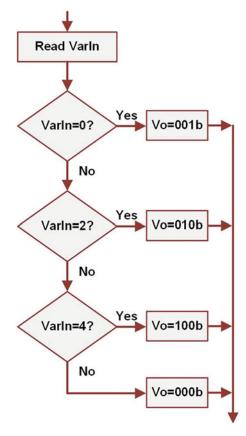

| 8.3.4            | Implementing Switch/Case Functionality in Assembly          | 224 |

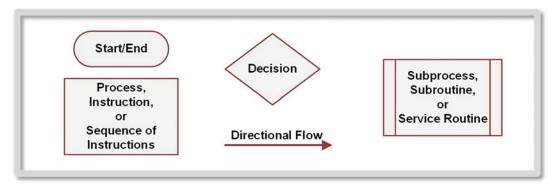

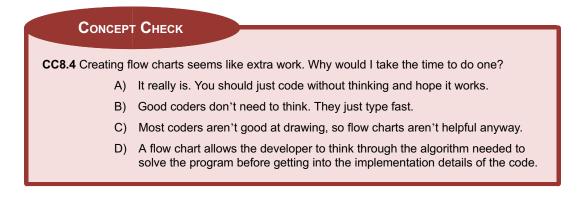

| 8.4 FLOV         | / CHARTS                                                    | 225 |

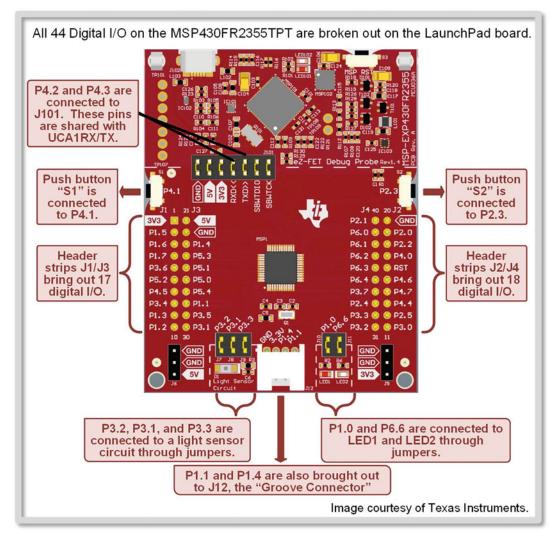

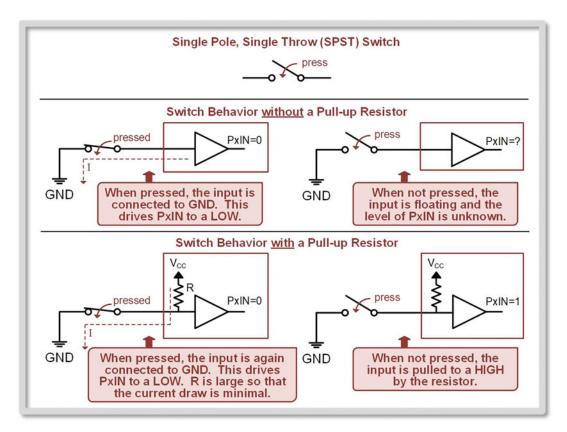

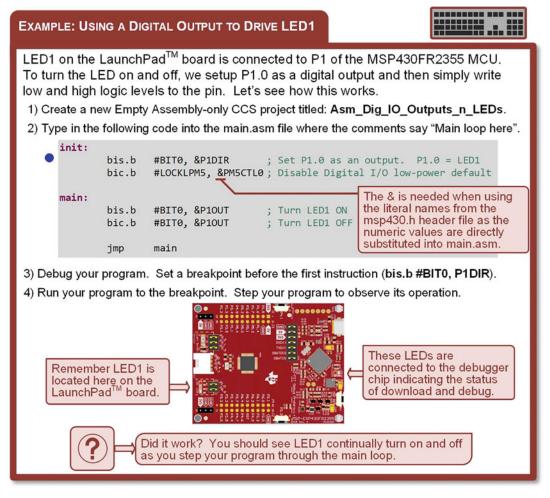

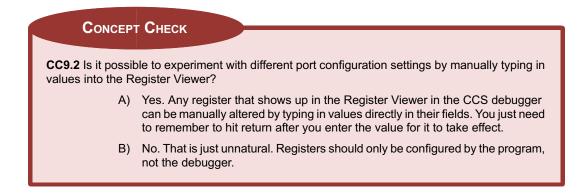

| 9: DIGITAL       | I/O                                                         | 231 |

| 04 T             |                                                             | 004 |

|                  | MSP430 DIGITAL I/O SYSTEM                                   |     |

| 9.1.1            | Port Direction Registers (PxDIR)                            |     |

| 9.1.2            | Port Input Registers (PxIN)                                 |     |

| 9.1.3            | Port Output Registers (PxOUT)                               |     |

| 9.1.4            | Port Pull-up or Pull-down Resistor Enable Registers (PxREN) |     |

| 9.1.5            | Port Function Select Registers (PxSEL1 and PxSEL0)          |     |

| 9.1.6            | Digital I/O Enabling After Reset                            |     |

| 9.1.7            | Using Literal Definitions from the MSP430.H Header File     |     |

|                  | al Output Programming                                       |     |

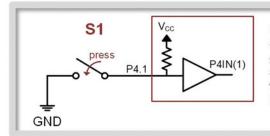

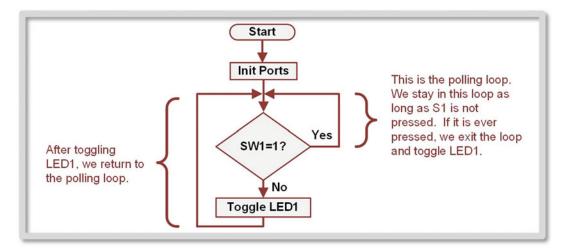

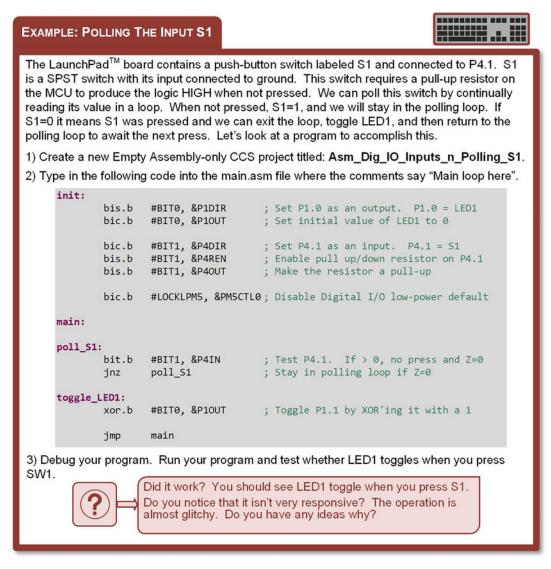

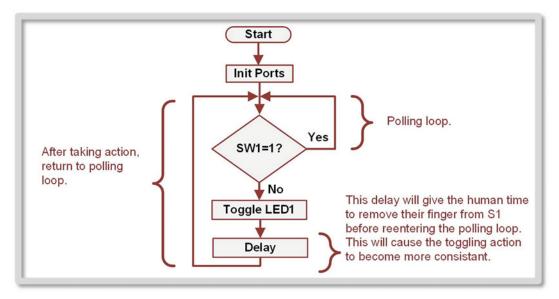

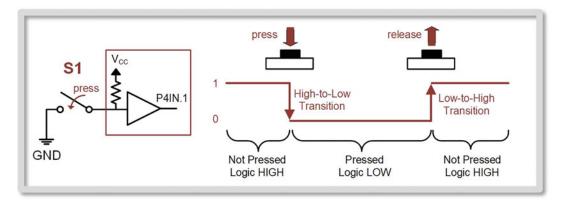

| 9.3 Digit        | al Input Programming                                        | 240 |

| 10: THE ST       | ACK AND SUBROUTINES                                         | 247 |

| 10 1 Tн⊧         | Stack                                                       | 247 |

|                  | ROUTINES                                                    |     |

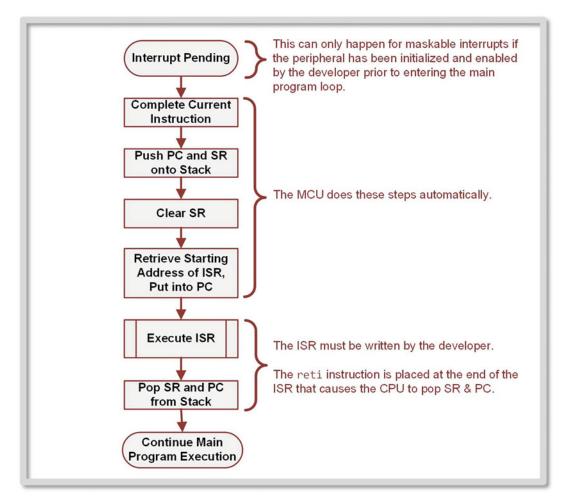

|                  | DUCTION TO INTERRUPTS                                       |     |

| 44 4 Tu-         |                                                             | 055 |

|                  | CONCEPT OF AN INTERRUPT                                     |     |

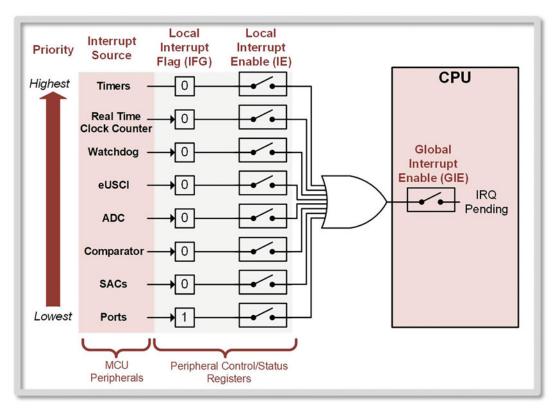

|                  | Interrupt Flags (IFG)                                       |     |

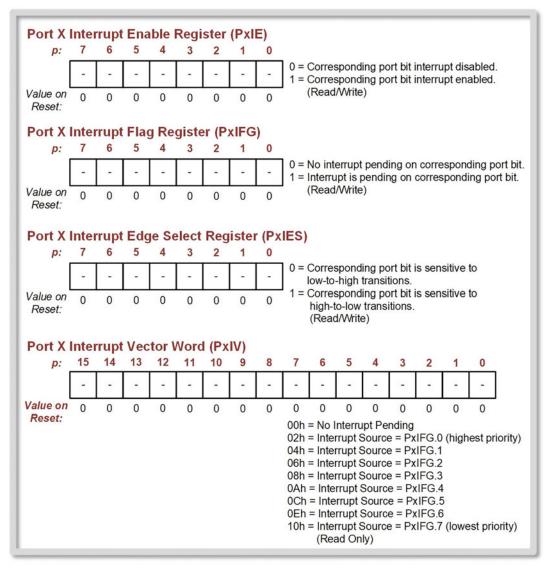

|                  | Interrupt Priority and Enabling                             |     |

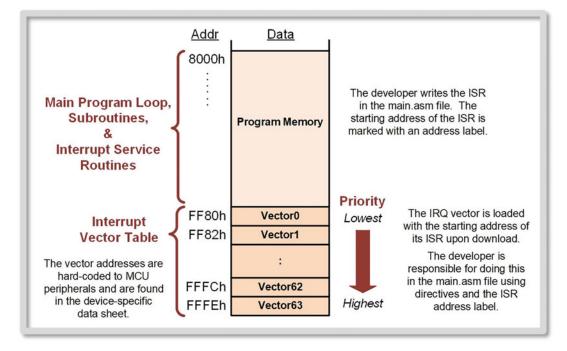

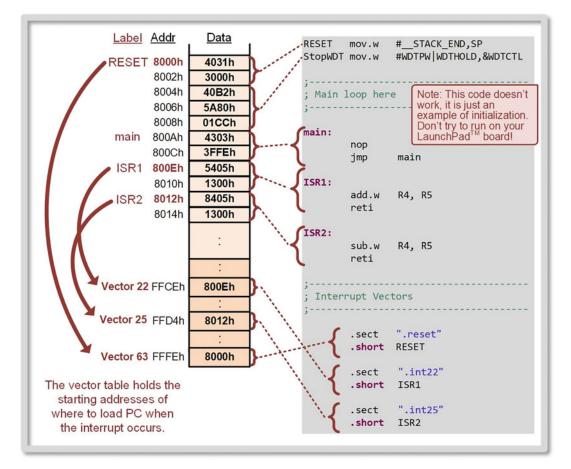

|                  | Interrupt Vectors                                           |     |

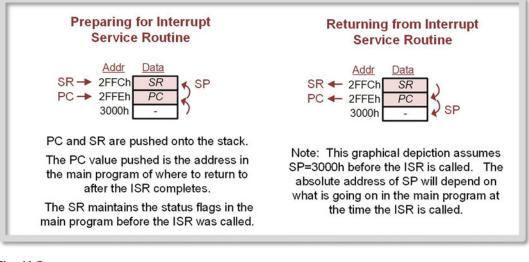

|                  | Operation of the Stack during an IRQ                        |     |

|                  | Interrupt Service Routines (ISR)                            |     |

|                  | Nested Interrupts                                           |     |

|                  | Interrupt Servicing Summary                                 |     |

|                  | MSP430FR2355 Interrupts                                     |     |

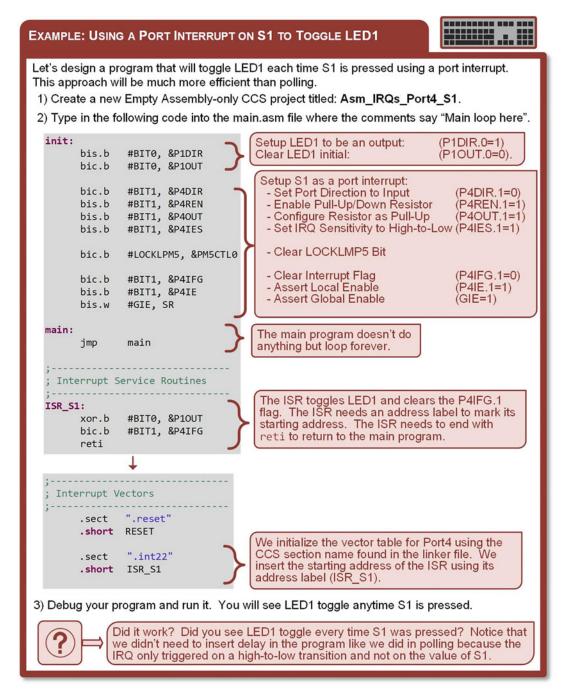

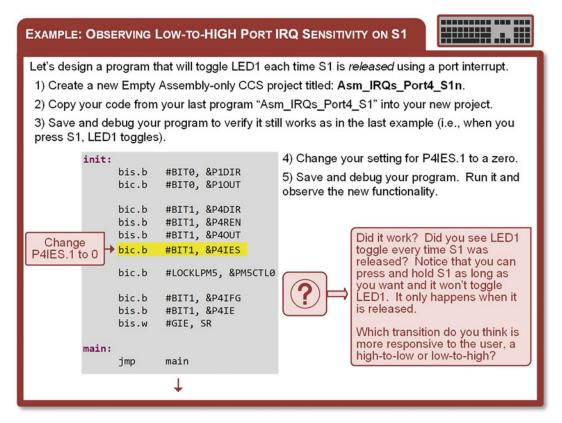

| 11.2 MSF         | 430FR2355 Port Interrupts                                   | 265 |

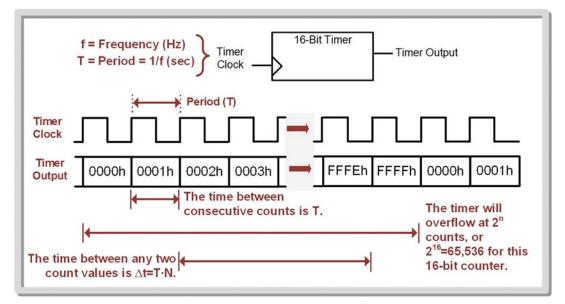

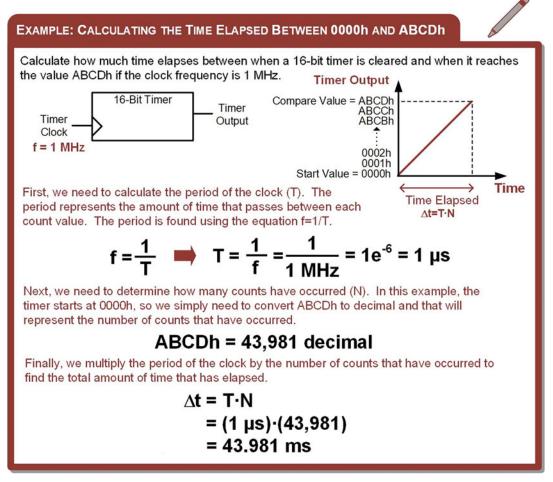

| 12: INTRO        | DUCTION TO TIMERS                                           | 273 |

| 12.1 TIME        | R OVERVIEW                                                  | 273 |

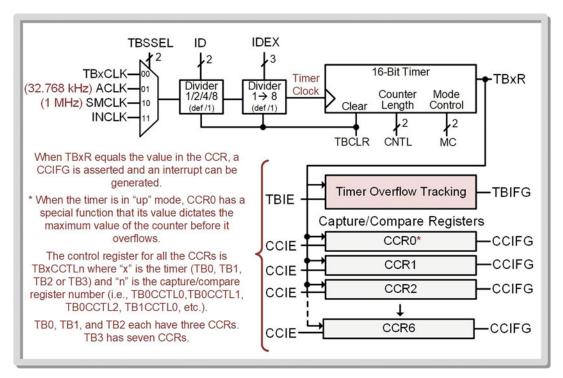

| 12.2 TIME        | R OVERFLOWS ON THE MSP430FR2355                             | 278 |

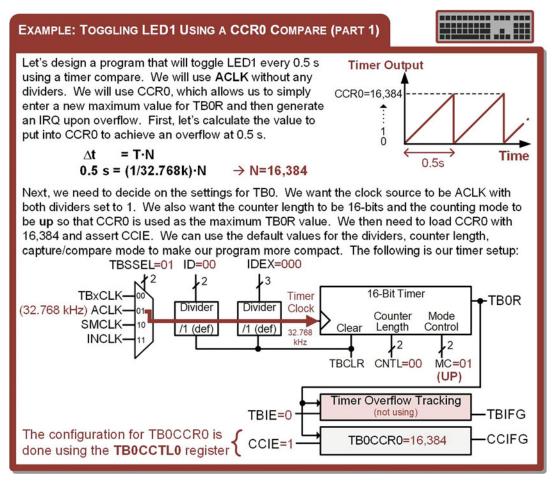

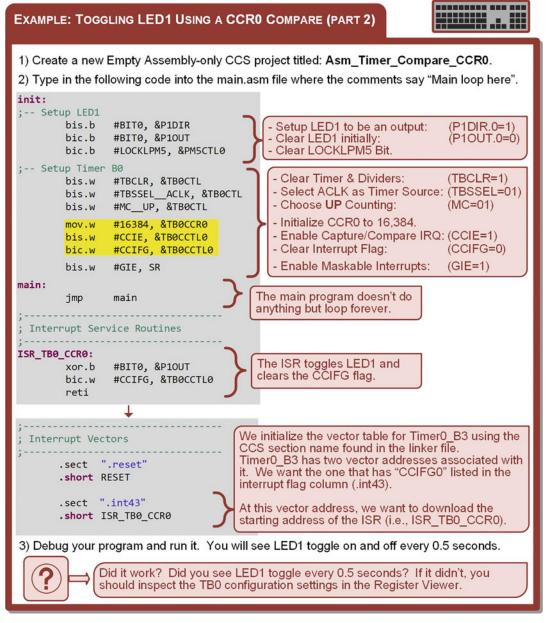

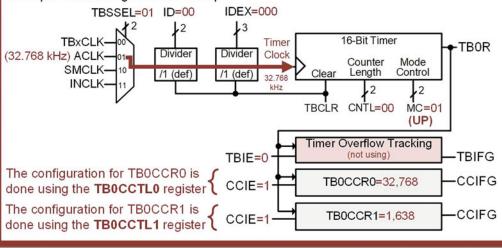

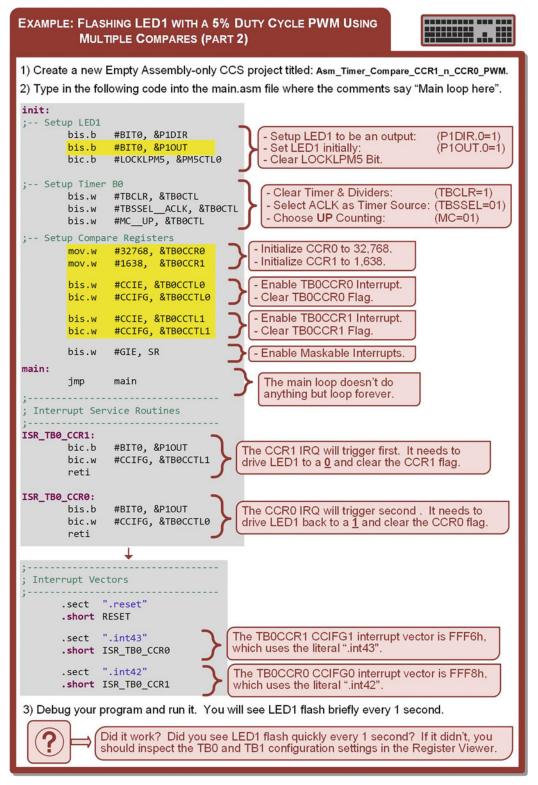

|                  | R COMPARES ON THE MSP430FR2355                              |     |

|                  | ATING PULSE WIDTH MODULATED SIGNALS USING TIMER COMPARES    |     |

|                  | R CAPTURES ON THE MSP430FR2355                              |     |

| 13: <b>SWITC</b> | HING TO THE C LANGUAGE                                      | 301 |

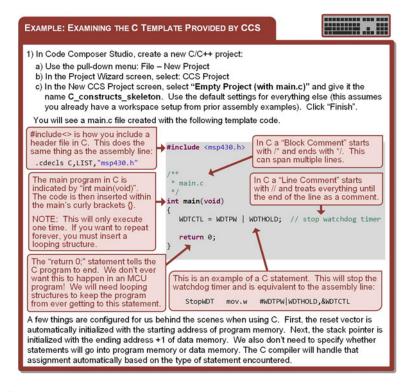

| 13 1 BASE        | CS OF C PROGRAMMING ON THE MSP430                           | 301 |

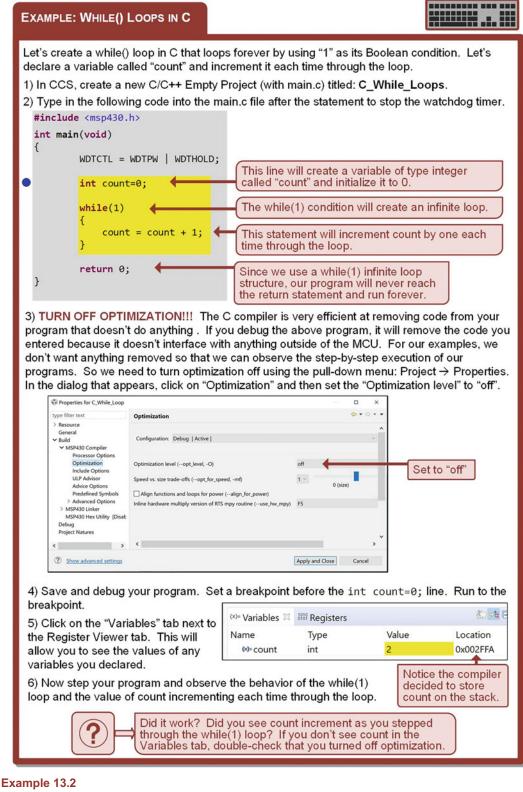

|                  | While() Loops in C                                          |     |

|                  |                                                             |     |

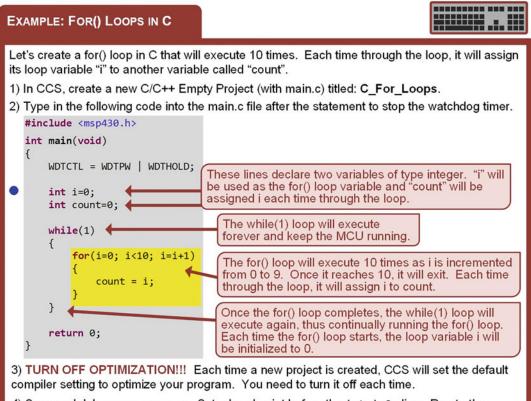

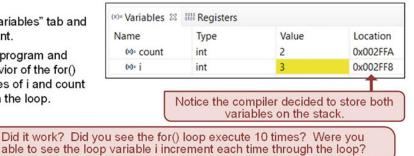

| 13.1.2 For() Loops in C                                           |     |

|-------------------------------------------------------------------|-----|

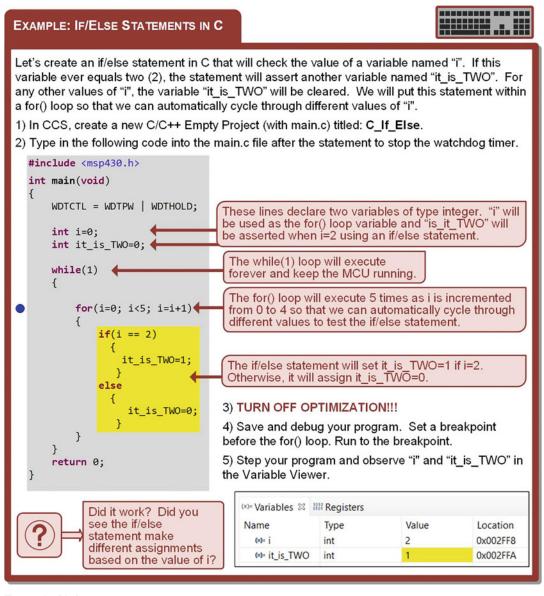

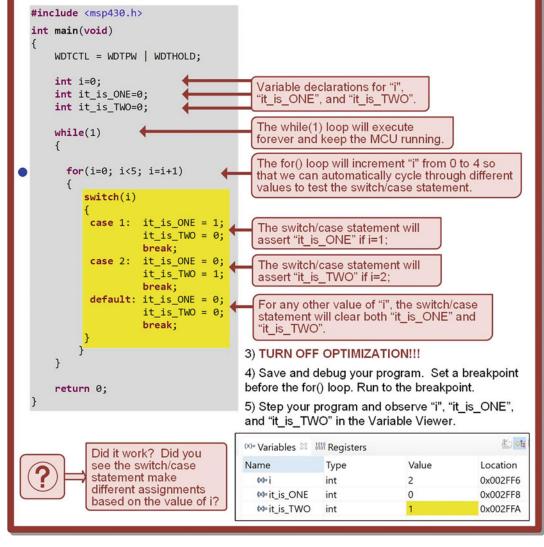

| 13.1.3 If/Else Statements in C                                    | 305 |

| 13.1.4 Switch/Case Statements in C                                | 306 |

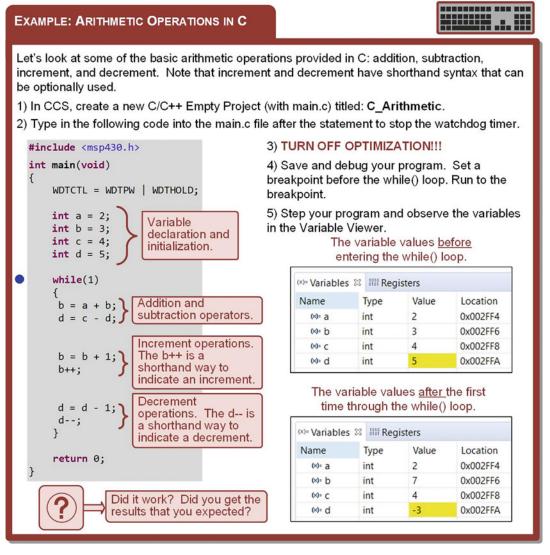

| 13.1.5 Arithmetic Operators in C                                  | 307 |

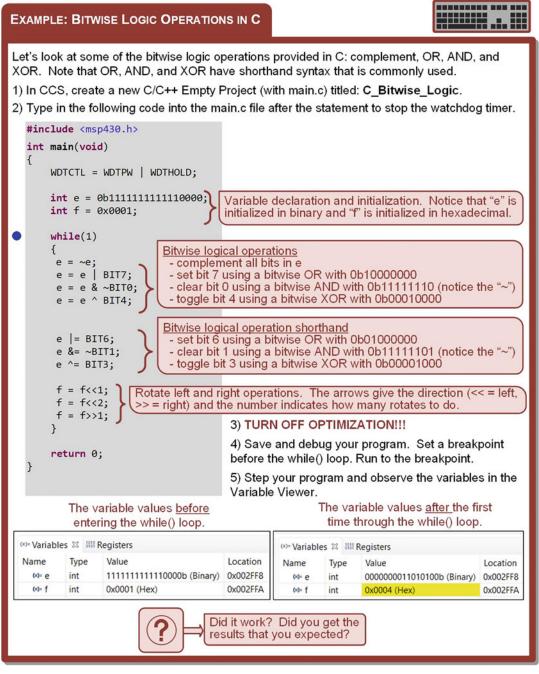

| 13.1.6 Bitwise Logic Operators in C                               | 307 |

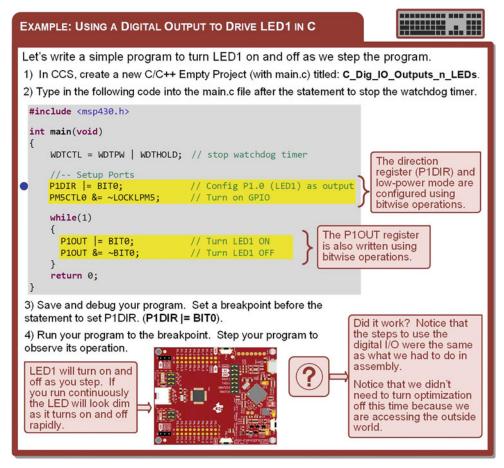

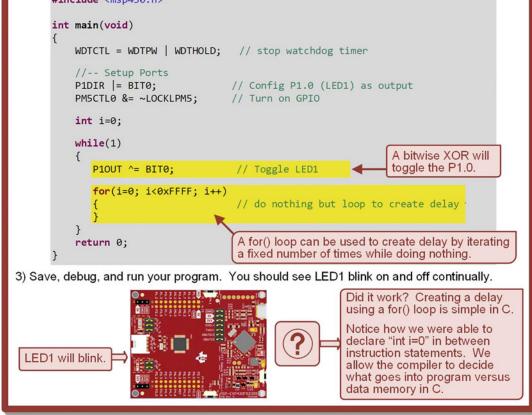

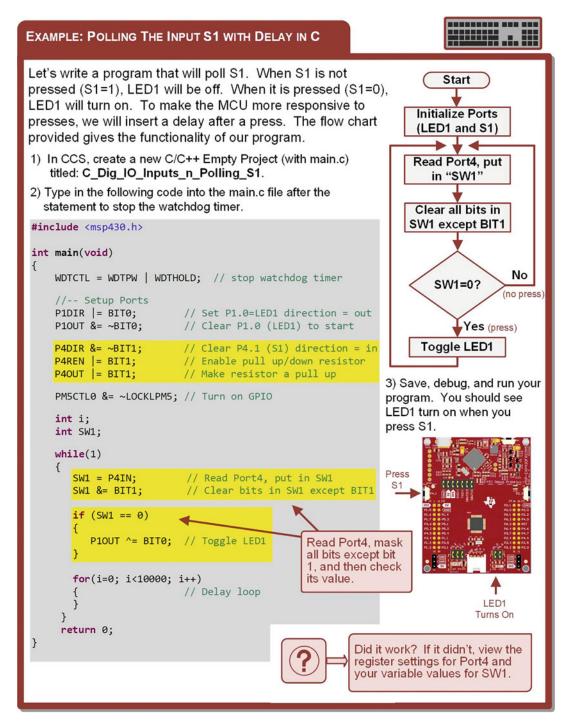

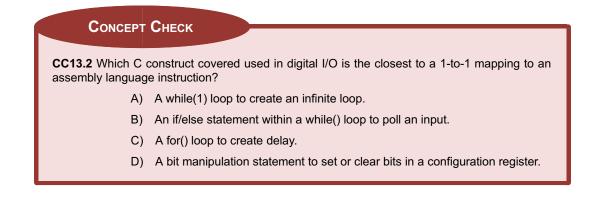

| 13.2 DIGITAL I/O IN C                                             | 310 |

| 13.3 INTERRUPTS IN C                                              | 313 |

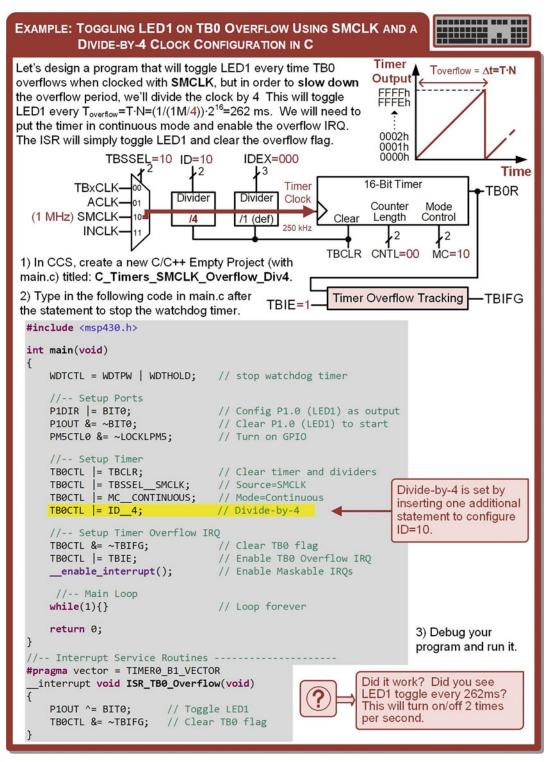

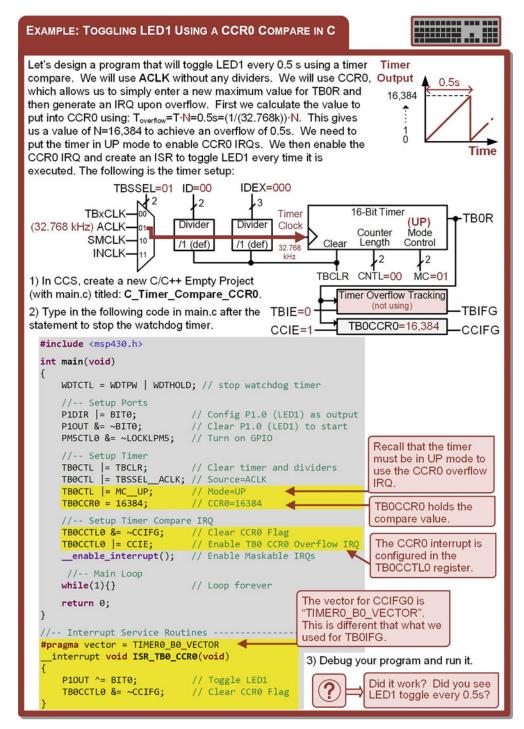

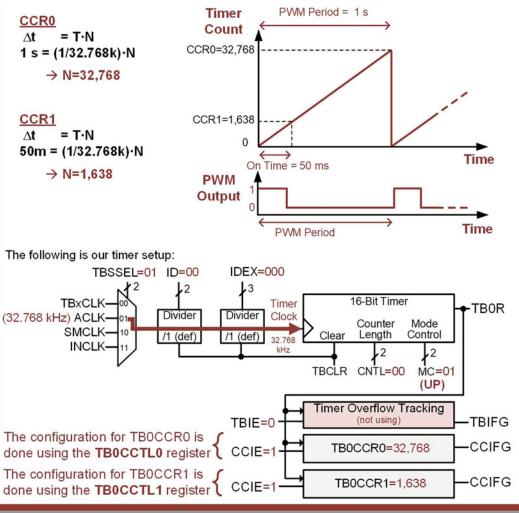

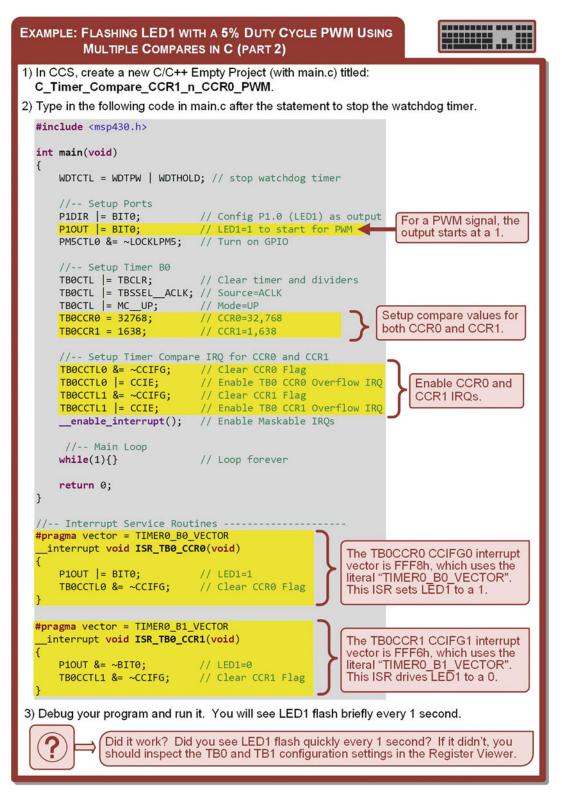

| 13.4 TIMERS IN C                                                  |     |

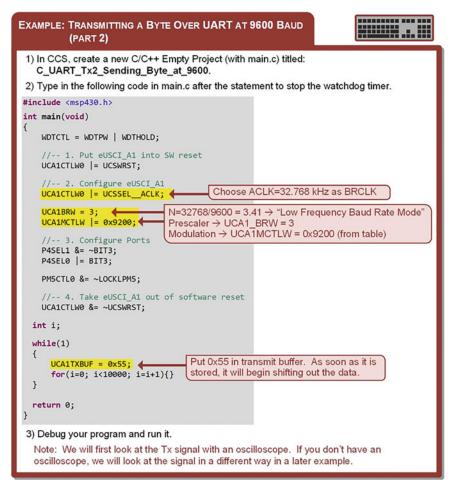

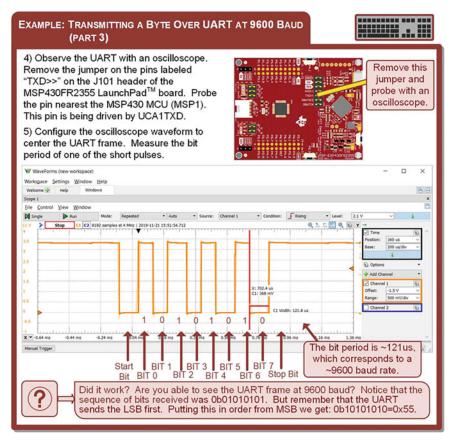

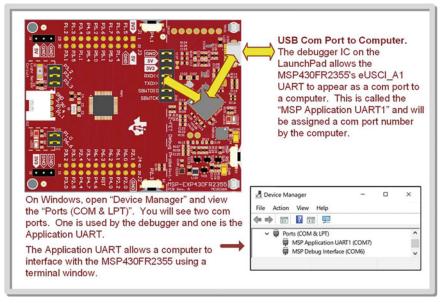

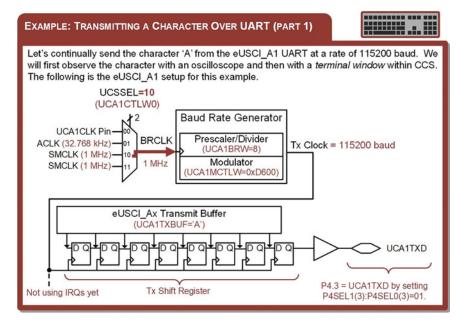

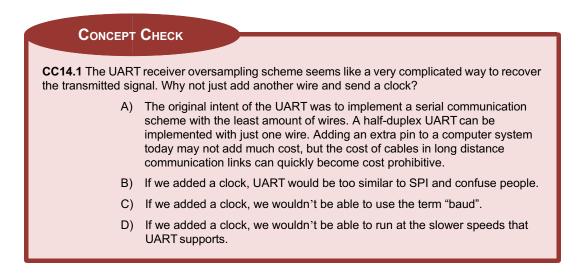

| 14: SERIAL COMMUNICATION IN C                                     | 327 |

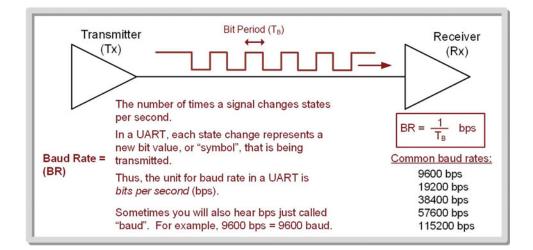

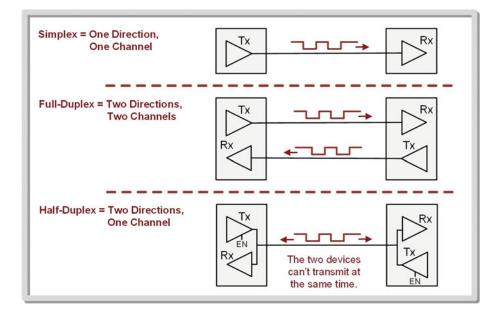

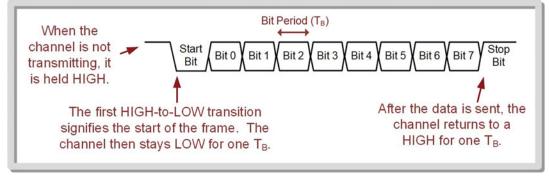

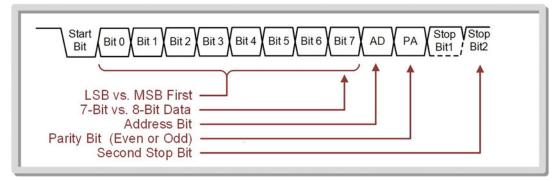

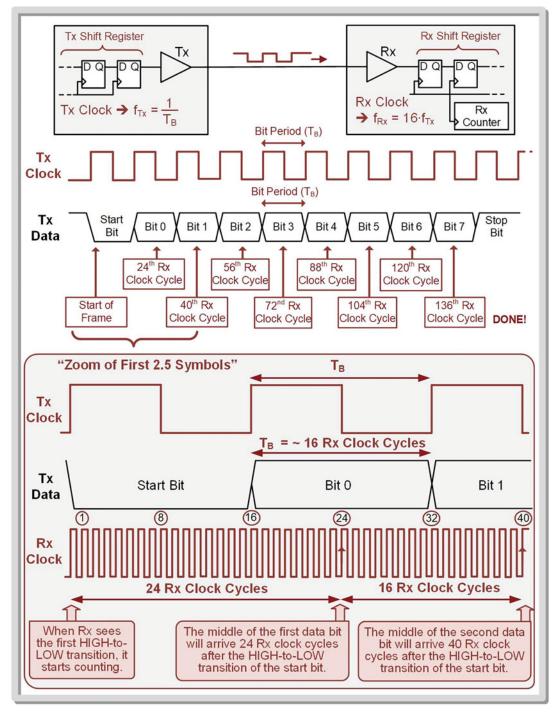

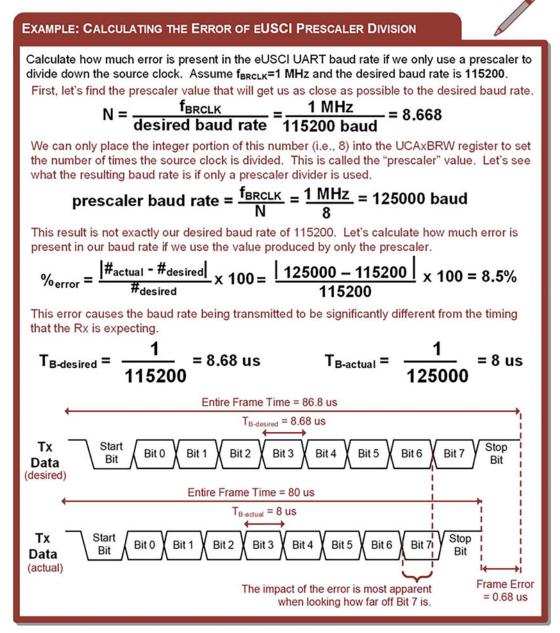

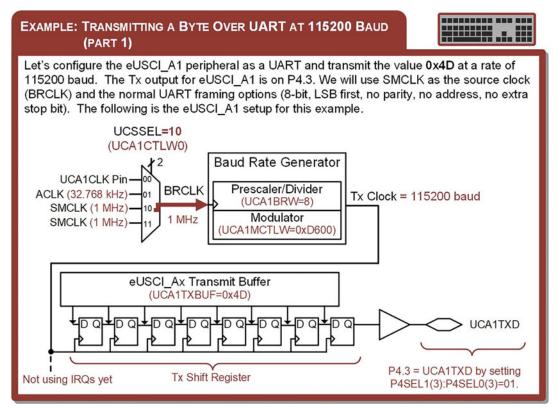

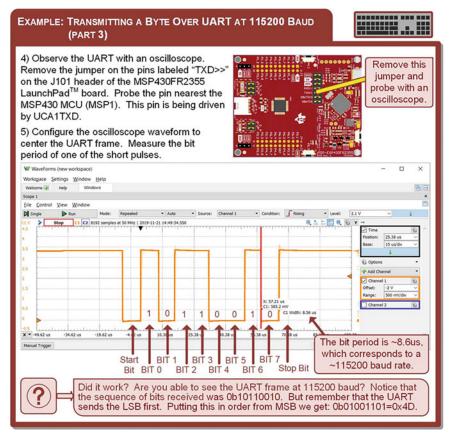

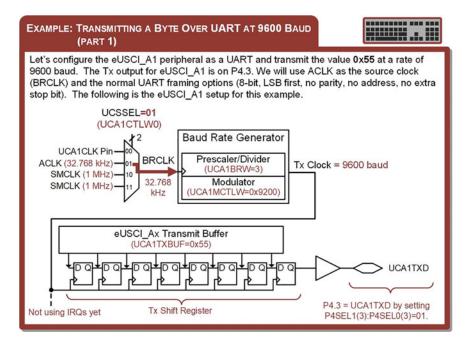

| 14.1 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART)           | 327 |

| 14.1.1 The UART Standard                                          |     |

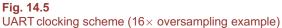

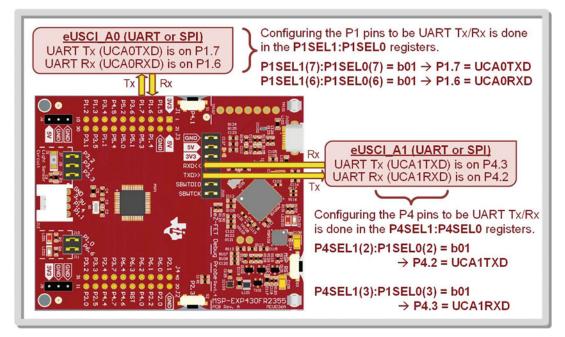

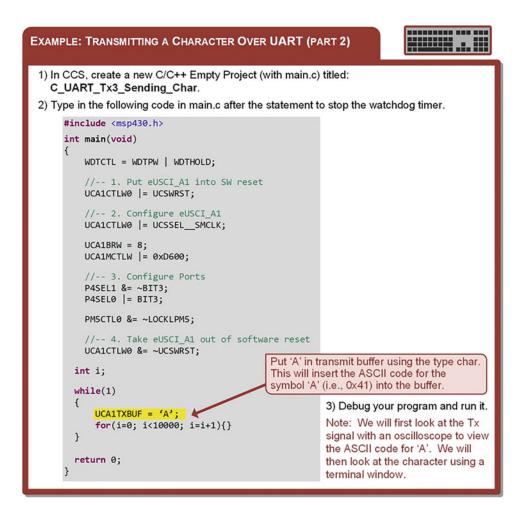

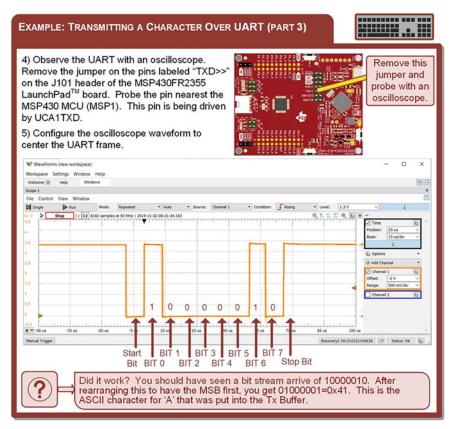

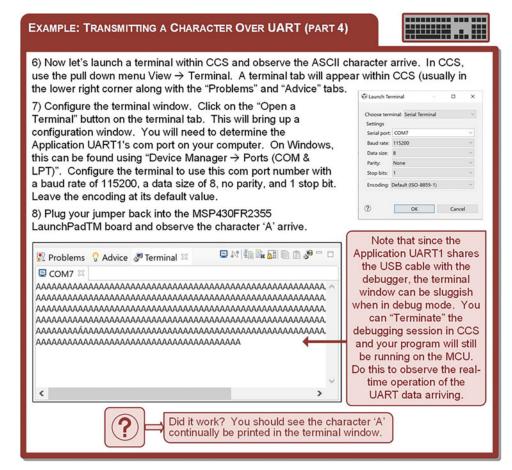

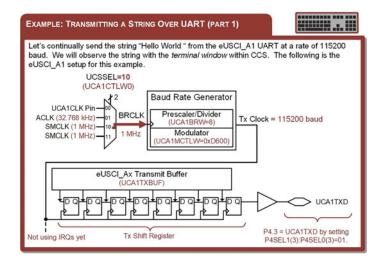

| 14.1.2 UART Transmit on the MSP430FR2355                          | 333 |

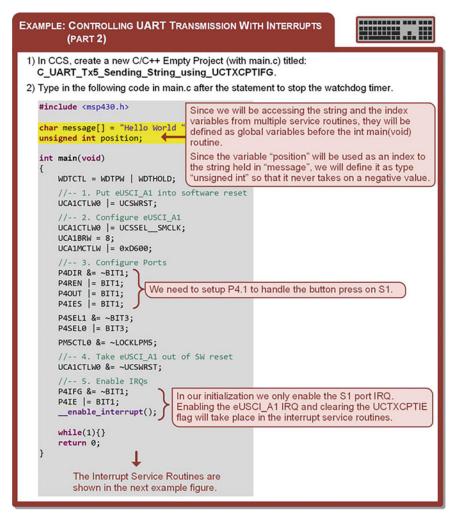

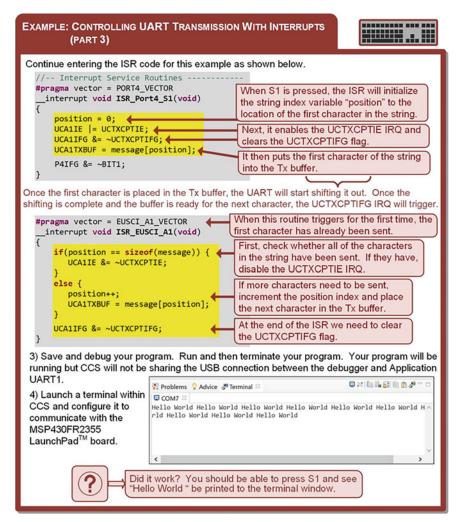

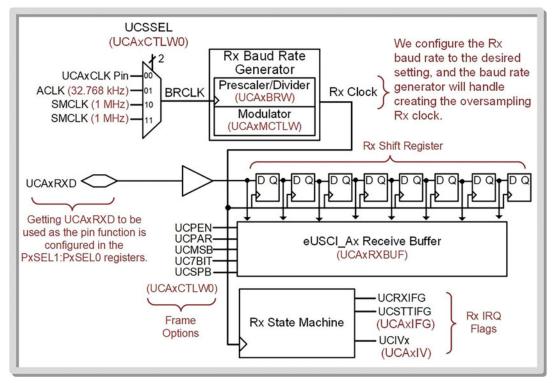

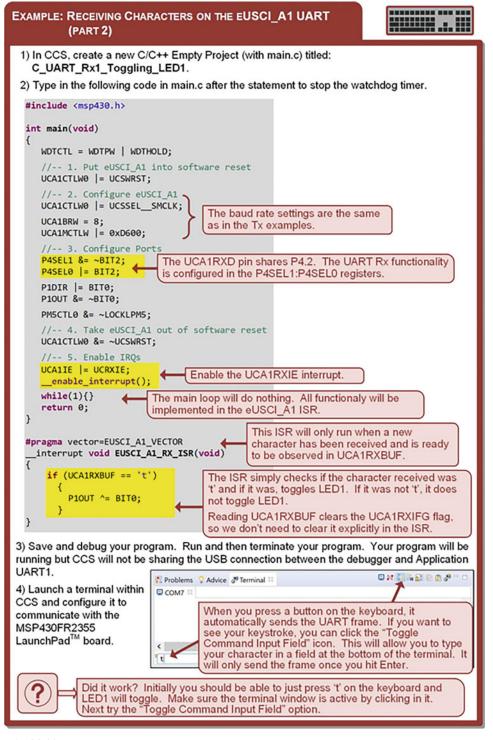

| 14.1.3 UART Receive on the MSP430FR2355                           | 355 |

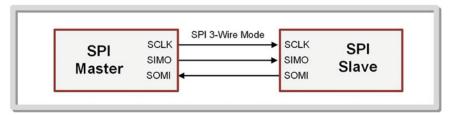

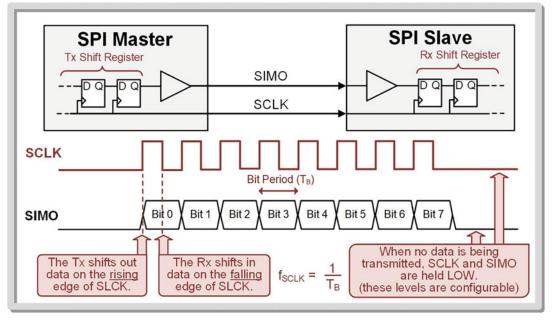

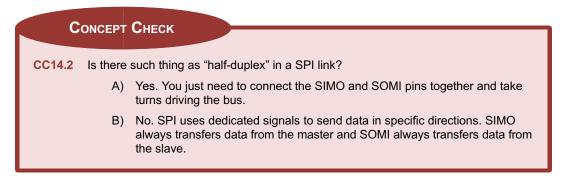

| 14.2 Serial Peripheral Interface (SPI)                            | 359 |

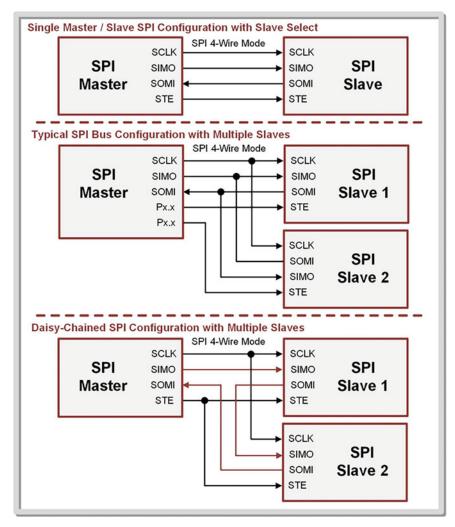

| 14.2.1 The SPI Protocol                                           | 359 |

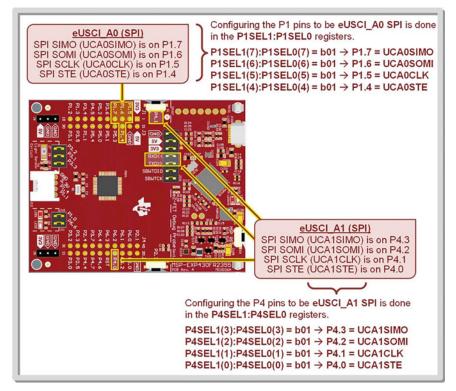

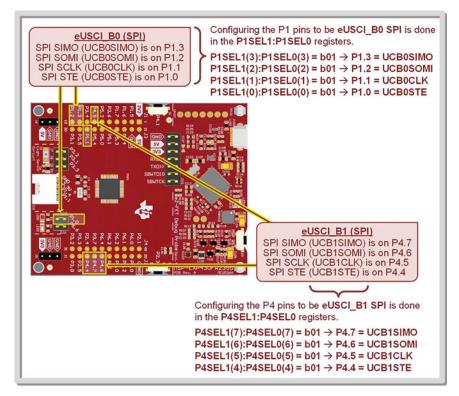

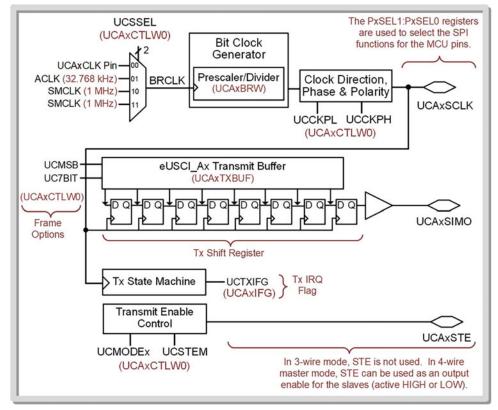

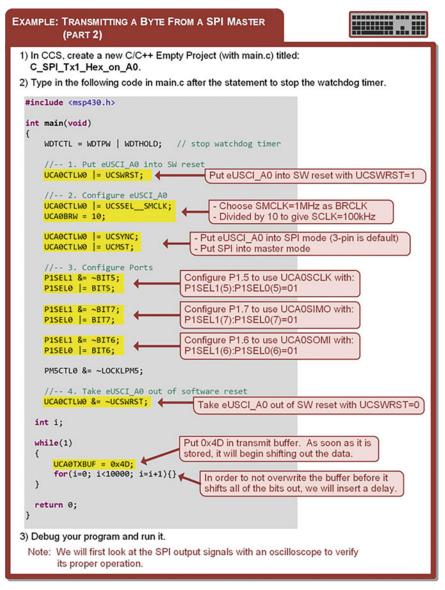

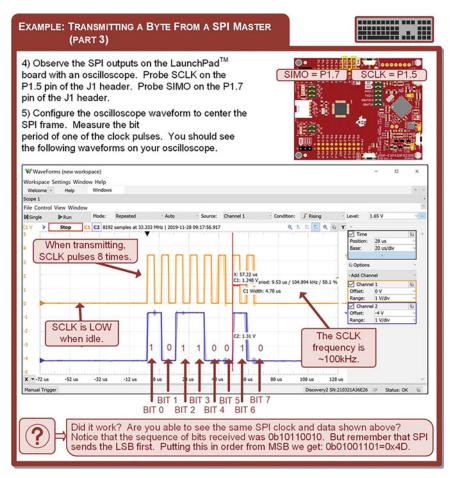

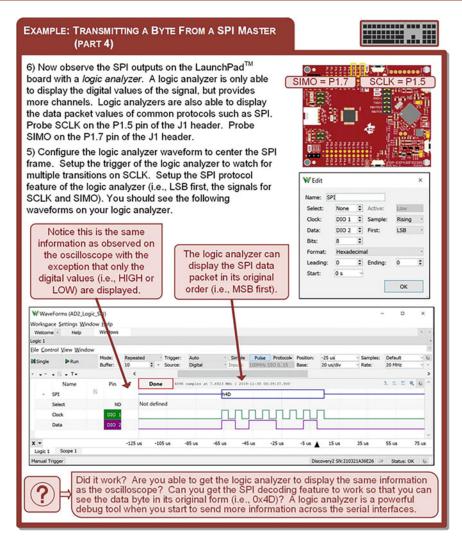

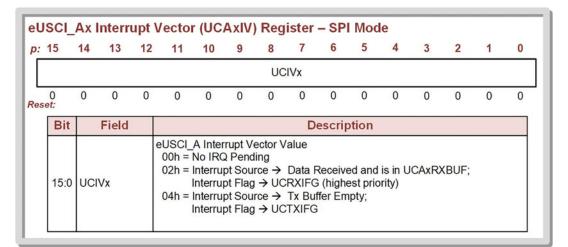

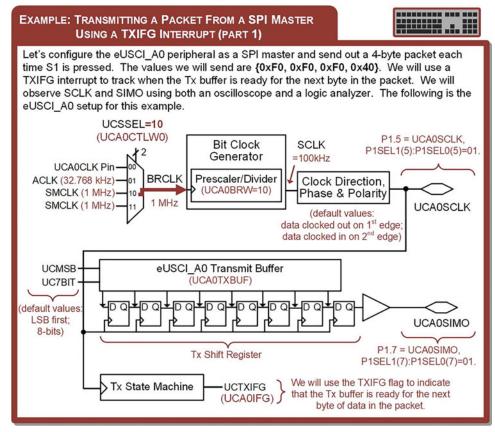

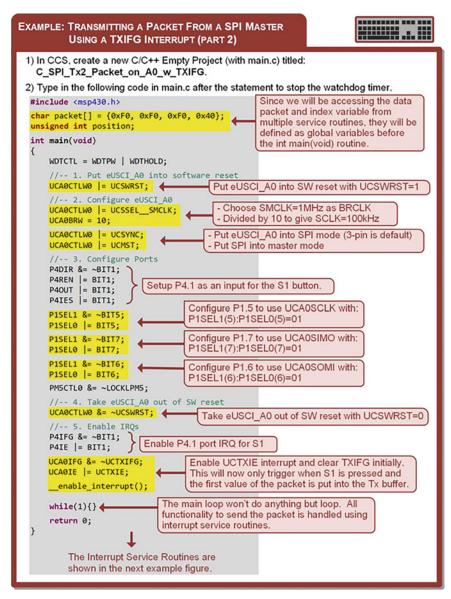

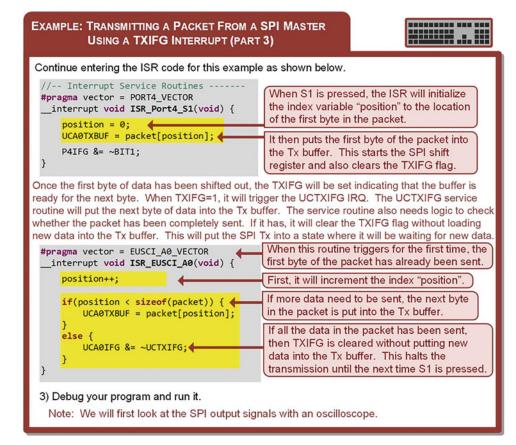

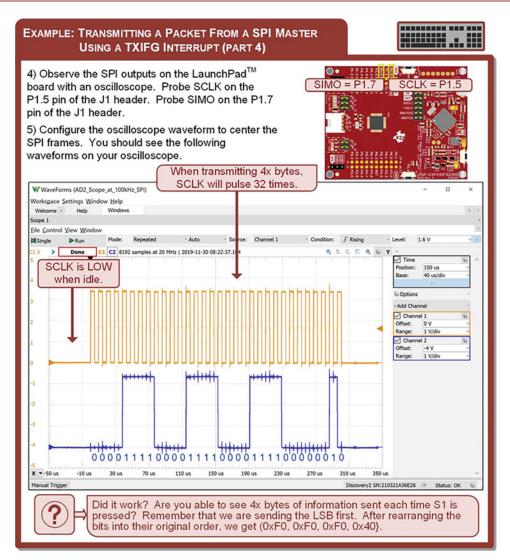

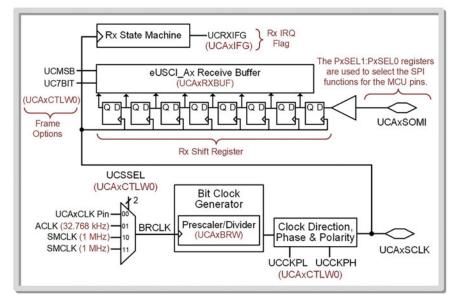

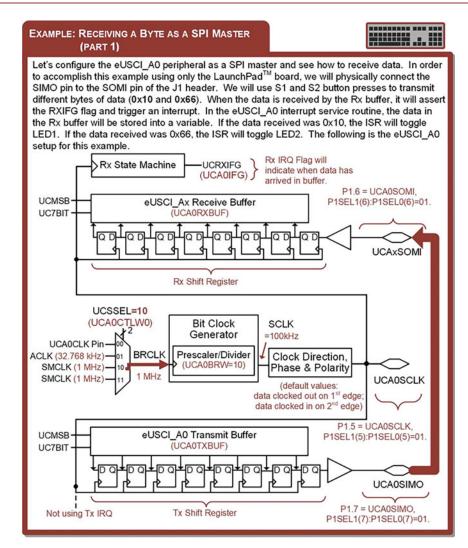

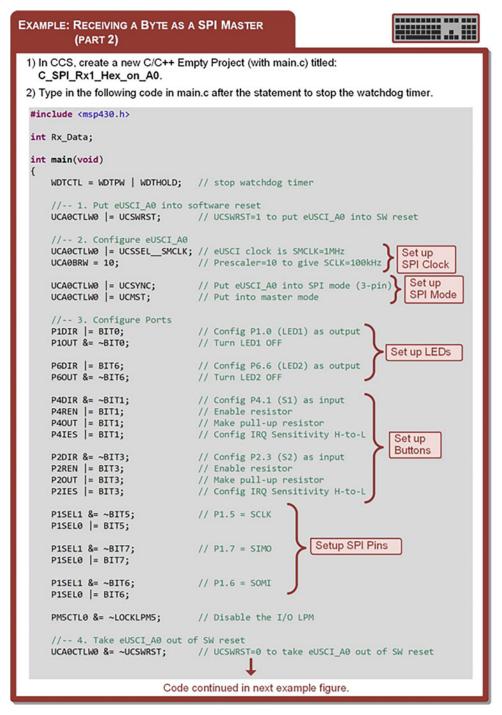

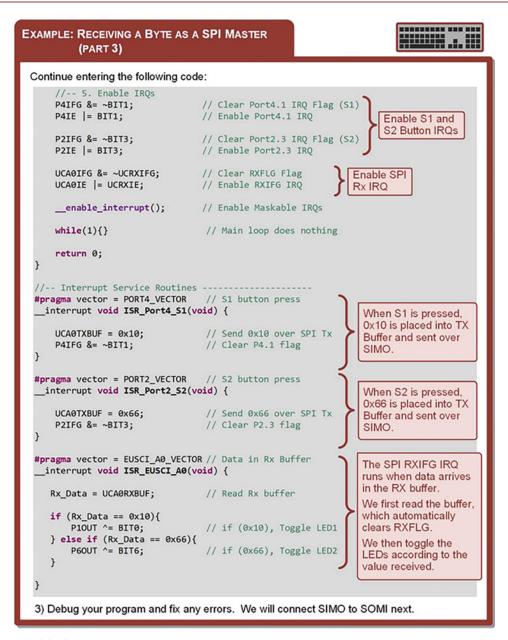

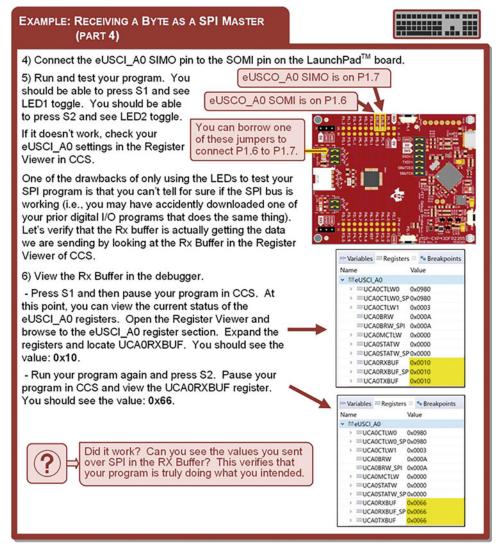

| 14.2.2 SPI Master Operation on the MSP430FR2355                   | 363 |

| 14.2.3 SPI Slave Operation on the MSP430FR2355                    | 384 |

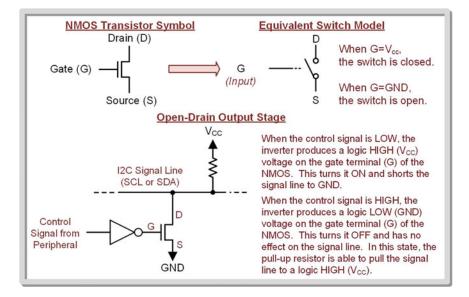

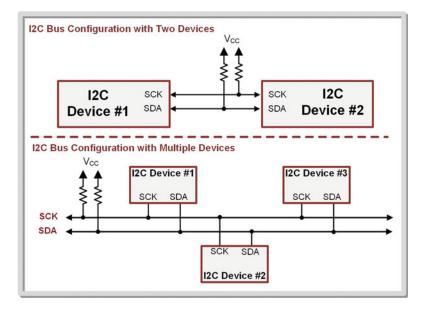

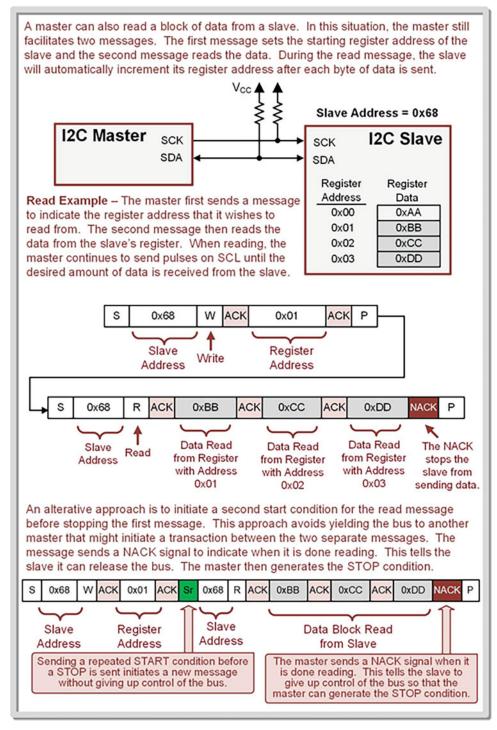

| 14.3 INTER-INTEGRATED CIRCUIT (I2C) BUS                           | 385 |

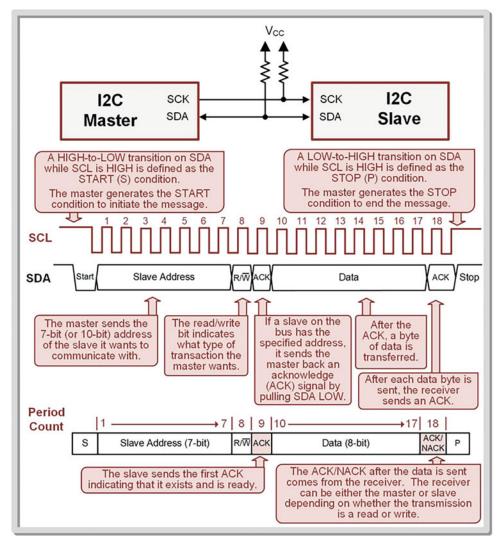

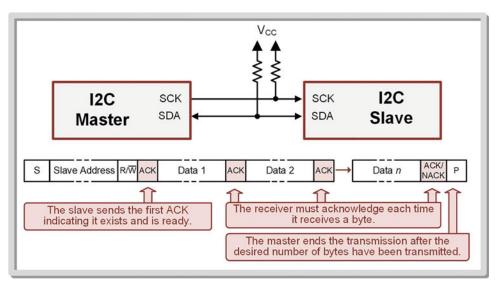

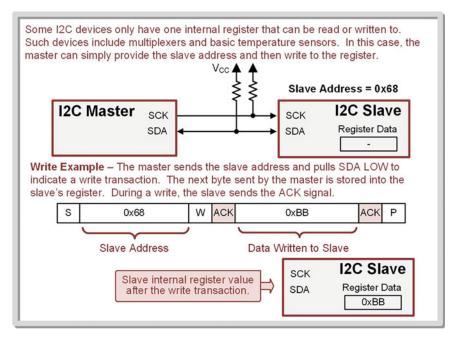

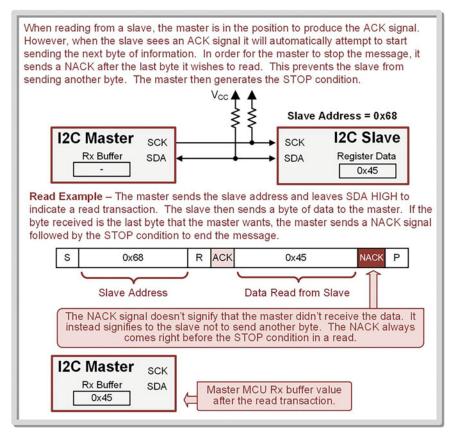

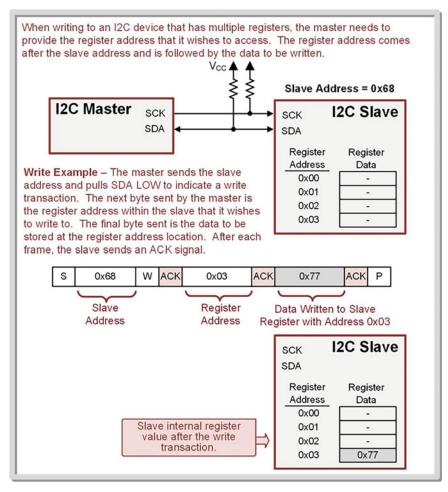

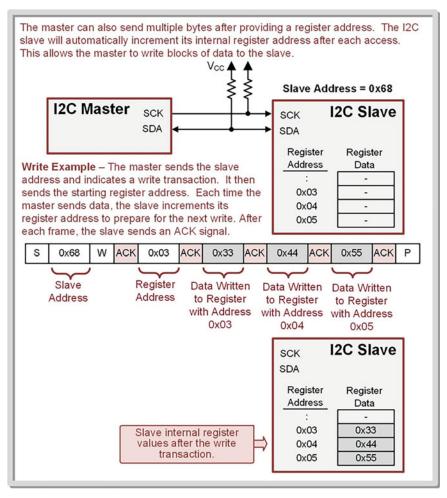

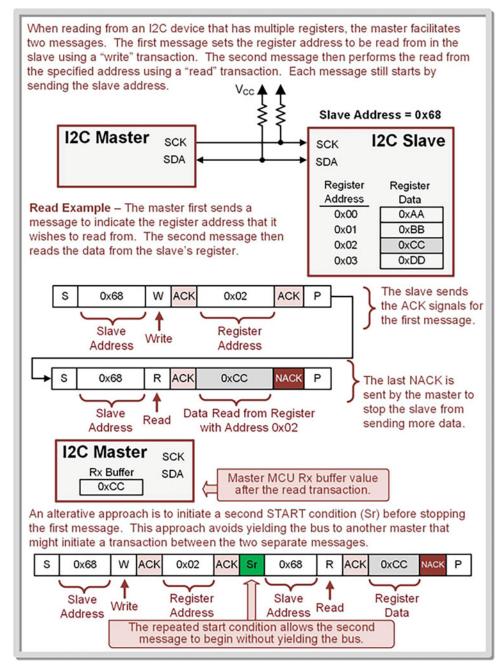

| 14.3.1 The I2C Protocol                                           | 385 |

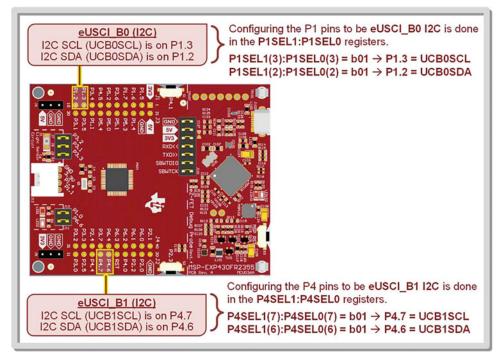

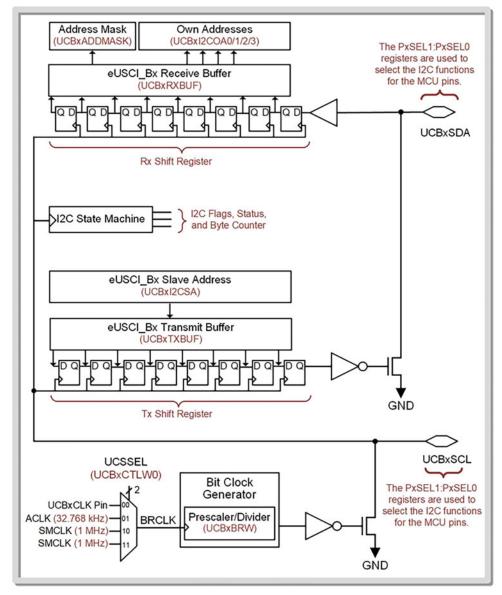

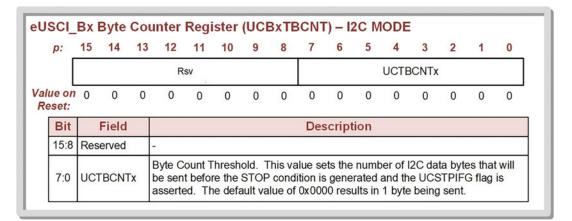

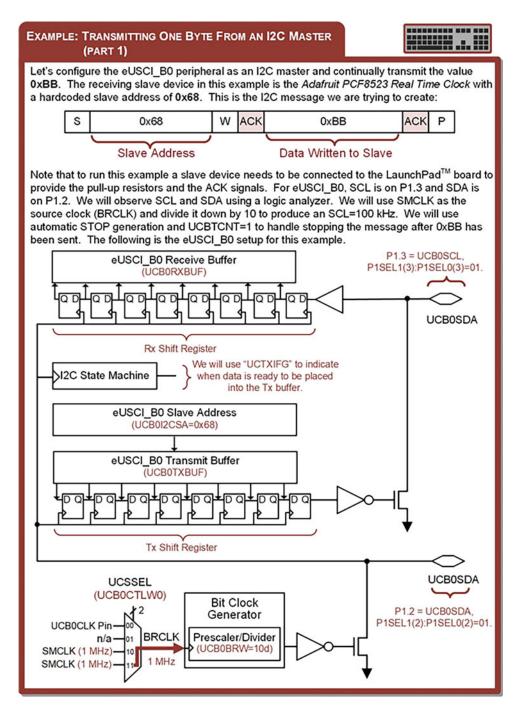

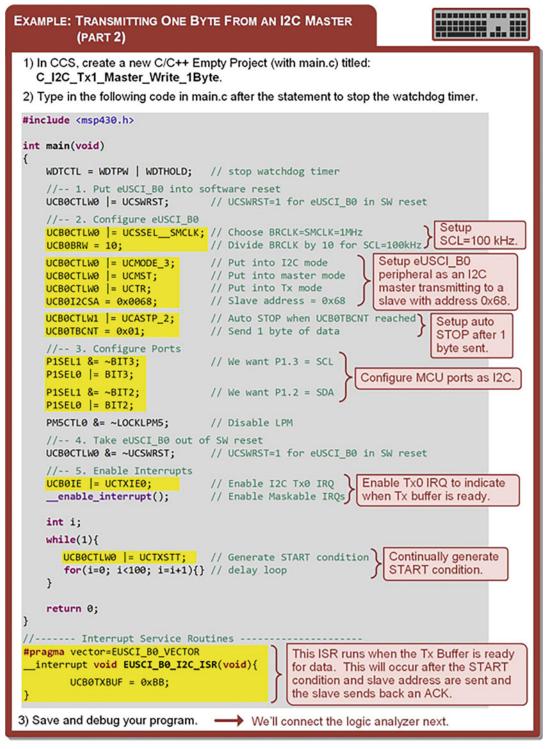

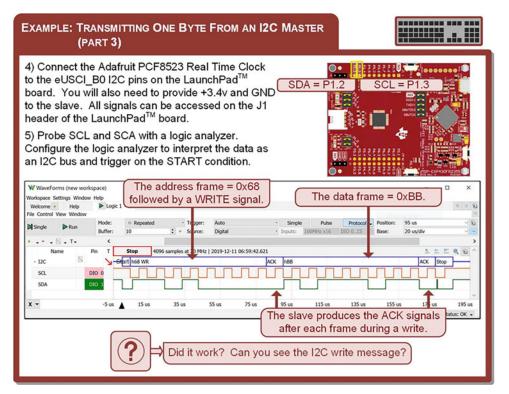

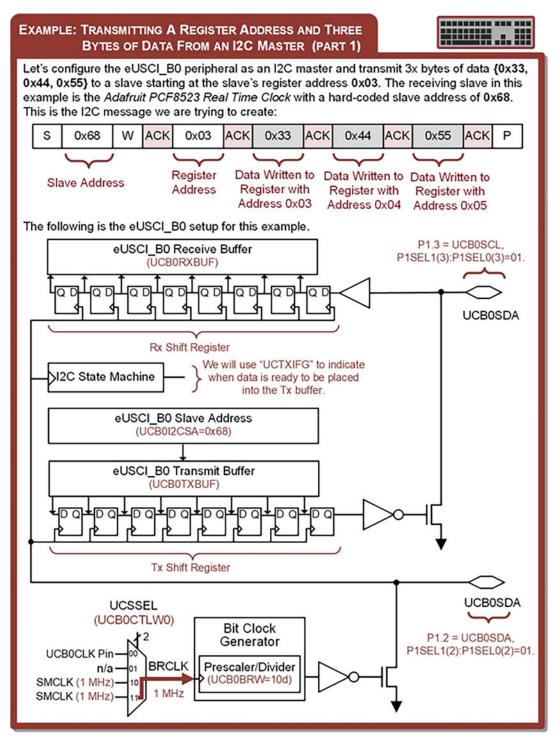

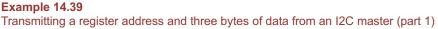

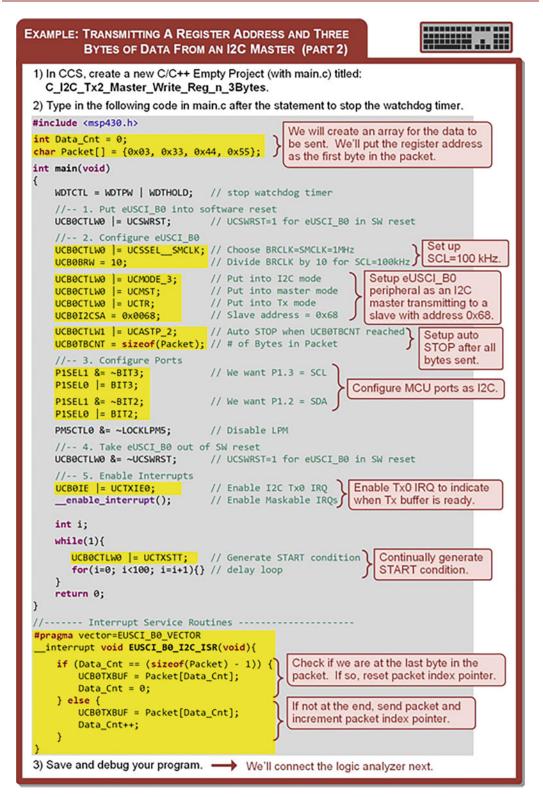

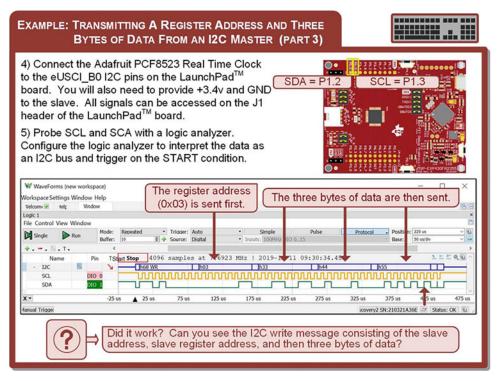

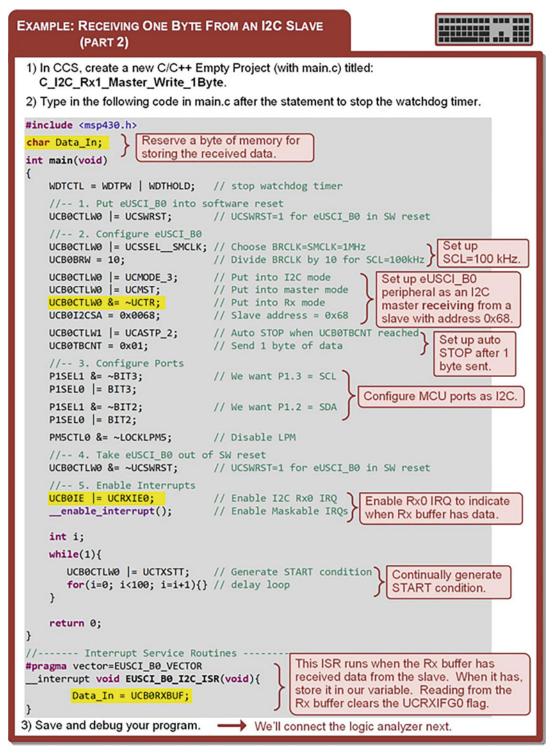

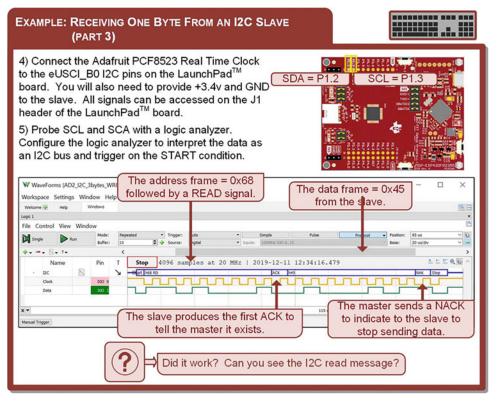

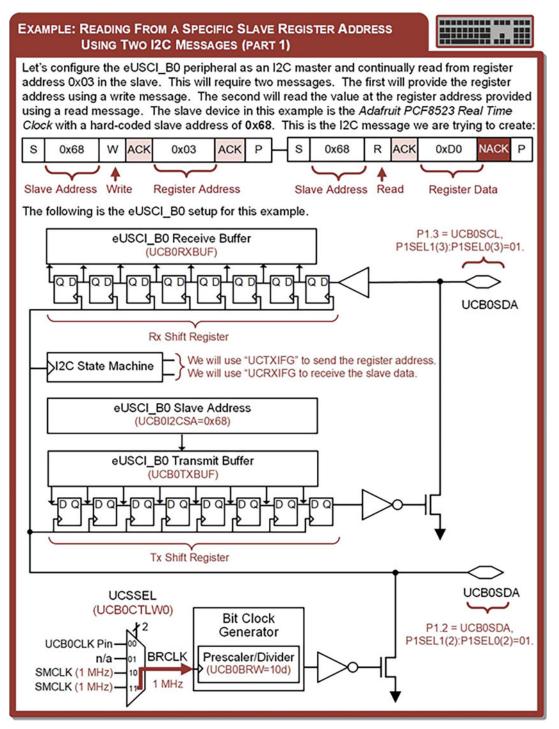

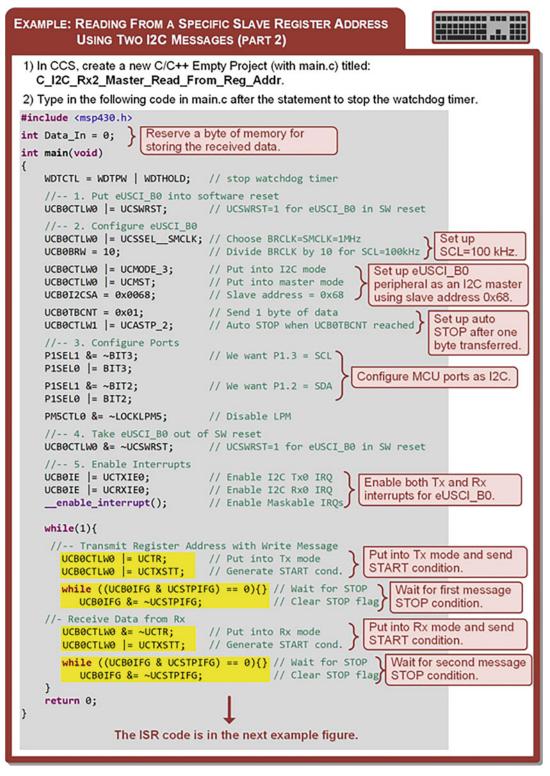

| 14.3.2 I2C Master Operation on the MSP430FR2355                   | 395 |

| 14.3.3 I2C Slave Operation on the MSP430FR2355                    | 417 |

| 15: ANALOG-TO-DIGITAL CONVERTERS                                  | 423 |

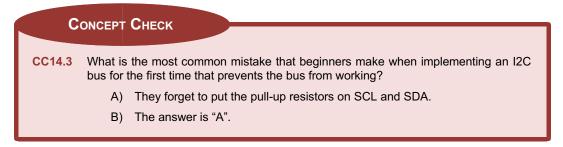

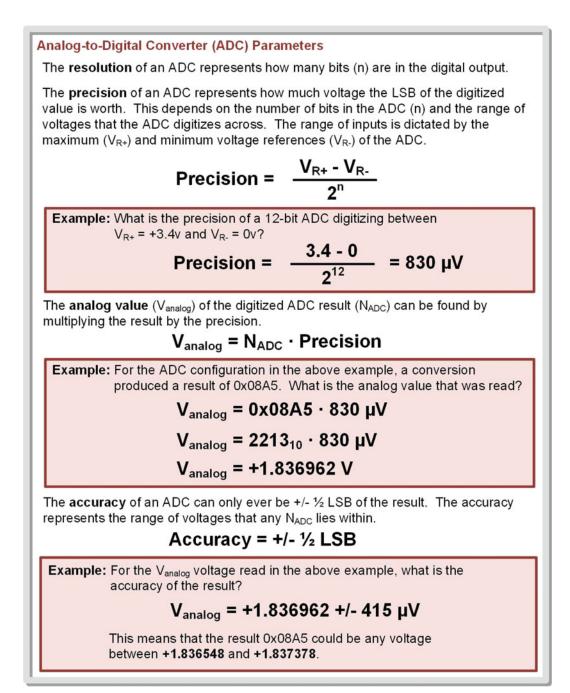

| 15.1 Analog-to-Digital Converters                                 | 423 |

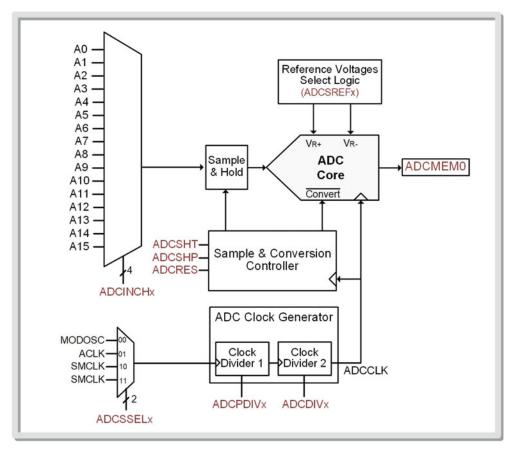

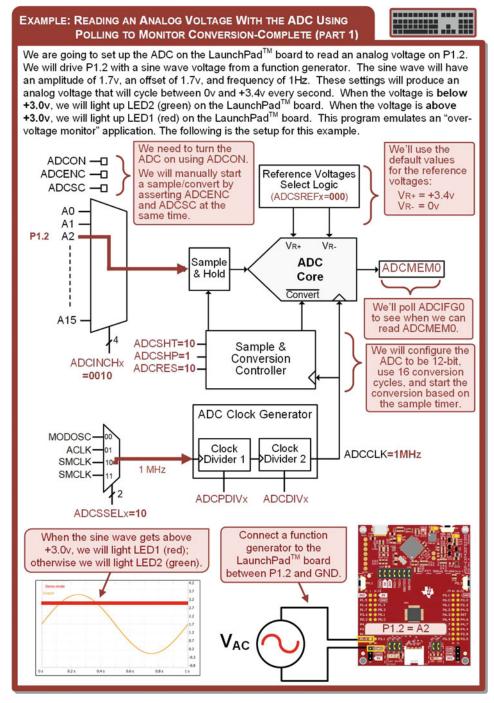

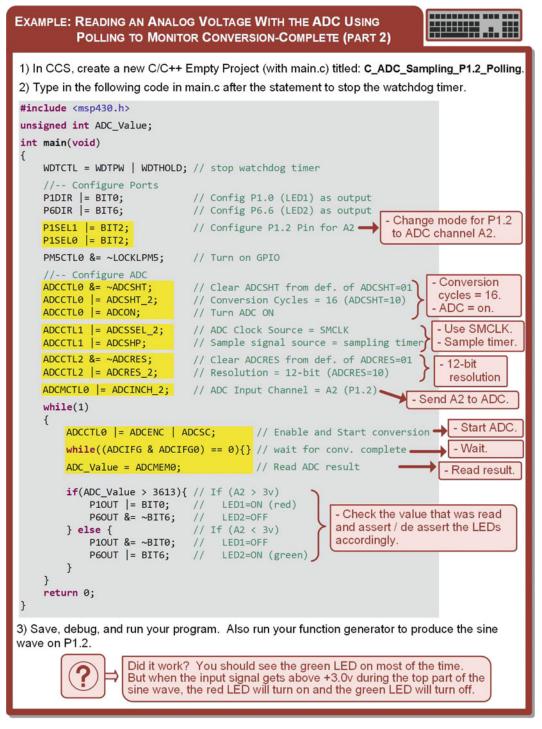

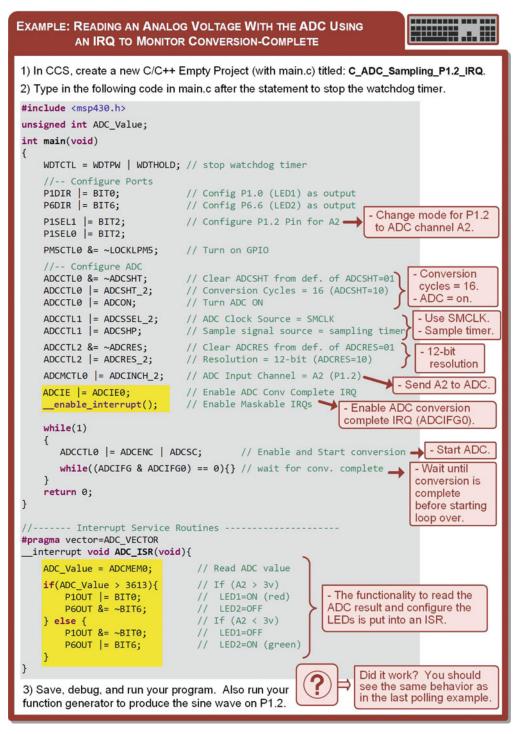

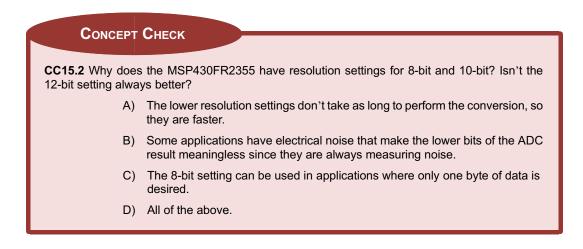

| 15.2 ADC OPERATION ON THE MSP430FR2355                            |     |

| 16: THE CLOCK SYSTEM                                              |     |

|                                                                   |     |

| 16.1 OVERVIEW OF THE MSP430FR2355 CLOCK SYSTEM                    |     |

| 16.1.1 Internal Very Low-Power Low-Frequency Oscillator (VLO)     |     |

| 16.1.2 Internal Trimmed Low-Frequency Reference Oscillator (REFO) |     |

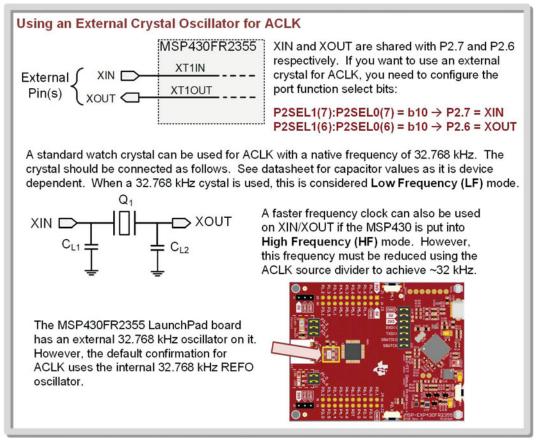

| 16.1.3 External XT1 Oscillator (XT1)                              |     |

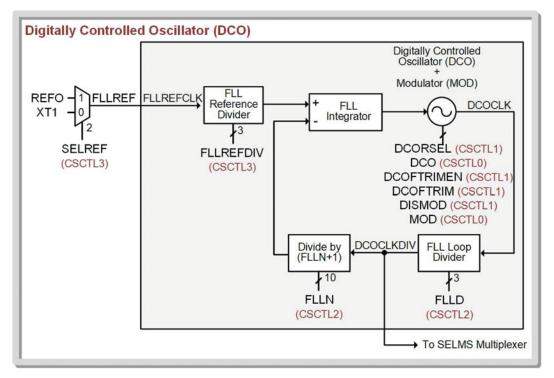

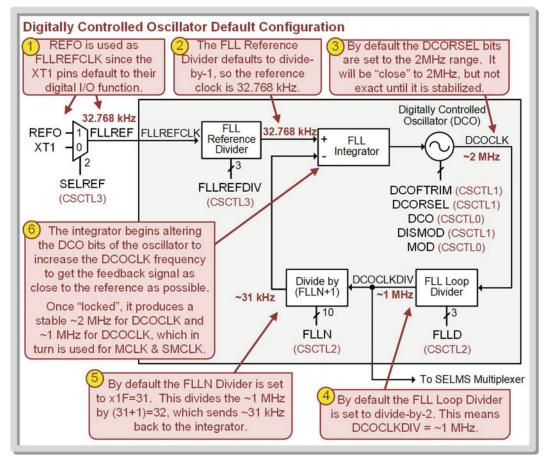

| 16.1.4 Internal Digitally Controlled Oscillator (DCO)             |     |

| 16.1.5 Internal High-Frequency Oscillator (MODCLK)                |     |

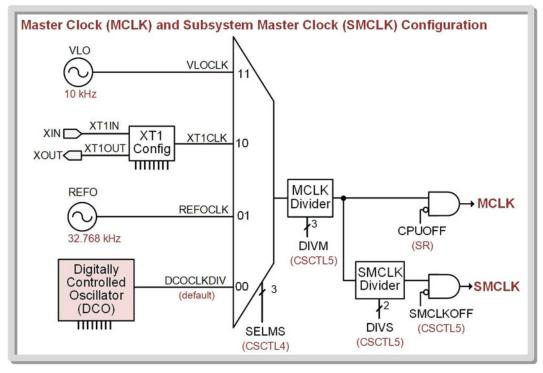

| 16.1.6 Master Clock (MCLK)                                        |     |

| 16.1.7 Subsystem Master Clock (SMCLK)                             |     |

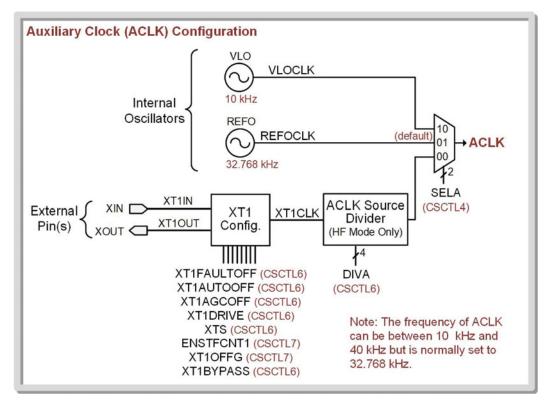

| 16.1.8 Auxiliary Clock (ACLK)                                     | 444 |

| 16.1.9 Default Settings on Power-Up                               |     |

| 16.1.10 CS Configuration Registers                                |     |

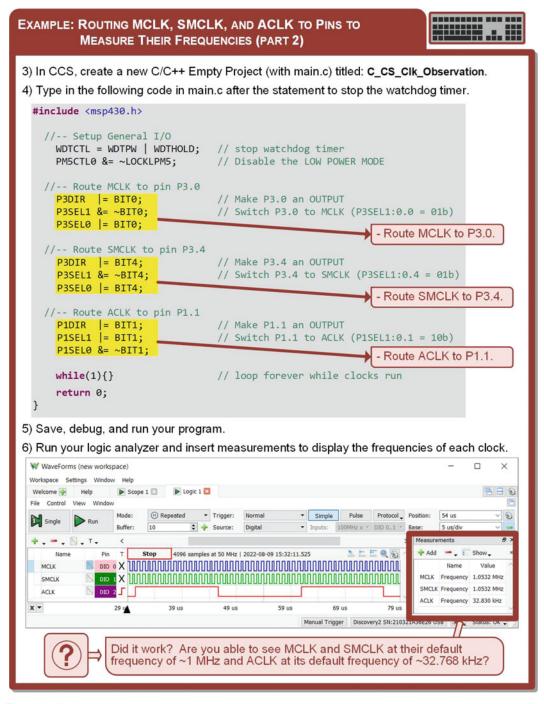

| 16.2 CONFIGURING THE CS ON THE MSP430FR2355                       | 456 |

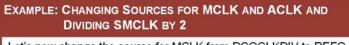

| 17: LOW POWER MODES                                               | 463 |

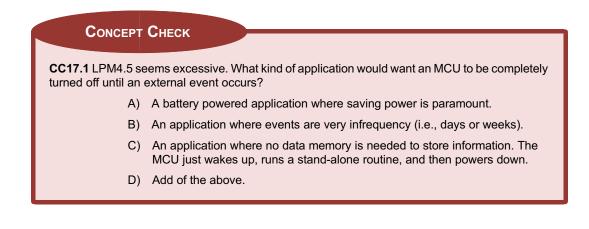

| 17.1 Overview of the MSP430FR2355's Low Power Modes               | 463 |

| 17.1.1 Active Mode (AM)                                           |     |

| 17.1.2 Low Power Mode 0 (LPM0): CPU OFF                           |     |

| 17.1.3 Low Power Mode 3 (LPM3): Standby                           |     |

| 17.1.4 Low Power Mode 4 (LPM4): Off                            | 464 |

|----------------------------------------------------------------|-----|

| 17.1.5 Low Power Mode 3.5 (LPM3.5): RTC Only                   | 465 |

| 17.1.6 Low Power Mode 4.5 (LPM4.5): Shutdown                   | 465 |

| 17.1.7 Example of Putting the MSP430FR2355 into Low Power Mode | 465 |

|                                                                |     |

| APPENDIX A: CONCEPT CHECK SOLUTIONS                            | 469 |

| REFERENCES                                                     | 471 |

| INDEX                                                          | 473 |

|                                                                |     |

## Chapter 1: Introduction to Embedded Systems

This chapter introduces the general concept of an embedded system. The goal is to provide a highlevel understanding of what an embedded computer is, their role in modern society, and motivation to learn more about them.

Learning Outcomes—After completing this chapter, you will be able to:

1.1 Describe the basic concept of an embedded system.

#### 1.1 What Is an Embedded System?

When most people hear the term "computer" they immediately think of their laptops or PCs. More recently, people have come to also associate portable devices such as smart phones and tablets with the term computer; however, most people don't tend to think of all of the modern electronics surrounding them as computers. But in fact, the majority of the consumer electronics in our daily lives have a computer that is controlling their operation. Items such as household appliances, thermostats, the mirror controller in a vehicle, an office copy machine, and even a hearing aid are examples of electronics in our daily lives that all have embedded computers at their core. The term to describe the small computers within these electronic devices is an *embedded computer*. The entire system then becomes an *embedded ded system*, implying that a small computer is included with the system and controls its operation [4–6].

So, what is the difference between the computers that we think of in laptops and workstations and those embedded in the majority of consumer electronics? We will classify computers into two broad categories: general-purpose and embedded. Let's start with a general-purpose computer. This type of computer is designed to run any type of software that the user desires. A user is able to install, uninstall, and update software applications that meet the user's current need. To support the abundance of potential software applications that may be run, general-purpose computers have abundant resources at their disposal. It is common for a general-purpose computer to have a variety of peripherals such as displays, keyboards/keypads, mice, Internet connections, and wireless communication capability. General-purpose computers also typically contain relatively high-performance hardware components such as fast processors and large amounts of data and program storage. To manage the large amounts of resources in a general-purpose computer, these devices require an operating system (OS). An operating system controls all of the resources and allocates them to the various software applications that are running. Common operating systems that you may be familiar with are Windows, iOS, and Linux. All of these operating systems have the same purpose, to manage the hardware resources of the computer so that any arbitrary software program may be successfully run on it. General-purpose computers also are designed for heavy user interaction. A typical general-purpose computer is designed to support a user sitting in front of it interacting with the software program using the keyboard, mouse, and monitor.

Despite a general-purpose computer having abundant resources, the vast majority of the time these resources are not being used. Activities such as typing an email or browsing the web use a very little amount of the computer's resources. But even though any single software program may only use a small amount of the resources available, a general-purpose computer must contain everything that is potentially needed to support a future program that may require the resources. To provide all of this capability, general-purpose computers are relatively expensive compared to their embedded systems'

counterparts with laptops and workstations costing hundreds to thousands of dollars. Additionally, to support the large number of resources, general-purpose computers are typically implemented using a group of integrated circuits (ICs), or chips. A general-purpose computer typically has one chip that implements its central processing unit (CPU), other chips to implement the data memory (i.e., RAM), and others to implement the program storage (i.e., hard drive or solid-state drive). A general-purpose computer is considered a *distributed* architecture because the full functionality of the computer is spread across multiple IC chips. This type of architecture supports very sophisticated CPUs and large amounts of data and program memory.

Now let's consider the concept of an embedded computer. Many of the electronics that are used in our daily lives don't require a high-performance computer that runs Windows or iOS. Your coffee maker doesn't require a cutting-edge processor to make your coffee. Your thermostat doesn't need the ability to run Microsoft Word to control the temperature of the room. What these types of applications need is a computer that can respond to inputs from the outside world (i.e., button presses or sensor inputs) and the ability to send control signals to other sub-systems to accomplish a task (i.e., heat the water reservoir or turn on the furnace). In these types of applications, the computer needs *just enough* resources to get the job done. The small computers used for these dedicated applications are *embedded computers*. Embedded computers are also referred to as *microcontrollers*, or MCUs, because they are the primary controller for their dedicated application.

Embedded computers have a variety of traits that differentiate them from general-purpose computers. First, embedded computers are mostly implemented on a single IC. An embedded computer does not require the large amounts of RAM and program storage as in a general-purpose computer, so all of the components of the computer can be put onto a single IC. Embedded computers also are able to include a variety of common peripherals such as timers, analog-to-digital converters, digital-to-analog converters, and serial interfaces to make them as versatile as possible when it comes to controlling all types of electronic devices. Depending on the amount of resources included, the physical size of an embedded computer chip can be extremely small. Consider the size of a thumb drive. This small storage stick has a full embedded computer system on it. Now compare that to the physical size of the hardware that resides in a general-purpose laptop. The small size of an embedded computer chip gives it the ability to be used in an endless list of applications.

Another attribute of an embedded computer is that it isn't designed to run arbitrary software programs that are installed at the will of the user. An embedded computer in a toaster isn't designed to have a new program installed by the user to make it control a microwave. The software that an embedded system runs is called firmware to highlight that it is not intended to be changed frequently. While some embedded systems can have their software updated by downloading a new program, this is a highly infrequent occurrence in the life of the computer (how many times have you upgraded the firmware in your car's mirrors?). Since an embedded computer does not need to support generalpurpose software programs, its software can be designed to optimize the functionality for the application at hand. This means there is a tight coupling between the hardware and software components of the embedded computer. This provides an optimized design that is typically only suited for the application that the embedded computer is made for. Embedded systems can contain operating systems; however, these OSs aren't anything like Windows or iOS. Instead, these operating systems act as task schedulers coordinating real-time activities such as reading from buttons or sensors and performing response actions. Operating systems for embedded computers are called real-time operating systems (RTOS), reflecting their purpose as a task scheduler. Not all embedded computers run an RTOS, but many just simply run dedicated software to accomplish a specific task.

Another attribute of an MCU is their low cost. While a general-purpose microprocessor chip can cost tens to hundreds of dollars, an MCU can cost 10s of cents to a few dollars. This low cost is driven by the high-volume manufacturing process used to create MCUs. As semiconductor manufacturing volume goes up, the cost of the individual chips produced goes down. The low cost of an embedded computer chip reveals the prevalence and popularity of the embedded computer. The number of embedded computers sold globally is multiple orders of magnitude larger than general-purpose computers, and this gap is only expected to grow as our devices become smarter and interconnected and more functionality is embedded into automobiles. In 2018, over 25 billion MCUs were sold globally [1]. Compare this to the ~400 million personal computers (PCs) sold annually that are based on general-purpose CPUs [2]. In fact, it is estimated that only ~2% of computer chips produced end up in PCs. To put this in perspective, every year there are tens of billions of new embedded systems being created to improve the quality of our lives [7,8].

Smart phones and tablets are a technology that has moved from the embedded systems category into the general-purpose description over the past decade. When cellular phones and personal desktop assistances first emerged, they were very much embedded systems. These devices were not able to support arbitrary software being installed on them and were designed to perform very specific tasks (phone calls, text messaging, scheduling, etc.); however, as processing technology advanced, cellular phones began to have the power to support more general-purpose operating systems such as Android and iOS. This gave them the ability to support different applications (i.e., *apps*) that could access the phone or tablets' abundant resources. Today, smart phones and tablets are considered general-purpose computers and only different from laptops and workstations in their size, portability, and software support.

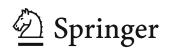

From an educational perspective, general-purpose computers and embedded computers are effectively the same. They are both computers that consist of hardware resources that are programmed to accomplish tasks using software. We can learn about the architecture of a computer using either, but focusing on embedded computers has a few advantages. First, they are inexpensive enough that every reader of this book can have an embedded computer sitting next to them where they can gain experience programming the MCU to do a variety of tasks. This allows embedded systems education to move from simply reading facts and figures to an active learning process where a deeper understanding of computers can be obtained. An additional bonus of this approach is that after completing the exercises in this book, the reader will have a practical skill set that is highly sought after in industry. Figure 1.1 shows a graphical depiction of the applications of computers and categorizing them into either generalpurpose or embedded.

#### CONCEPT CHECK

- **CC1.1** Why don't we just make one computer chip that serves the needs of every application on Earth? It seems like that would be a lot simpler than having thousands of different computer products.

- A) That isn't practical because every application has a different set of requirements. If we tried to create a "super chip" that could be simultaneously used in high-end servers and microwave ovens, then our microwave ovens would cost tens of thousands of dollars and consume much more electrical power.

- B) It is illegal to just have one computer chip design. It goes against the idea of capitalism and competition in the marketplace.

- C) They are still trying to create one computer chip that meets every application. It is just really hard.

- D) The answer to this concept check is A.

Fig. 1.1 Applications of embedded system [9]

#### Summary

- Computers can be put into two broad categories: general-purpose and embedded.

- General-purpose computers are designed to run any arbitrary software program. Thus, they contain abundant hardware resources to support potential applications and a sophisticated operating system to manage the resources.

- Embedded systems have a small computer embedded within them that controls the operation of the device.

#### **Exercise Problems**

### Section 1.1: What Is an Embedded System?

- **1.1.1** Classify a computer with the following attributes into either "general-purpose" or "embedded": *runs a sophisticated operating system such as Windows.*

- **1.1.2** Classify a computer with the following attributes into either "general-purpose" or "embedded": *implemented on a single chip*.

- 1.1.3 Classify a computer with the following attributes into either "general-purpose" or "embedded": can cost less than a US dollar.

- **1.1.4** Classify a computer with the following attributes into either "general-purpose" or "embedded": *designed to run any arbitrary software application the user desires.*

- **1.1.5** Classify a computer with the following attributes into either "general-purpose" or "embedded": *can cost hundreds to thousands of US dollars.*

- **1.1.6** Classify a computer with the following attributes into either "general-purpose" or "embedded": *its software is called firmware to highlight that it is rarely changed after being deployed.*

- 1.1.7 Classify a computer with the following attributes into either "general-purpose" or "embedded": also called a microcontroller because it controls the sub-systems around it.

- **1.1.8** Classify a computer with the following attributes into either "general-purpose" or "embedded": *can have a real-time operating system, but the OS primarily acts as a task scheduler.*

- **1.1.9** Classify a computer with the following attributes into either "general-purpose" or "embedded": has a tight coupling between the hardware and software, which optimizes its operation for the application at hand.

- Embedded computers have enough resources to "get the job done." They are implemented on a single IC, are very low in cost, and have a tight coupling between their hardware and software that optimizes their operation for the application they are designed for.

- The number of embedded computer chips sold each year outnumbers general-purpose computer chips by multiple orders of magnitude.

- **1.1.10** Classify a computer with the following attributes into either "general-purpose" or "embedded": *is the most popular type of computer on Earth.*

- **1.1.11** For the following application, would a generalpurpose computer or an embedded computer be better suited: *running the Windows operating system.*

- **1.1.12** For the following application, would a generalpurpose computer or an embedded computer be better suited: *controlling an Xbox*.

- **1.1.13** For the following application, would a generalpurpose computer or an embedded computer be better suited: *running a washing machine*.

- **1.1.14** For the following application, would a generalpurpose computer or an embedded computer be better suited: *controlling the radio in a car.*

- **1.1.15** For the following application, would a generalpurpose computer or an embedded computer be better suited: *controlling a satellite*.

- **1.1.16** For the following application, would a generalpurpose computer or an embedded computer be better suited: *controlling a wireless router*.

- **1.1.17** For the following application, would a generalpurpose computer or an embedded computer be better suited: *running servers in a data farm based on the Windows platform.*

- **1.1.18** For the following application, would a generalpurpose computer or an embedded computer be better suited: *a laptop running iOS*.

- **1.1.19** For the following application, would a generalpurpose computer or an embedded computer be better suited: *a Linux workstation used to develop for an MCU*.

- **1.1.20** For the following application, would a generalpurpose computer or an embedded computer be better suited: *controlling a video doorbell*.

## **Chapter 2: Digital Logic Basics**

This chapter provides a brief summary of classical digital logic design [10]. The point of this chapter is to expose the reader to the main concepts of digital logic so that they are familiar with them when moving into the computer organization topics covered later in the book. It is not intended to be an in-depth coverage of digital logic design. Rather, it is intended to expose the reader to the terminology used in digital logic, the most common number systems used in embedded systems, the basic logic operations used in combinational logic, and the basic operation of sequential logic, including synchronous registers and finite state machines.

Learning Outcomes—After completing this chapter you will be able to:

- 2.1 Describe the formation and use of positional number systems including conversions between bases and basic arithmetic.

- 2.2 Describe the basic operation of combinational logic circuits.

- 2.3 Describe the basic operation of sequential logic circuits.

- 2.4 Describe the basic operation of semiconductor memory including different implementation technologies.

#### 2.1 Number Systems

Logic circuits are used to generate and transmit 1s and 0s to compute and convey information. This two-valued number system is called binary. As presented earlier, there are many advantages of using a binary system; however, the human brain has been taught to count, label, and measure using the decimal number system. The decimal number system contains ten unique symbols (0  $\rightarrow$  9). In order to bridge the gap between the way our brains think (decimal) and how we build our computers (binary), we need to understand the basics of number systems. This includes the formal definition of a positional number system and how it can be extended to accommodate any arbitrarily large (or small) value. This also includes how to convert between different number systems that contain different numbers of symbols. In this section, we cover three different number systems: decimal (ten symbols), binary (two symbols), and hexadecimal (16 symbols). The study of decimal and binary is obvious as they represent how our brains interpret the physical world (decimal) and how our computers work (binary). Hexadecimal is studied because it is a useful means to represent large sets of binary values using a manageable number of symbols. This section will also discuss how to perform basic arithmetic (addition and subtraction) in the binary number system and how to represent negative numbers. The goal of this section is to provide an understanding of the basic principles of number systems so that we can design computer programs that use arbitrary number bases.

#### 2.1.1 Positional Number Systems

A positional number system allows the expansion of the original set of symbols so that they can be used to represent any arbitrarily large (or small) value. For example, if we use the ten symbols in our decimal system, we can count from 0 to 9. Using just the individual symbols we do not have enough symbols to count beyond 9. To overcome this, we use the same set of symbols but assign a different value to the symbol based on its position within the number. The *position* of the symbol with respect to other symbols in the number allows an individual symbol to represent greater (or lesser) values. We can use this approach to represent numbers larger than the original set of symbols. For example, let's say we

want to count from 0 upward by 1. We begin counting 0, 1, 2, 3, 4, 5, 6, 7, 8 to 9. When we are out of symbols and wish to go higher, we bring on a symbol in a different position with that position being valued higher and then start counting over with our original symbols (e.g., ..., 9, 10, 11, ... 19, 20, 21, ...). This is repeated each time a position runs out of symbols (e.g., ..., 99, 100, 101... 999, 1000, 1001,...).

First, let's look at the formation of a number system. The first thing that is needed is a set of symbols. The formal term for one of the symbols in a number system is a *numeral*. One or more numerals are used to form a *number*. We define the number of numerals in the system using the terms *radix* or *base*. For example, our decimal number system is said to be *base 10*, or have a *radix of 10*, because it consists of ten unique numerals or symbols.

#### Radix = Base≡the number of numerals in thenumber system

The next thing that is needed is the relative value of each numeral with respect to the other numerals in the set. We can say 0 < 1 < 2 < 3, etc., to define the relative magnitudes of the numerals in this set. The numerals are defined to be greater or less than their neighbors by a magnitude of 1. For example, in the decimal number system each of the subsequent numerals is greater than its predecessor by exactly 1. When we define this relative magnitude, we are defining that the numeral 1 is greater than the numeral 0 by a magnitude of 1; the numeral 2 is greater than the numeral 1 by a magnitude of 1; etc. At this point we have the ability to count from 0 to 9 by 1s. We also have the basic structure for mathematical operations that have results that fall within the numeral set from 0 to 9 (e.g., 1 + 2 = 3). In order to expand the values that these numerals can represent, we need define the rules of a positional number system.

#### 2.1.1.1 Generic Structure

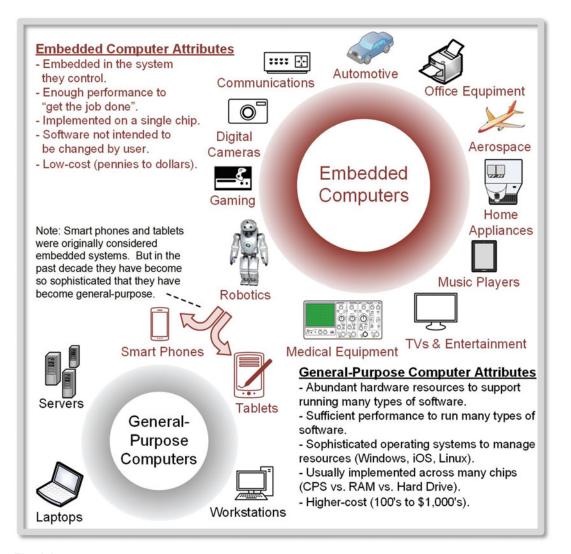

In order to represent larger or smaller numbers than the lone numerals in a number system can represent, we adopt a positional system. In a positional number system, the relative position of the numeral within the overall number dictates its value. When we begin talking about the position of a numeral, we need to define a location to which all of the numerals are positioned with respect to. We define the *radix point* as the point within a number to which numerals to the left represent whole numbers and numerals to the right represent fractional numbers. The radix point is denoted with a period (i.e., "."). A particular number system often renames this radix point to reflect its base. For example, in the base 10 number system (i.e., decimal), the radix point is commonly called the *decimal point*; however, the term *radix point* can be used across all number systems as a generic term. If the radix point is not present in a number, it is assumed to be to the right of number. Figure 2.1 shows an example number highlighting the radix point and the relative positions of the whole and fractional numerals.

Fig. 2.1 Definition of radix point

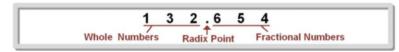

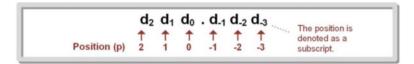

Next, we need to define the position of each numeral with respect to the radix point. The position of the numeral is assigned a whole number with the number to the left of the radix point having a position value of 0. The position number increases by 1 as numerals are added to the left (2, 3, 4...) and decreased by 1 as numerals are added to the right (-1, -2, -3). We will use the variable *p* to represent position. The position number will be used to calculate the value of each numeral in the number based on its relative position to the radix point. Figure 2.2 shows the example number with the position value of each numeral highlighted.

### Fig. 2.2 Definition of position number (p) within the number

In order to create a generalized format of a number, we assign the term *digit* (d) to each of the numerals in the number. The term digit signifies that the numeral has a position. The position of the digit within the number is denoted as a subscript. The term *digit* can be used as a generic term to describe a numeral across all systems, although some number systems will use a unique term instead of digit which indicates its base. For example, the binary system uses the term *bit* instead of digit; however, using the term digit to describe a generic numeral in any system is still acceptable. Figure 2.3 shows the generic subscript notation used to describe the position of each digit in the number.

#### Fig. 2.3 Digit notation

We write a number from left to right starting with the highest position digit that is greater than 0 and end with the lowest position digit that is greater than 0. This reduces the number of numerals that are written; however, a number can be represented with an arbitrary number of 0s to the left of the highest position digit greater than 0 and an arbitrary number of 0s to the right of the lowest position digit greater than 0 and an arbitrary number. For example, the number 132.654 could be written as 0132.6540 without affecting the value of the number. The 0s to the left of the number are called *leading 0s* and the 0s to the right of the number are called *trailing 0s*. The reason this is being stated is because when a number is implemented in circuitry, the number of numerals is fixed, and each numeral must have a value. The variable *n* is used to represent the number of numerals in a number. If a number is defined with n=4, that means four numerals are always used. The number 0 would be represented as 0000 with both representations having an equal value.

#### 10 • Chapter 2: Digital Logic Basics

#### 2.1.1.2 Decimal Number System (Base 10)

As mentioned earlier, the decimal number system contains ten unique numerals (0, 1, 2, 3, 4, 5, 6, 7, 8, and 9). This system is thus a base 10 or a radix 10 system. The relative magnitudes of the symbols are 0 < 1 < 2 < 3 < 4 < 5 < 6 < 7 < 8 < 9.

#### 2.1.1.3 Binary Number System (Base 2)

The binary number system contains two unique numerals (0 and 1). This system is thus a base 2 or a radix 2 system. The relative magnitudes of the symbols are 0 < 1. At first glance, this system looks very limited in its ability to represent large numbers due to the small number of numerals. When counting up, as soon as you count from 0 to 1, you are out of symbols and must increment the p + 1 position in order to represent the next number (e.g., 0, 1, 10, 11, 100, 101, ...); however, magnitudes of each position scale quickly so that circuits with a reasonable amount of digits can represent very large numbers. The term *bit* is used instead of *digit* in this system to describe the individual numerals and at the same time indicate the base of the number.

Due to the need for multiple bits to represent meaningful information, there are terms dedicated to describing the number of bits in a group. When 4 bits are grouped together, they are called a *nibble*. When 8 bits are grouped together, they are called a *byte*. Larger groupings of bits are called *words*. The size of the word can be stated as either an *n-bit word* or omitted if the size of the word is inherently implied. For example, if you were using a 32-bit microprocessor, using the term *word* would be interpreted as a *32-bit word*. For example, if there was a 32-bit grouping, it would be referred to as a 32-bit word. The leftmost bit in a binary number is called the *Most Significant Bit* (MSB). The rightmost bit in a binary number is called the *Least Significant Bit* (*LSB*).

#### 2.1.1.4 Hexadecimal Number System (Base 16)

The hexadecimal number system contains 16 unique numerals. This system is most often referred to in spoken word as "hex" for short. Since we only have ten Arabic numerals in our familiar decimal system, we need to use other symbols to represent the remaining six numerals. We use the alphabetic characters A–F in order to expand the system to 16 numerals. The 16 numerals in the hexadecimal system are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. The relative magnitudes of the symbols are 0 < 1 < 2 < 3 < 4 < 5 < 6 < 7 < 8 < 9 < A < B < C < D < E < F. We use the generic term digit to describe the numerals within a hexadecimal number.

At this point, it becomes necessary to indicate the base of a written number. The number 10 has an entirely different value if it is a decimal number or binary number. In order to handle this, a subscript is typically included at the end of the number to denote its base when writing out the number. For example,  $10_{10}$  indicates that this number is decimal "ten." If the number was written as  $10_2$ , this number would represent binary "one zero." Table 2.1 lists the equivalent values in each of the four number systems just described for counts from  $0_{10}$  to  $15_{10}$ . The left side of the table does not include leading 0s. The right side of the table contains the same information but includes the leading 0s. The equivalencies of decimal, binary, and hexadecimal in this table are typically committed to memory.

| Decimal              | Binary                       | Hex              | Decimal              | Binary                       | Hex     |

|----------------------|------------------------------|------------------|----------------------|------------------------------|---------|

| 0                    | 0                            | 0                | 00                   | 0000                         | 0       |

| 1                    | 1                            | 1                | 01                   | 0001                         | 1       |

| 2                    | 10                           | 2                | 02                   | 0010                         | 2       |

| 3                    | 11                           | 3                | 03                   | 0011                         | 3       |

| 4                    | 100                          | 4                | 04                   | 0100                         | 4       |

| 5                    | 101                          | 5                | 05                   | 0101                         | 5       |

| 6                    | 110                          | 6                | 06                   | 0110                         | 6       |

| 7                    | 111                          | 7                | 07                   | 0111                         | 7       |

| 8                    | 1000                         | 8                | 08                   | 1000                         | 8       |

| 9                    | 1001                         | 9                | 09                   | 1001                         | 9       |

| 10                   | 1010                         | A                | 10                   | 1010                         | A       |

| 11                   | 1011                         | B                | 11                   | 1011                         | B       |

| 12<br>13<br>14<br>15 | 1100<br>1101<br>1110<br>1111 | C<br>D<br>E<br>F | 12<br>13<br>14<br>15 | 1100<br>1101<br>1110<br>1111 | C D E F |

| (Witho               | out Leadin                   | g 0's)           | (Wit                 | h Leading                    | 0's)    |

#### Table 2.1

Number system equivalency (decimal, binary, hexadecimal)

When typing out different number bases within the MSP430 low-level programming environment, special syntax is used to specify the desired base. Figure 2.4 shows the allowable syntax for specifying constant *literals* for the MSP430. The term "literal" simply means that the number is to be treated as a number, not as something else such as a location in memory.

| Decimal Literals<br>- No special syntax.<br>- Negative signs <u>are</u> permitted.<br>- Commas <u>are not</u> permitted. | <u>Valid Decimal Syntax</u><br>1000<br>-32768<br>25                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary Literals<br>- Append "b" to the end of binary number.                                                             | Valid Binary Syntax<br>11001100b<br>101010B                                                                                                                                                            |

| Hexadecimal Literals<br>- Append "h" to the end of HEX number.<br>Note 1: If the HEX number starts with a                | <u>Valid Hexadecimal Syntax</u><br>123h<br>6ABBH<br>0ABCDh                                                                                                                                             |

| letter (i.e,. A, B, C, D, E, or F) a leading 0<br>must in inserted because a literal cannot<br>start with a letter.      | Note 2: For the last example, the intended<br>number was ABCDh. However this syntax alone<br>would be invalid because a literal constant<br>cannot start with a letter so a leading 0 was<br>inserted. |

|                                                                                                                          | is not the same size as the register that it will go<br>ith leading 0's to make it the appropriate size.                                                                                               |

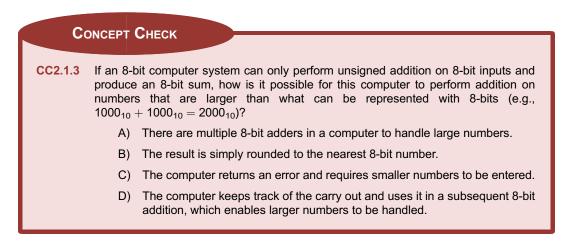

#### **CONCEPT CHECK**

**CC2.1.1** The base of a number system is arbitrary and is commonly selected to match a particular aspect of the physical system in which it is used (e.g., base 10 corresponds to our 10 fingers, base 2 corresponds to the 2 states of a switch). If a physical system contained 3 unique modes and a base of 3 was chosen for the number system, what is the base 3 equivalent of the decimal number 3?

A)  $3_{10} = 11_3$

- B) 3<sub>10</sub> = 3<sub>3</sub>

- C)  $3_{10} = 10_3$

- D)  $3_{10} = 21_3$

#### 2.1.2 Base Conversion

Now we look at converting between bases. There are distinct techniques for converting to and from decimal. There are also techniques for converting between bases that are powers of 2 (e.g., base 2, 4, 8, and 16).

#### 2.1.2.1 Converting to Decimal

The value of each digit within a number is based on the individual digit value and the digit's position. Each position in the number contains a different *weight* based on its relative location to the radix point. The weight of each position is based on the radix of the number system that is being used. The weight of each position in decimal is defined as:

#### $Weight = (Radix)^p$

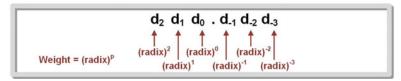

This expression gives the number system the ability to represent fractional numbers since an expression with a negative exponent (e.g.,  $x^{-y}$ ) is evaluated as 1 over the expression with the exponent change to positive (e.g.,  $1/x^{y}$ ). Figure 2.5 shows the generic structure of a number with its positional weight highlighted.

#### Fig. 2.5 Weight definition

In order to find the decimal value of each of the numerals in the number, its individual numeral value is multiplied by its positional weight. In order to find the value of the entire number, each value of the individual numeral-weight products is summed. The generalized format of this conversion is written as:

Total Decimal Value =

$$\sum_{i=p_{min}}^{p_{max}} d_i \cdot (radix)^i$$

In this expression,  $p_{max}$  represents the highest position number that contains a numeral greater than 0. The variable  $p_{min}$  represents the lowest position number that contains a numeral greater than 0. These limits are used to simplify the hand calculations; however, these terms theoretically could be  $+\infty$  to  $-\infty$  with no effect on the result since the summation of every leading 0 and every trailing 0 contributes nothing to the result.

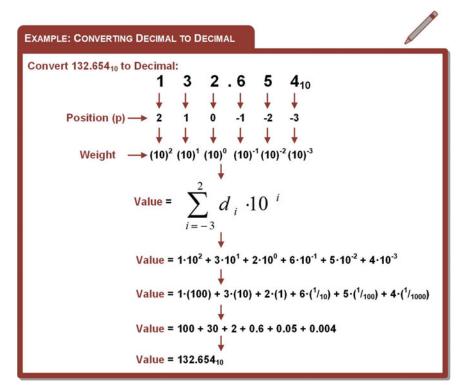

As an example, let's evaluate this expression for a decimal number. The result will yield the original number but will illustrate how positional weight is used. Let's take the number  $132.654_{10}$ . To find the decimal value of this number, each numeral is multiplied by its positional weight and then all of the products are summed. The positional weight for the digit 1 is  $(radix)^{p}$  or  $(10)^{2}$ . In decimal this is called the hundred's position. The positional weight for the digit 3 is  $(10)^{1}$ , referred to as the ten's position. The positional weight for digit 2 is  $(10)^{0}$ , referred to as the 1s position. The positional weight for digit 6 is  $(10)^{-1}$ , referred to as the tenth's position. The positional weight for digit 4 is  $(10)^{-3}$ , referred to as the thousandth's position. When these weights are multiplied by their respective digits and summed, the result is the original decimal number  $132.654_{10}$ . Example 2.1 shows this process step by step.

#### 14 • Chapter 2: Digital Logic Basics

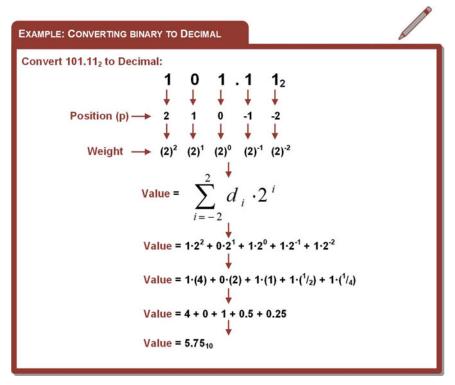

This process is used to convert between any other base to decimal. Let's convert  $101.11_2$  to decimal. The same process is followed with the exception that the base in the summation is changed to 2. Converting from binary to decimal can be accomplished quickly in your head due to the fact that the bit values in the products are either 1 or 0. That means any bit that is a 0 has no impact on the outcome and any bit that is a 1 simply yields the weight of its position. Example 2.2 shows the step-by-step process converting a binary number to decimal.

Example 2.2 Converting binary to decimal

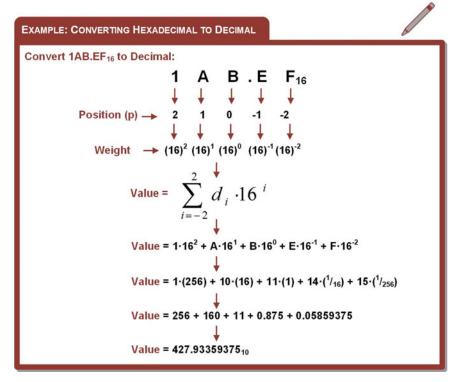

Let's now convert  $1AB.EF_{16}$  to decimal. The same process is followed with the exception that the base is changed to 16. When performing the conversion, the decimal equivalent of the numerals A–F needs to be used. Example 2.3 shows the step-by-step process converting a hexadecimal number to decimal.

#### **Example 2.3** Converting hexadecimal to decimal

In some cases, it is desired to specify a *level of accuracy* for the conversion in order to bound the number of fractional digits in the final result. For example, if the conversion in Example 2.3 was stated as "convert 1AB.EF<sub>16</sub> to decimal with a *fractional accuracy of 2 digits*," the final result would be 427.93<sub>10</sub>. How rounding is handled can also be specified with the two options being *with* or *without rounding*. In the case where the conversion is performed *with rounding*, additional fractional digits may need to be computed to determine if the least significant digit of the new decimal fraction needs to be altered. For example, let's say the conversion in Example 2.3 is stated as "convert 1AB.EF<sub>16</sub> to decimal with a fractional accuracy of 4 *digits with rounding*." In this case, the final result would be 427.9336<sub>10</sub>. Notice how rounding was applied to the digit in position p = -3 changing it from a 5 to a 6 based on the value in position p = -4. Now let's say the conversion in Example 2.3 is stated as "convert 1AB.EF<sub>16</sub> to decimal with a fractional accuracy of 4 *digits without rounding*." In this case, the final result would be 427.9336<sub>10</sub>. Notice how rounding accuracy of 4 *digits without rounding*." In this case, the final result would be 427.9335<sub>10</sub>. Notice how without rounding simply drops all of the digits beyond the specified level of accuracy.

#### 2.1.2.2 Converting from Decimal

The process of converting from decimal to another base consists of two separate algorithms. There is one algorithm for converting the whole number portion of the number and another algorithm for converting the fractional portion of the number. The process for converting the whole number portion is to divide the decimal number by the base of the system you wish to convert to. The division will result in a quotient and a whole number remainder. The remainder is recorded as the *least significant numeral* in the converted number. The resulting quotient is then divided again by the base, which results in a new quotient and new remainder. The remainder is recorded as the next higher-order numeral in the new

number. This process is repeated until a quotient of 0 is achieved. At that point the conversion is complete. The remainders will always be within the numeral set of the base being converted to.

The process for converting the fractional portion is to multiply just the fractional component of the number by the base. This will result in a product that contains a whole number and a fraction. The whole number is recorded as the *most significant digit* of the new converted number. The new fractional portion is then multiplied again by the base with the whole number portion being recorded as the next lower-order numeral. This process is repeated until the product yields a fractional component equal to 0 or the desired level of accuracy has been achieved. The level of accuracy is specified by the number of numerals in the new converted number. For example, the conversion would be stated as "convert this decimal number to binary with a fractional accuracy of 4 bits." This means the final result would only have 4 bits in the fraction. In cases where the conversion does not yield exactly 4 fractional bits, there are two approaches that can be used. The first is to have *no rounding*, which means the conversion simply stops at the desired accuracy. The second is to apply *rounding*, which means additional bits beyond the desired accuracy are computed in order to determine whether the least significant bit is reported.

Let's convert  $11.375_{10}$  to binary. Example 2.4 shows the step-by-step process converting a decimal number to binary.

Example 2.4 Converting decimal to binary

In many binary conversions to binary, the number of fractional bits that result from the conversion is more than what is needed. In this case, rounding is applied to limit the fractional accuracy. The simplest rounding approach for binary numbers is to continue the conversion for one more bit beyond the desired fractional accuracy. If the next bit is a 0, then you leave the fractional component of the number as is. If the next bit is a 1, you round the least significant bit of your number up. Often this rounding will result in a cascade of roundings from the LSB to the MSB. As an example, let's say that the conversion in Example 2.4 was specified to have a fractional accuracy of 2 bits. If the bit in position p = -3 was a 0 (which it is not, but let's just say it is for the sake of this example), then the number would be left as is and the final converted number would be  $1011.01_2$ ; however, if the bit in position p = -3 was a 1 (as it actually is in Example 2.4), then we would need to apply rounding. We would start with the bit in position p = -2. Since it is a 1, we would round that up to a 0, but we would need to apply the overflow of this rounding to the next higher-order bit in position p = -1. That would then cause the value of p = -1 to go from a 0 to a 1. The final result of the conversion with rounding would be  $1011.01_2$ .

Let's now convert  $254.655_{10}$  to hexadecimal with an accuracy of three fractional digits. When doing this conversion, all of the divisions and multiplications are done using decimal. If the results end up between  $10_{10}$  and  $15_{10}$ , then the decimal numbers are substituted with their hex symbol equivalent (i.e., A to F). Example 2.5 shows the step-by-step process of converting a decimal number to hex with a fractional accuracy of three digits.

Example 2.5 Converting decimal to hexadecimal

Rounding of hexadecimal digits uses a similar approach as when rounding decimal numbers, with the exception that the middle of the range of the numbers lies between digits  $7_{16}$  and  $8_{16}$ . This means that any number to be rounded that is  $8_{16}$  or greater will be rounded up. Numbers that are  $7_{16}$  or less will be rounded down, which means the fractional component of the converted number is left as in.

#### 2.1.2.3 Converting Between 2<sup>n</sup> Bases

Converting between  $2^n$  bases (e.g., 2, 4, 8, and 16) takes advantage of the direct mapping that each of these bases has back to binary. Base 8 numbers take exactly 3 binary bits to represent all eight symbols (i.e.,  $0_8 = 000_2$ ,  $7_8 = 111_2$ ). Base 16 numbers take exactly 4 binary bits to represent all 16 symbols (i.e.,  $0_{16} = 0000_2$ ,  $F_{16} = 1111_2$ ).

When converting *from* binary to any other  $2^n$  base, the whole number bits are grouped into the appropriate-sized sets starting from the radix point and working left. If the final leftmost grouping does not have enough symbols, it is simply padded on left with leading 0s. Each of these groups is then directly substituted with their  $2^n$  base symbol. The fractional number bits are also grouped into the appropriate-sized sets starting from the radix point, but this time working right. Again, if the final rightmost grouping does not have enough symbols, it is simply padded on the right with trailing 0s. Each of these groups is then directly substituted with their  $2^n$  base symbol.

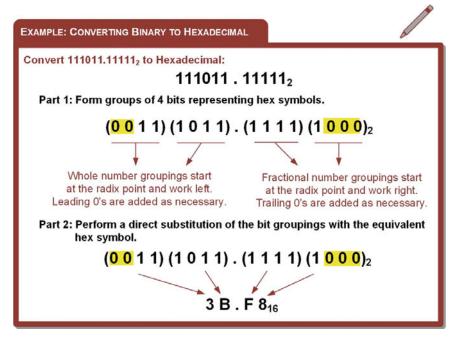

Example 2.6 shows the step-by-step process of converting a binary number to hexadecimal.

**Example 2.6** Converting binary to hexadecimal

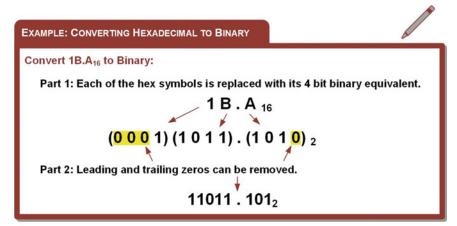

Example 2.7 shows the step-by-step process of converting a hexadecimal number to binary.

#### **Example 2.7** Converting hexadecimal to binary

#### 2.1.3 Binary Arithmetic

#### 2.1.3.1 Addition (Carries)

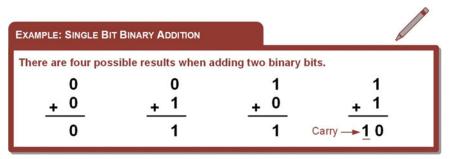

Binary addition is a straightforward process that mirrors the approach we have learned for longhand decimal addition. The two numbers (or terms) to be added are aligned at the radix point and addition begins at the least significant bit. If the sum of the least significant position yields a value with two bits (e.g., 10<sub>2</sub>), then the least significant bit is recorded, and the most significant bit is *carried* to the next higher position. The sum of the next higher position is then performed including the potential *carry bit* from the prior addition. This process continues from the least significant position to the most significant position. Example 2.8 shows how addition is performed on two individual bits.

Example 2.8 Single bit binary addition

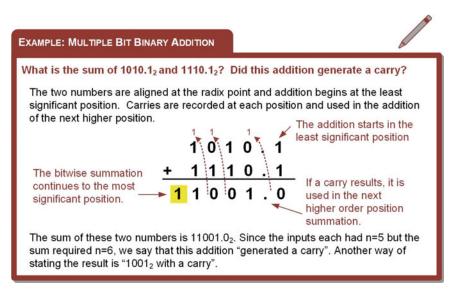

When performing binary addition, the width of the inputs and output is fixed (i.e., *n*-bits). Carries that exist within the *n*-bits are treated in the normal fashion of including them in the next higher position sum; however, if the highest position summation produces a carry, this is a uniquely named event. This event is called a *carry out* or the sum is said to *generate a carry*. The reason this type of event is given special terminology is because in real circuitry, the number of bits of the inputs and output is fixed in hardware and the carryout is typically handled by a separate circuit. Example 2.9 shows this process when adding two 4-bit numbers.

#### Example 2.9 Multiple bit binary addition

The largest decimal sum that can result from the addition of two binary numbers is given by  $2 \cdot (2^n - 1)$ . For example, two 8-bit numbers to be added could both represent their highest decimal value of  $(2^n - 1)$  or  $255_{10}$  (i.e., 1111 1111<sub>2</sub>). The sum of this number would result in  $510_{10}$  or (1 1111 1110<sub>2</sub>). Notice that the largest sum achievable would only require one additional bit. This means that a single carry bit is sufficient to handle all possible magnitudes for binary addition.

#### 2.1.3.2 Subtraction (Borrows)

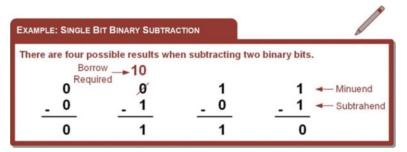

Binary subtraction also mirrors longhand decimal subtraction. In subtraction, the formal terms for the two numbers being operated on are *minuend* and *subtrahend*. The subtrahend is subtracted from the minuend to find the *difference*. In longhand subtraction, the minuend is the top number and the subtrahend is the bottom number. For a given position if the minuend is less than the subtrahend, it needs to *borrow* from the next higher-order position to produce a difference that is positive. If the next higher position does not have a value that can be borrowed from (i.e., 0), then it in turn needs to borrow from the next higher position and so forth. Example 2.10 shows how subtraction is performed on two individual bits.

#### Example 2.10 Single bit binary subtraction

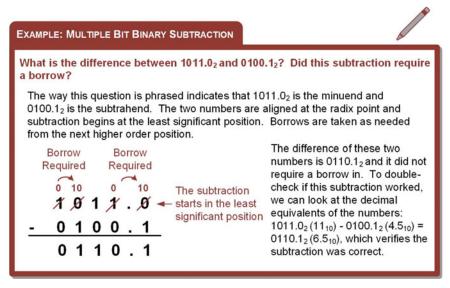

As with binary addition, binary subtraction is accomplished on fixed widths of inputs and output (i.e., *n*-bits). The minuend and subtrahend are aligned at the radix point and subtraction begins at the least significant bit position. Borrows are used as necessary as the subtractions move from the least significant position to the most significant position. If the most significant position requires a borrow, this is a uniquely named event. This event is called a *borrow in* or the subtraction is said to *require a borrow*. Again, the reason this event is uniquely named is because in real circuitry, the number of bits of the input and output is fixed in hardware and the borrow in is typically handled by a separate circuit. Example 2.11 shows this process when subtracting two 4-bit numbers.

**Example 2.11** Multiple bit binary subtraction

Notice that if the minuend is less than the subtrahend, then the difference will be negative. At this point, we need a way to handle negative numbers.

#### 2.1.4 Unsigned and Signed Numbers

All of the number systems presented in the prior sections were positive. We need to also have a mechanism to indicate negative numbers. When looking at negative numbers, we only focus on the mapping between decimal and binary since octal and hexadecimal are used as just another representation of a binary number. In decimal, we are able to use the negative *sign* in front of a number to indicate it is negative (e.g.,  $-34_{10}$ ). In binary, this notation works fine for writing numbers on paper (e.g.,  $-1010_2$ ), but we need a mechanism that can be implemented using real circuitry. In a real digital circuit, the circuits can only deal with 0s and 1s. There is no "–" in a digital circuit. Since we only have 0s and 1s in the hardware, we use a bit to represent whether a number is positive or negative. This is referred to as the *sign bit*. If a binary number is not going to have any negative values, then it is called an *unsigned* number and it can only represent positive numbers. If a binary number is going to allow negative numbers, it is called a *signed* number. It is important to always keep track of the type of number we are using as the same bit values can represent very different numbers depending on the coding mechanism that is being used.

#### 2.1.4.1 Unsigned Numbers

An unsigned number is one that does not allow negative numbers. When talking about this type of code, the number of bits is fixed and stated up front. We use the variable *n* to represent the number of bits in the number. For example, if we had an 8-bit number, we would say, "This is an 8-bit, unsigned number."

The number of unique codes in an unsigned number is given by  $2^n$ . For example, if we had an 8-bit number, we would have  $2^8$  or 256 unique codes (e.g., 0000 0000<sub>2</sub> to 1111 1111<sub>2</sub>).

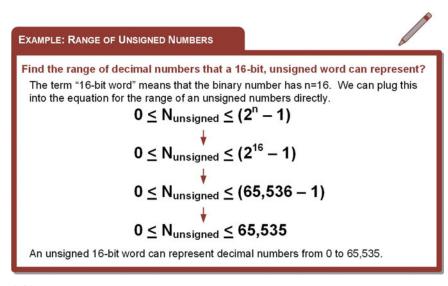

The *range* of an unsigned number refers to the decimal values that the binary code can represent. If we use the notation  $N_{\text{unsigned}}$  to represent any possible value that an *n*-bit, unsigned number can take on, the range would be defined as:  $0 < N_{\text{unsigned}} < (2^n - 1)$

Range of anUNSIGNED number  $\Rightarrow 0 < N_{unsigned} < (2^n - 1)$

For example, if we had an unsigned number with n = 4, it could take on a range of values from  $+0_{10}$  (0000<sub>2</sub>) to  $+15_{10}$  (1111<sub>2</sub>). Notice that while this number has 16 unique possible codes, the highest decimal value it can represent is  $15_{10}$ . This is because one of the unique codes represents  $0_{10}$ . This is the reason that the highest decimal value that can be represented is given by  $(2^n - 1)$ . Example 2.12 shows this process for a 16-bit number.

#### Example 2.12

Finding the range of an unsigned number

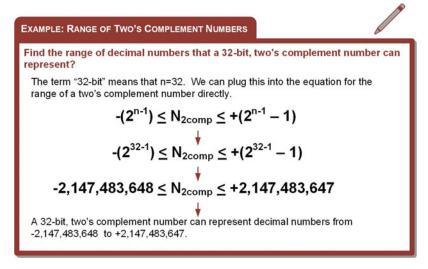

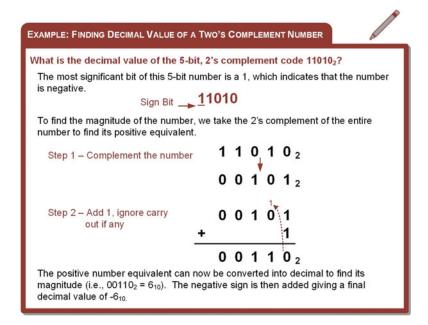

#### 2.1.4.2 Signed Numbers (Two's Complement)

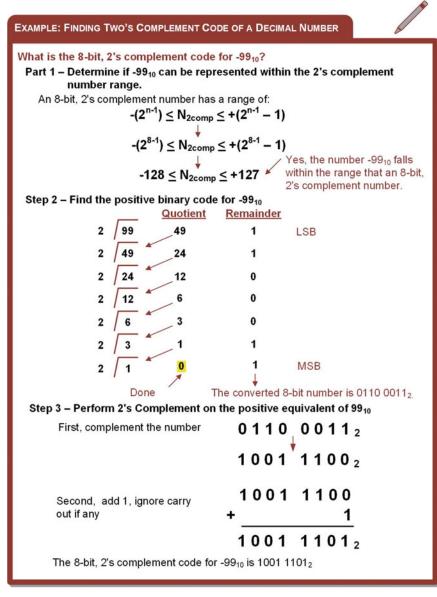

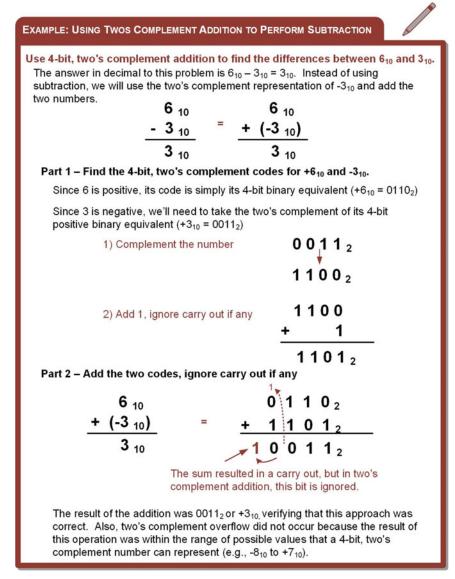

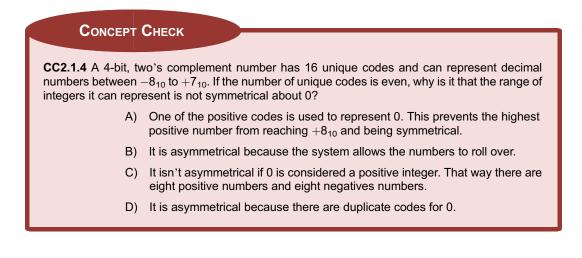

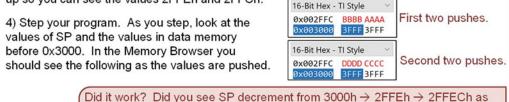

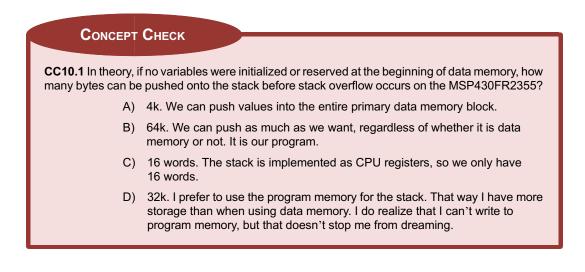

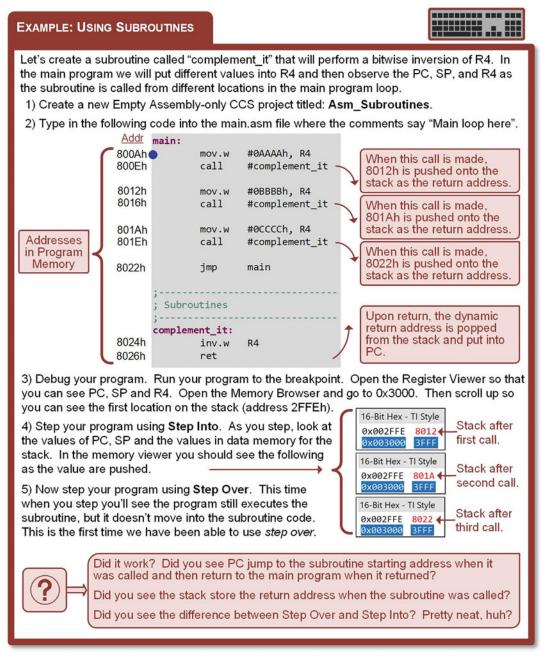

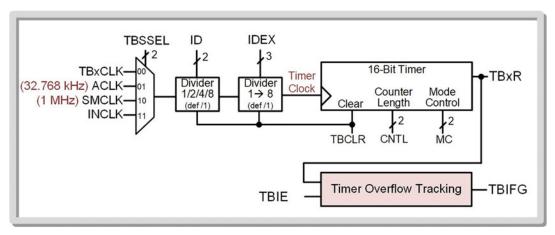

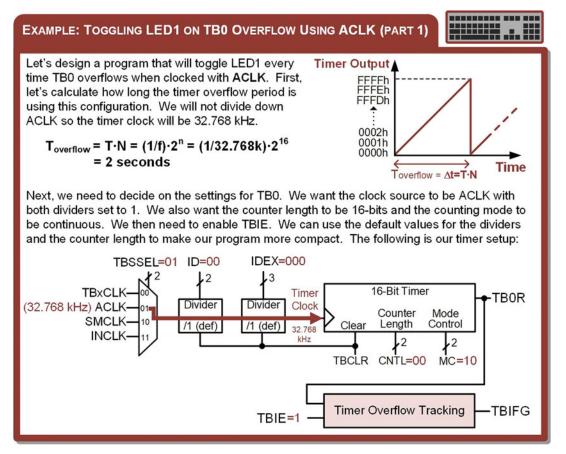

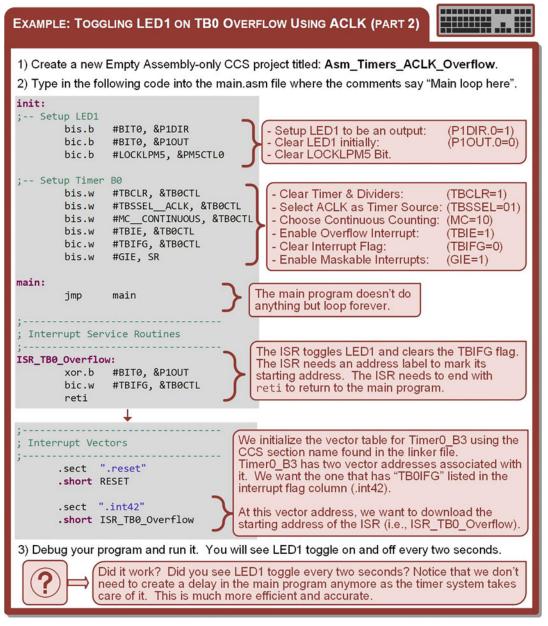

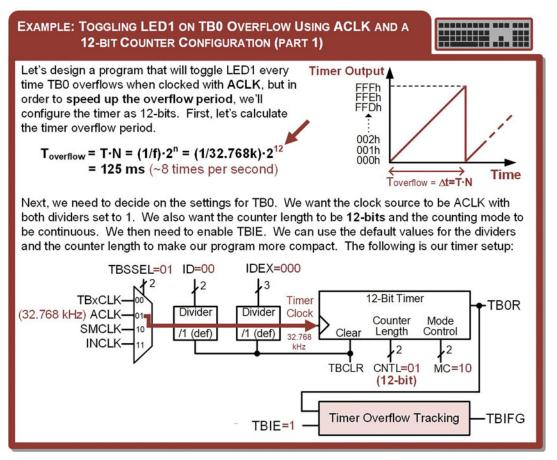

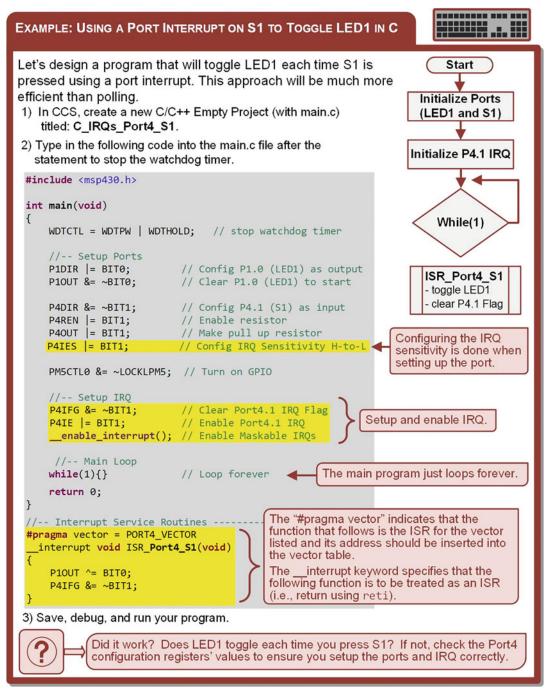

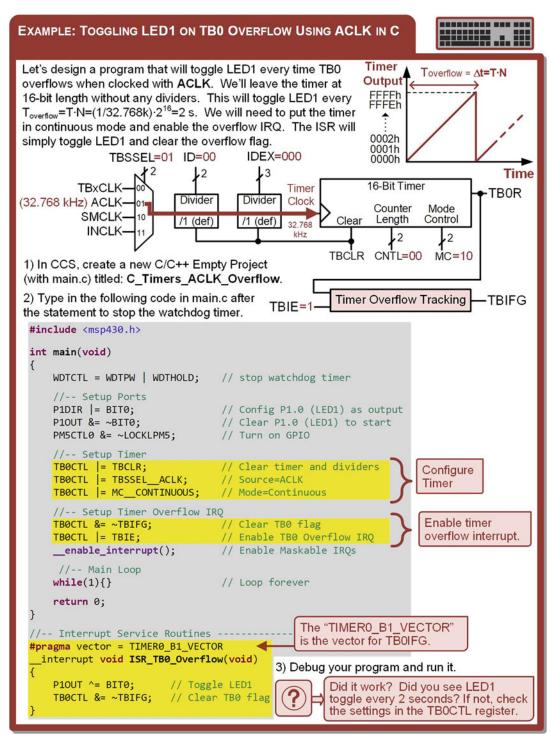

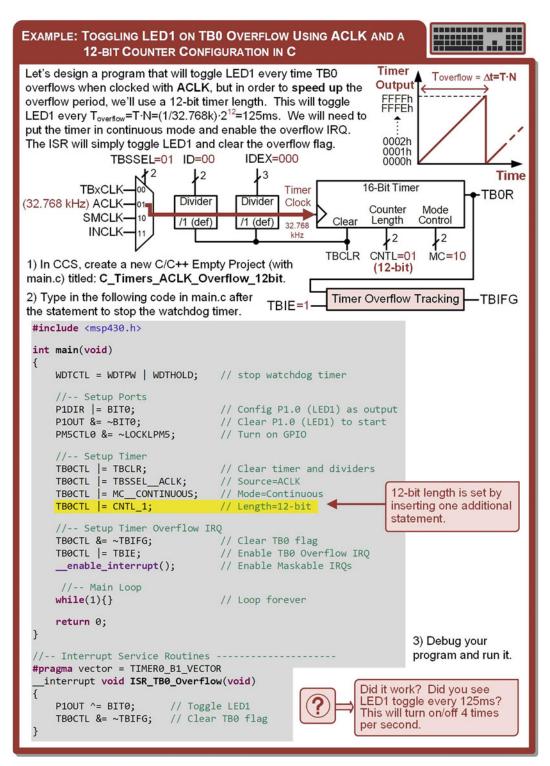

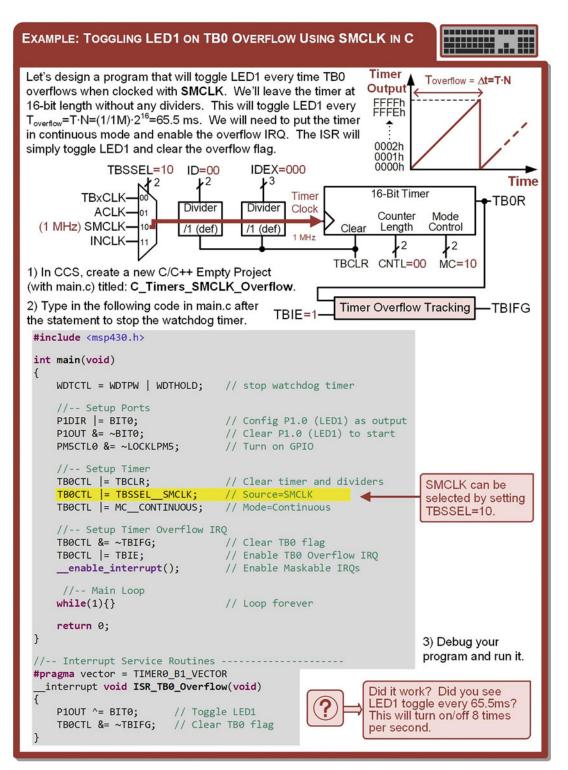

Signed numbers are able to represent both positive and negative numbers. The most significant bit of a signed numbers is always the *sign bit*, which represents whether the number is positive or negative. The sign bit is defined to be a *0 if the number is positive* and *1 if the number is negative*. When using signed numbers, the number of bits is fixed so that the sign bit is always in the same position. There are a variety of ways to encode negative numbers using a sign bit. The encoding method used exclusively in modern computers is called *two's complement*. When talking about a signed number, the number of bits and the type of encoding is always stated. For example, we would say, "This is an 8-bit, two's complement number."