# EMERGING LOW-POWER SEMICONDUCTOR DEVICES

Applications for Future Technology Nodes

EDITED BY SHUBHAM TAYAL ABHISHEK KUMAR UPADHYAY DEEPAK KUMAR SHIROMANI BALMUKUND RAHI

# Emerging Low-Power Semiconductor Devices

This book gives insight into the emerging semiconductor devices from their applications in electronic circuits. It discusses the challenges in the field of engineering and applications of advanced low-power devices.

*Emerging Low-Power Semiconductor Devices: Applications for Future Technology Nodes* offers essential exposure to low-power devices and their applications in wireless, biosensing, and circuit domains. The book provides a detailed discussion on all aspects, including the current and future scenarios related to the low-power device. The book also presents basic knowledge about field-effect transistor (FET) devices and introduces emerging and novel FET devices. The chapters include a review of the usage of FET devices in various domains like biosensing, wireless and cryogenics applications. The chapters also explore device-circuit co-design issues in the digital and analog domains. The content is presented in an easy-to-follow manner that makes it ideal for individuals new to the subject.

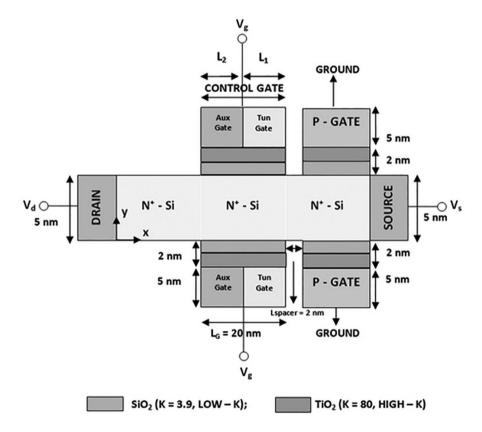

This book is intended for scientists, researchers, and postgraduate students looking for an understanding of device physics, circuits, and systems.

## Emerging Low-Power Semiconductor Devices Applications for Future

Technology Nodes

Edited by

Shubham Tayal, Abhishek Kumar Upadhyay, Deepak Kumar, and Shiromani Balmukund Rahi

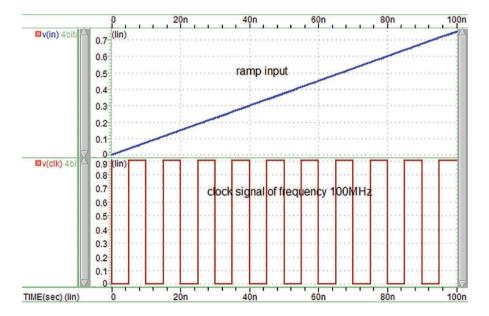

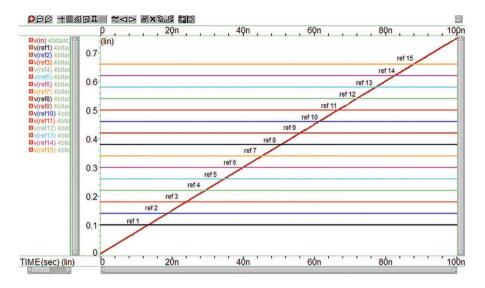

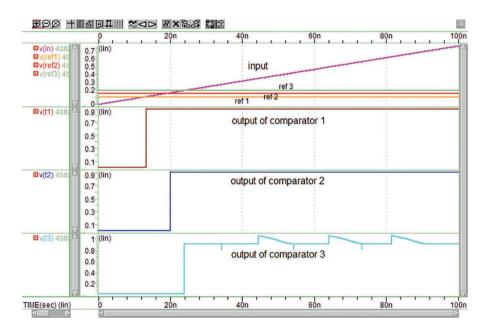

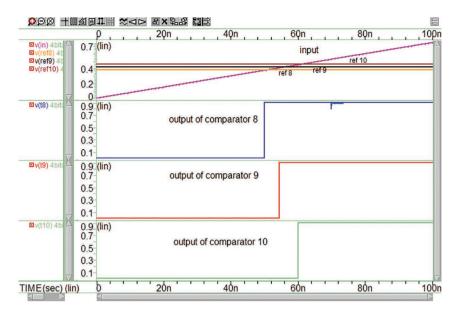

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

First edition published 2023 by CRC Press 6000 Broken Sound Parkway NW, Suite 300, Boca Raton, FL 33487-2742

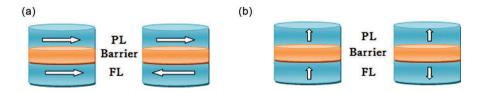

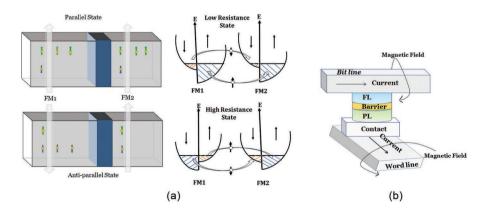

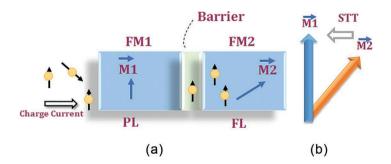

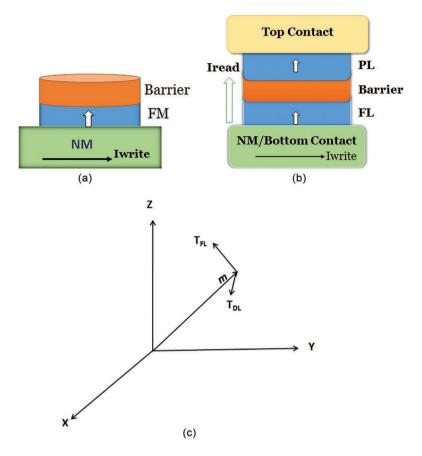

and by CRC Press 4 Park Square, Milton Park, Abingdon, Oxon, OX14 4RN

CRC Press is an imprint of Taylor & Francis Group, LLC

© 2023 selection and editorial matter, Shubham Tayal, Abhishek Kumar Upadhyay, Deepak Kumar, Shiromani Balmukund Rahi; individual chapters, the contributors

Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, access www.copyright. com or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. For works that are not available on CCC, please contact mpkbookspermissions@ tandf.co.uk

*Trademark notice*: Product or corporate names may be trademarks or registered trademarks and are used only for identification and explanation without intent to infringe.

ISBN: 978-1-032-14729-1 (hbk) ISBN: 978-1-032-14730-7 (pbk) ISBN: 978-1-003-24077-8 (ebk)

DOI: 10.1201/9781003240778

Typeset in Times by codeMantra

## Contents

|           | vii<br>six                                                                                     |

|-----------|------------------------------------------------------------------------------------------------|

| Chapter 1 | Role of TFET Devices and Their Performance Analysis for<br>Wireless Communications             |

|           | B. Lokesh and B. Lakshmi                                                                       |

| Chapter 2 | Modeling and Simulation of Emerging Low-Power Devices                                          |

|           | M. Venkatesh, G. Lakshmi Priya, S. Arun Samuel, and<br>M. Karthigai Pandian                    |

| Chapter 3 | Tunnel Field-Effect Transistor: An Energy-Efficient<br>Semiconductor Device47                  |

|           | Chandan Kumar Pandey, Saurabh Chaudhury,<br>Neerja Dharmale, and Young Suh Song                |

| Chapter 4 | Analytical Modeling of Surface Potential of a Double-Gate<br>Heterostructure PNPN Tunnel FET69 |

|           | K. Baruah and S. Baishya                                                                       |

| Chapter 5 | Impact of Semiconductor Materials and Architecture Design on<br>TFET Device Performance79      |

|           | M. Saravanan, Eswaran Parthasarathy, J. Ajayan, and D. Nirmal                                  |

| Chapter 6 | Performance Analysis of Emerging Low-Power Junctionless<br>Tunnel FETs                         |

|           | G. Lakshmi Priya, M. Venkatesh, S. Preethi, T. Venish Kumar,<br>and N. B. Balamurugan          |

| Chapter 7 | Recent Developments in Schottky Diodes and Their Applications 127                              |

|           | S. Sreejith, B. Sivasankari, S. Babu Devasenapati, A. Karthika,<br>and Anitha Mathew           |

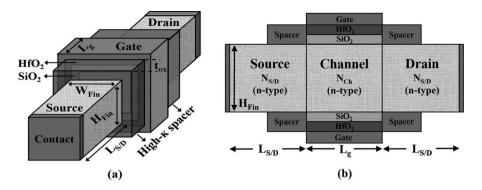

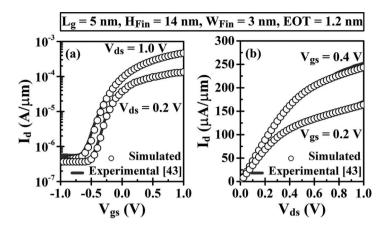

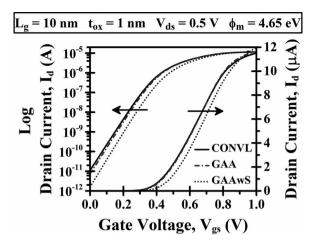

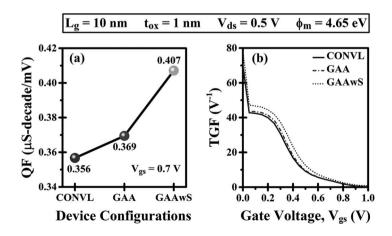

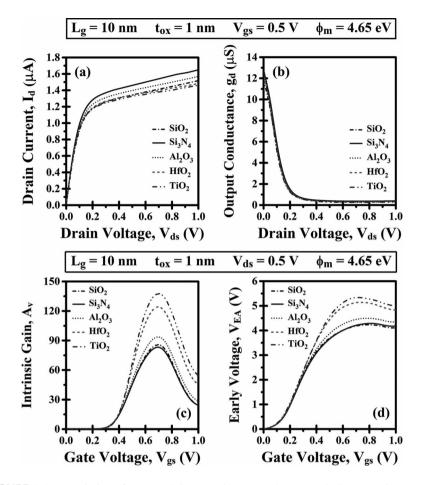

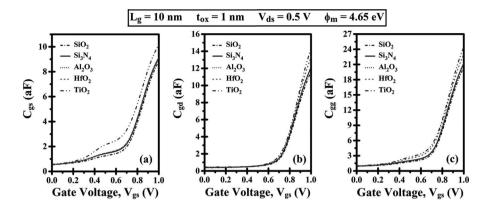

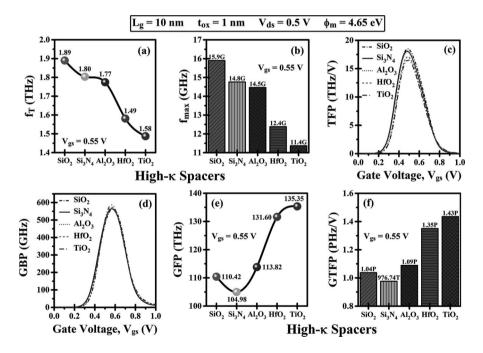

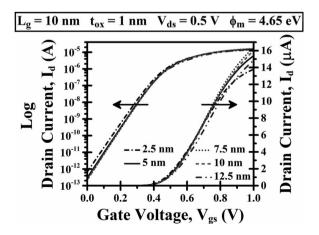

| Chapter 8  | Numerical Study of a Symmetric Underlap S/D High-κ Spacer<br>on JAM-GAA FinFET for Low-Power Applications                                                                   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | B. Kumar and Rishu Chaujar                                                                                                                                                  |

| Chapter 9  | Potential Prospects of Negative Capacitance Field Effect<br>Transistors for Low-Power Applications                                                                          |

|            | Shalini Chaudhary, Nawaz Shafi, Basudha Dewan,<br>Chitrakant Sahu, and Menka                                                                                                |

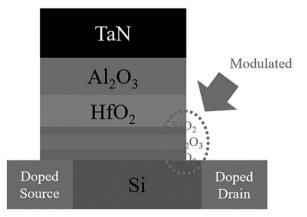

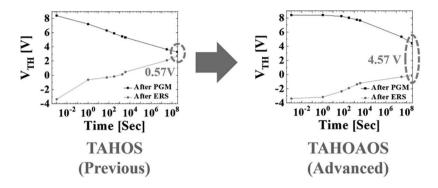

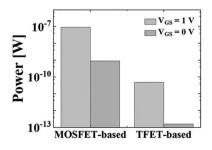

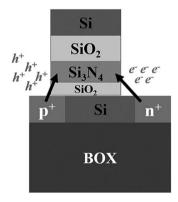

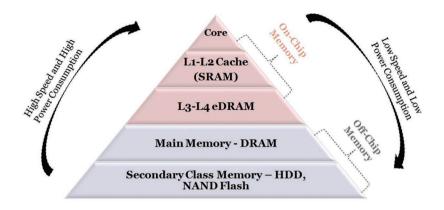

| Chapter 10 | Memory Designing Using Low-Power FETs for Future<br>Technology Nodes                                                                                                        |

|            | Young Suh Song, Shiromani Balmukund Rahi,<br>Chandan Kumar Pandey, Shubham Tayal, Yunho Choi,<br>Bijo Joseph, Tripuresh Joshi, Daryoosh Dideban, and<br>Suman Lata Tripathi |

| Chapter 11 | TFET-Based Flash Analog-to-Digital Converter                                                                                                                                |

| Chapter 12 | Demand of Low-Power-Driven FET as Biosensors in<br>Biomedical Applications                                                                                                  |

| Chapter 13 | 2D Materials for Spin Orbital Torque MRAM:<br>A Path toward Neuromorphic Computing                                                                                          |

|            | Shashidhara M and Abhishek Acharya                                                                                                                                          |

| Index      |                                                                                                                                                                             |

## Editors

Dr. Shubham Tayal is an assistant professor in the Department of Electronics and Communication Engineering at SR University, Warangal, India. He has more than six years of academic/research experience teaching at UG and PG levels. He has received his PhD in Microelectronics & VLSI Design from the National Institute of Technology, Kurukshetra, MTech (VLSI Design) from YMCA University of Science and Technology, Faridabad, and BTech (electronics and communication engineering) from MDU, Rohtak. He has qualified GATE (2011, 2013, 2014) and UGC-NET (2017). He has published more than 25 research papers in various international journals and conferences of repute, and many papers are under review. He is on the editorial and reviewer panel of many SCI/SCOPUS-indexed international journals and conferences. Currently, he is the editor of four books from CRC Press (Taylor & Francis Group, USA). He is a member of various professional bodies like IEEE, IRED, etc. He was the recipient of Green ThinkerZ International Distinguished Young Researcher Award 2020. His research interests include simulation and modeling of multigate semiconductor devices, device-circuit co-design in digital/analog domain, machine learning, and IOT.

**Dr. Abhishek Kumar Upadhyay** obtained his PhD degree in electrical engineering from the Indian Institute of Technology (IIT), Indore, M.P., India, in 2019. After obtaining his PhD, he worked as a post-doctoral fellow in Model Group, Material to System Integration Laboratory (IMS Lab), University of Bordeaux, France. Currently, he is working as Scientific Staff in the Institute for Fundamentals of Electrical Engineering and Electronics, Technische Universität, D-01062, Dresden, Germany. He is actively involved in compact modeling, parameter extraction, 3D EM simulation, measurement, and characterization of RF devices.

**Mr. Deepak Kumar** works as an assistant professor (senior scale) in the Department of Electrical and Electronics Engineering at University of Petroleum and Energy Studies (UPES), Dehradun, India. He has six years of experience in teaching and research. He is pursuing his PhD from UPES, Dehradun, in the field of dye-sensitized solar cells (simulation and experimental study). He obtained his MTech degree from Indian Institute of Technology (IIT), Kanpur, India, in 2015 in the specialization of VLSI and microelectronics (electrical engineering) and received a BTech degree in Electronics Engineering from Harcourt Butler Technical University in 2011. He has published various research articles in reputed journals and conferences, and has also been awarded for the best paper presentation in the ICAMEES conference at UPES in 2018. In addition to academic responsibilities, he also serves the IEEE community as IEEE Student Branch (STB 10991) Counselor at UPES Dehradun and faculty coordinator (department level) for the SPOKEN TUTORIAL, IIT Bombay, MHRD Program. His research area includes VLSI, semiconductor devices (TFET, OSC, OTFT), and circuits and solar cell technology.

Dr. Shiromani Balmukund Rahi received his BSc (physics, chemistry, and mathematics) degree in 2002, MSc (electronics) degree from Deen Dyal Upadhyaya Gorakhpur University, Gorakhpur in 2005, GATE (2009), MTech (microelectronics) from Panjab University Chandigarh in 2011, and Doctorate of Philosophy in 2018 from Indian Institute of Technology, Kanpur, India. He also completed his master's project (MSc) in Central Electronics Engineering Research Institute (CEERI, 2005). He currently works at Mahamaya College of Agriculture Engineering and Technology, Akabarpur, Ambedkar Nagar, Uttar Pradesh, affiliated to Narendra Dev University of Agriculture and Technology, Uttar Pradesh, India. He has successfully published 15 research papers, 1 conference proceedings, and a book chapter. He has also addended and presented his research work in various international conferences and workshops. He has received various reviewer awards and recognizations such as IEEE Golden Reviewers (2018), AIP Advances (2020), and International Journal of Circuit Theory and Applications, Wiley (2020). He is also jointly working with Professor S.C. Misra (Indian Institute of Technology, Kanpur, India) for the development of IoTs for smart applications and Dr Naima Guenifi (LEA Electronics Department, University Mostefa Benboulaid of Algeria) for the development of ultralow-power devices such as tunnel FETs and negative capacitance FETs.

## Contributors

## Abhishek Acharya

Department of ECE SV National Institute of Technology Surat, India

## J. Ajayan

Department of ECE SR University Warangal Telangana, India

## Naushad Alam

Department of Electronics Engineering ZHCET, AMU Aligarh, India

## T. S. Arun Samuel

Department of Electronics and Communication Engineering, National Engineering College Kovilpatti, India

## Asra Ansari

Department of Electronics Engineering ZHCET, AMU Aligarh, India

**Babu Devasenapati, S.** SNS College of Technology Coimbatore, India

## S. Baishya

Department of Electrical Engineering National Institute of Technology Silchar, India

## N. B. Balamurugan

Department of ECE Thiagarajar College of Engineering Madurai, India

## K. Baruah

Department of Electrical Engineering National Institute of Technology Silchar, India

## Saurabh Chaudhury

Department of Electrical Engineering NIT Silchar Assam, India

## Shalini Chaudhary

Department of Electronics and Communication Engineering Malaviya National Institute of Technology Jaipur Jaipur, India

## Rishu Chaujar

Department of Applied Physics Delhi Technological University Delhi, India

#### **Yunho Choi** University of Texas at Austin Austin, Texas

Basudha Dewan Department of Electronics and Communication Engineering Malaviya National Institute of Technology Jaipur Jaipur, India

## Neerja Dharmale

Department of Electrical Engineering NIT Silchar Assam, India

## Daryoosh Dideban

University of Kashan Kashan, Iran

### Mekonnen Getnet

Applied Physics Department Delhi Technological University Delhi, India and Physics Department Debre Tabor University Debre Tabor, Ethiopia

#### **Bijo Joseph**

SRM Institute of Science and Technology Chennai, India

#### **Tripuresh Joshi**

Govind Ballabh Pant Engineering College Pauri, India

#### M. Karthigai Pandian

Department of Electrical Electronics and Communication Engineering GITAM University Bengaluru, India

## A. Karthika

SNS College of Technology Coimbatore, India

## **B. Kumar**

Department of Applied Physics Delhi Technological University Delhi, India

## B. Lakshmi

Centre for Nano Electronics & VLSI Design and School of Electronics Engineering VIT Chennai Chennai, India

#### G. Lakshmi Priya

School of Electronics Engineering (SENSE), VIT University Chennai, India **B. Lokesh** School of Electronics Engineering VIT Chennai Chennai, India

Anitha Mathew IES College of Engineering Chittilappilly, India

#### Menka

Department of Electronics and Communication Engineering Malaviya National Institute of Technology Jaipur Jaipur, India

#### D. Nirmal

Karunya Institute of Technology and Sciences Coimbatore, India

#### **Chandan Kumar Pandey**

School of Electronics Engineering VIT-AP University Amaravati, India

#### **Eswaran Parthasarathy**

SRM Institute of Science and Technology Chennai, India

#### S. Preethi

Department of ECE Sri Krishna College of Technology Coimbatore, India

#### Shiromani Balmukund Rahi

MCAET Ambedkar Nagar Akbarpur, India

#### **Chitrakant Sahu**

Department of Electronics and Communication Engineering Malaviya National Institute of Technology Jaipur Jaipur, India

#### Contributors

**M. Saravanan** Sri Eshwar College of Engineering Coimbatore, India

#### Nawaz Shafi

Department of Electronics and Communication Engineering Malaviya National Institute of Technology Jaipur Jaipur, India

#### Shashidhara, M.

Department of ECE SV National Institute of Technology Surat, India

#### **B.** Sivasankari

SNS College of Technology Coimbatore, India

#### Young Suh Song

Department of Computer Science Korea Military Academy Seoul, South Korea

S. Sreejith SNS College of Technology Coimbatore, India

#### Shubham Tayal

Department of ECE SR University Warangal, India

#### Suman Lata Tripathi

School of Electronics and Electrical Engineering Lovely Professional University Phagwara, India

#### T. Venish Kumar

Department of ECE Nadar Saraswathi College of Engineering & Technology Theni, India

#### M. Venkatesh

School of Electronics and Communication Engineering REVA University Bengaluru, India

# 1 Role of TFET Devices and Their Performance Analysis for Wireless Communications

*B. Lokesh and B. Lakshmi* VIT Chennai

## CONTENTS

| 1.1  | Introd                 | uction    |                                              | 1  |

|------|------------------------|-----------|----------------------------------------------|----|

| 1.2  | Descri                 | ption and | 2                                            |    |

| 1.3  | Results and Discussion |           | 6                                            |    |

|      | 1.3.1                  | Realizat  | ion of Leaf Cells Using IG HJ-DGTFET         | 6  |

|      |                        | 1.3.1.1   | Realization of NAND Logic Circuit            | 6  |

|      |                        |           | Realization of X-OR Logic Circuit            |    |

|      | 1.3.2                  | Realizat  | ion of D Flip-Flop                           | 8  |

|      |                        |           | ion of the QPSK System                       |    |

|      |                        | 1.3.3.1   | Realization of PRBS Generator                | 11 |

|      |                        | 1.3.3.2   | Realization of the Even/Odd Stream Generator |    |

|      | 1.3.4                  | Perform   | ance Analysis of the QPSK System             | 11 |

|      |                        | 1.3.4.1   | Device Level Performance Metrics             | 11 |

|      |                        | 1.3.4.2   | Circuit-Level Performance Metrics            | 14 |

| 1.4  | Conclu                 | usions    |                                              | 16 |

| Refe | rences.                |           |                                              |    |

|      |                        |           |                                              |    |

## 1.1 INTRODUCTION

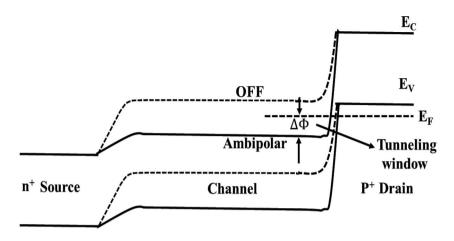

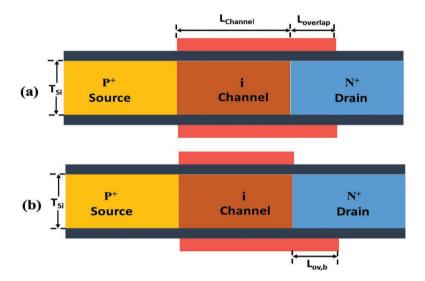

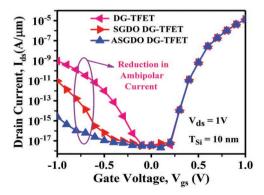

Due to the scaling down of semiconductor devices in the nanometer region, conventional devices such as complementary metal oxide semiconductors (CMOSs) and Moore's law are approaching their limits fast [1]. CMOS-based transistors are no longer in frame in terms of efficiency and hence not suitable for applications requiring low supply voltages due to short channel effects, which in turn limit subthreshold swing (SS) and produce high  $I_{OFF}$ . In the coming decade, there can be an increasing demand for solid-state transistors with channel lengths as short as 1–5 nm for both analog and digital applications [2]. To satisfy Moore's law and achieve a high performance of transistors in nanometer regions, alternate devices such as the p-i-n structure, known as tunnel field effect transistors (TFETs), have been explored and proved to be efficient. Band-to-band tunneling (BTBT) is the principle of mechanism for conduction unlike diffusion in MOS transistors [3]. The mechanism is due to the wave-like properties of electrons, which allows them to pass through barriers with little effort. Due to the mechanism of BTBT, the limitation of SS of 60 mV/decade and better resistance to variations in temperature can be achieved [4,5]. Though this improves the efficiency of the device, TFETs exhibit an ambipolar nature, which means that the device will be conducting for both positive and negative gate voltages. For an n-type TFET (n-TFET) when  $V_{gs}$  < 0, the tunnel junction starts to shift from the source to the drain side. This behavior can cause problems when used in applications such as complimentary logic circuit and hence limits the use of TFET in digital circuits. If this behavior can be suppressed, then TFETs can be used to obtain promising results in digital circuits. Many structures to suppress this behavior are explored in the literature already [6–8].

One such promising structure is an independent gate heterojunction TFET (IG HJ-DGTFET) [9]. The double gate provides control of gate leakage current and improves the magnitude of drain current, whereas the heterojunction structure improves tunneling by modifying the band energy levels in a way to reduce barrier energy for positive gate voltages, which improves  $I_{ON}$ , and increase barrier energy for negative gate voltages, thus reducing  $I_{OFF}$  [10,11]. This makes the devices compatible for applications such as a quadrature phase shift keying (QPSK) system, which demands low power. For TFETs, recent experiments have shown that on using lower-band-gap materials such as InAs or InSb, there is a huge increase in  $I_{ON}$  at lower voltages [12]. Also, to reduce the tunneling barrier and increase the probability for an electron to tunnel through, a combination of materials, GaSb for source and InAs for channel and drain, is used. Another reason for using these material combinations is that they allow lattice-matched growth, which helps in changing the band gap without altering the crystal structure [13].

In this chapter, to show the efficiency of IG HJ-DGTFET, the digital part of the QPSK system has been implemented and validated for low power consumption and less propagation delay. Also, the variations of rise and fall times of an inverter cell used in the QPSK system with respect to temperature have been provided to show temperature independency. The organization of this chapter is as follows: Section 1.2 provides a description of the device and its operation; Section 1.3 provides results and discussion of an implemented QPSK system using IG HJ-DGTFET, and finally Section 1.4 provides the conclusion.

## **1.2 DESCRIPTION AND SIMULATION OF THE DEVICE**

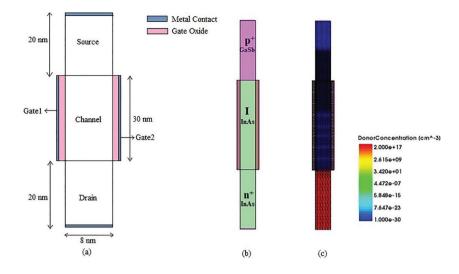

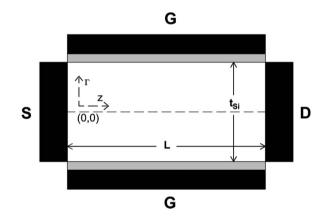

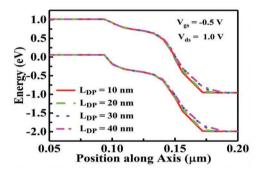

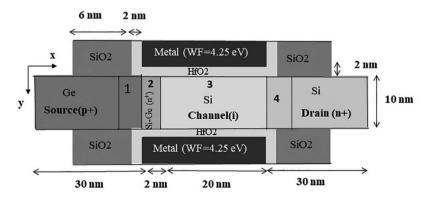

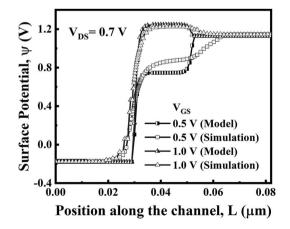

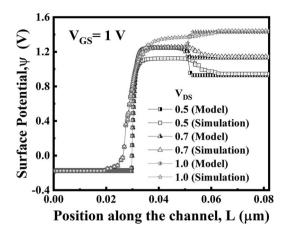

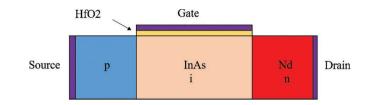

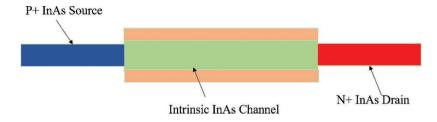

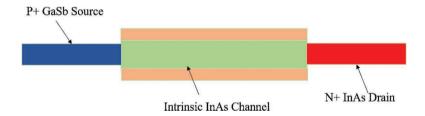

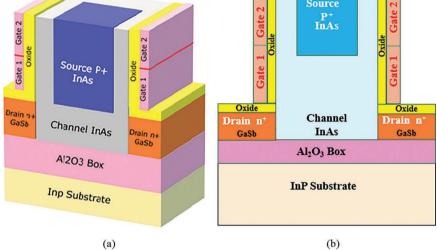

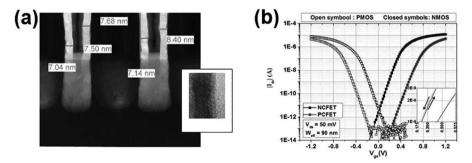

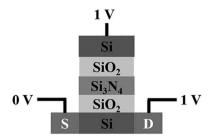

The simulation of the device is carried out using Sentaurus technology computeraided design (TCAD) simulator from Synopsys. Figure 1.1a shows the schematic of the device; Figure 1.1b shows the GaSb-InAs heterojunction TFET structure without doping and Figure 1.1c, with doping/meshing. The device consists of the source doped with GaSb and drain and channel doped with InAs, which is used to increase the  $I_{ON}$  considerably by increasing the energy of the valence band to that of the conduction band at the tunneling junction. This reduces the tunneling barrier and hence increases the probability of tunneling at the junction. The device dimensions, appropriate models for the device simulator, and the DC characteristics obtained are taken from our previous calibrated results [14]. The length of the device is 70 nm with

**FIGURE 1.1** (a) Schematic of the device and (b) the simulated structure of IG HJ-DGTFET without doping and (c) with doping/meshing.

source and drain length of 20 nm each with a channel length of 30 nm and high-k dielectric of silicon nitride  $(Si_3N_4)$ . The geometrical and doping parameters used in this simulation are listed in Table 1.1.

In the device physics, a hydrodynamic model, doping dependence mobility, effects of high and normal electric fields on the saturation of velocity, a Shockley–Read–Hall (SRH) recombination model, and mobility of electrons are used. Also, the Fermi–Dirac statistics is used instead of Boltzmann statistics because of the high doping concentrations used in source and drain. The effects of scattering are ignored as the doped n+ region remains active with the flow of charge carriers even with high doping concentrations. In the used model, it is assumed that only the voltage of gate-source decides band bending, which is necessary in the source region (for line tunneling) or

## TABLE 1.1 Parameter Space of IG HI-DGTFET

| Geometrical/Doping Parameters                  | IG HJ-DGTFET (GaSb-InAs)                       |

|------------------------------------------------|------------------------------------------------|

| Gate length $(L_g)$                            | 30 nm                                          |

| Channel thickness $(T_{ch})$                   | 8 nm                                           |

| Front and back gate oxide thickness $(T_{ox})$ | 1 nm                                           |

| Source dopant/doping concentration             | Boron $-4 \times 10^{19}$ /cm <sup>3</sup>     |

| Drain dopant/doping concentration              | Arsenic $-2 \times 10^{17}$ /cm <sup>3</sup>   |

| Channel doping concentration                   | Intrinsic $-1 \times 10^{15}$ /cm <sup>3</sup> |

| Source material                                | GaSb                                           |

| Drain/channel material                         | InAs                                           |

| Gate work-function                             | 4.85 eV                                        |

|                                                |                                                |

in most of the source-channel region (for point tunneling). The effect of the voltage of drain is considered by assuming that the voltage of drain-source is what determines the location of the level of Fermi energy in the energy bands of drain. Specifically, the used model assumes that the carriers can tunnel into an energy level that is only at or above the level of Fermi energy and the electron Fermi level is assumed to be the same throughout the regions of source and drain from which electrons are generated and tunnel to the drain (considering a majority carrier density).

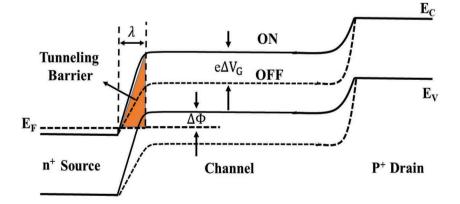

As it is known that the probability of transmission  $T_{WKB}$  is mainly dependent on the tunneling mass and bandgap, variations of these two parameters can improve the  $I_{ON}$  of the device and is calculated using the Wentzel–Kramers–Brillouin (WKB) expression, which is given by

$$T_{\rm WKB} \approx \exp \frac{4\lambda \sqrt{2m^* E_g^3}}{3qh(E_g + \Delta \emptyset)}$$

(1.1)

where  $m^*$  is the electron's effective mass,  $E_g$  is the band gap energy, and q is the charge of electron.  $\lambda$  is the tunneling length, which defines the spatial extent of region of transition at the interface of source and channel,  $\Delta \emptyset$  is the range of energy over which the tunneling can occur or the difference in energies of conduction band in the source and the valence band in the channel, and h is Planck's constant.

$$\lambda = \sqrt{\frac{\varepsilon_{Si}}{\varepsilon_{ox}}} \cdot \sqrt{t_{ox} t_{Si}}$$

(1.2)

where  $t_{ox}$  and  $t_{Si}$  are the thickness of oxide and silicon, respectively, and  $\varepsilon_{ox}$  and  $\varepsilon_{Si}$  are dielectric constants of oxide and silicon, respectively.

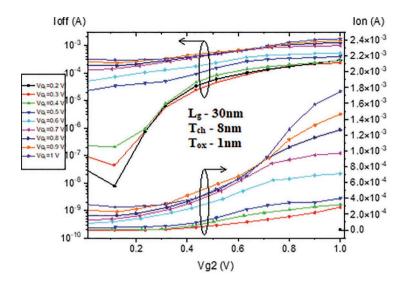

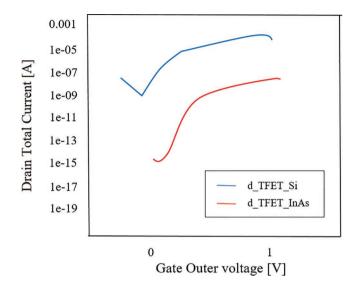

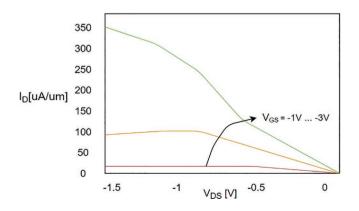

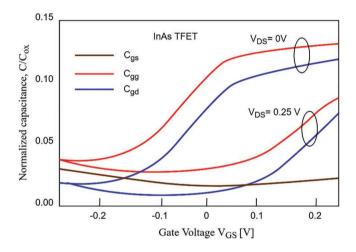

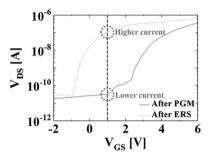

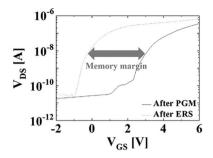

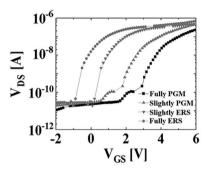

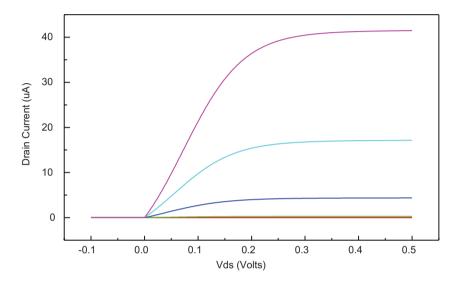

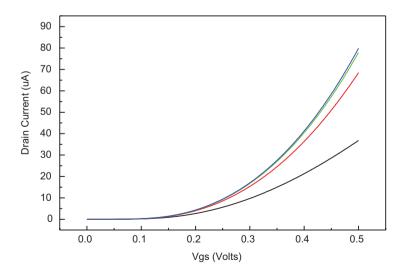

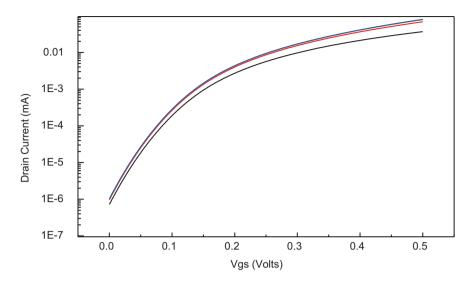

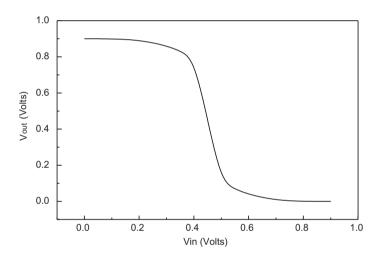

The tunneling barrier not only depends on the energy band gap but also on the carrier generation rate. As the gate voltage rises, the electric field across the channel also increases. The double-gate structure used in this work operates in independent gate (IG) mode, which means that both gates are simulated with different gate voltages ( $V_{g1} \neq V_{g2}$ ). The transfer characteristics of IG HJ-DGTFET with a constant voltage of gate-1 at 1 V and a varying voltage of gate-2 from 0 to 1 V with a drain voltage of 1 V are shown in Figure 1.2. It can be observed that as the gate voltage rises,  $I_{ON}$  and  $I_{OFF}$  start to increase because of carrier generation dependency, which is given in equation (1.3).

$$G_{tun} = A \frac{\left|E^2\right|}{\sqrt{E_g}} \exp\left(-B \frac{E_g^2}{\left|E\right|}\right)$$

(1.3)

where  $G_{tun}$  is the carrier generation rate due to the interband tunneling at the junction, E is the electric field,  $E_g$  is band gap energy, and A and B are constants.

It can be said that by only increasing  $I_{ON}$  of TFETs, it is not sufficient to improve the performance metrics in the circuit level. In the circuit level, there are many performance parameters such as delay, power consumption and dissipation, and rise

FIGURE 1.2 Transfer characteristics of IG HJ-DGTFET.

and fall times. These performance metrics are dependent on device parameters such as drain current in the linear regions and saturation of TFETs, gate and Miller capacitances, output conductance  $(g_d)$ , and tunneling distance. The mentioned device parameters in turn affect SS. The expression for SS is shown in equation (1.4).

$$SS = \ln \frac{KT}{q} \left( 1 + \frac{C_{dep}}{C_{ox}} \right)$$

(1.4)

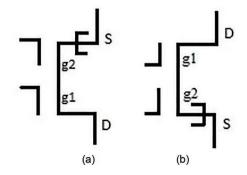

From equation (1.4), it can be made clear that by improving SS, the performance of the device/circuit can be improved to an extent. One way to improve SS is by eliminating the temperature dependency of the device, which has various advantages shown in the results and discussion section. The circuit symbols of both n-type and p-type IG HJ-DGTFETs are shown in Figure 1.3.

FIGURE 1.3 Symbol of IG HJ-DGTFET: (a) PTFET and (b) NTFET.

## 1.3 RESULTS AND DISCUSSION

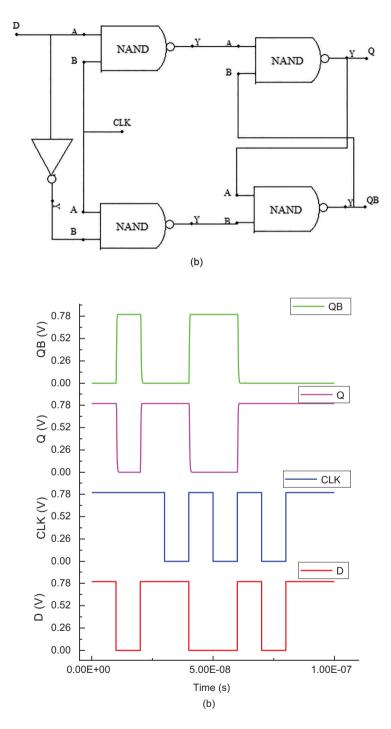

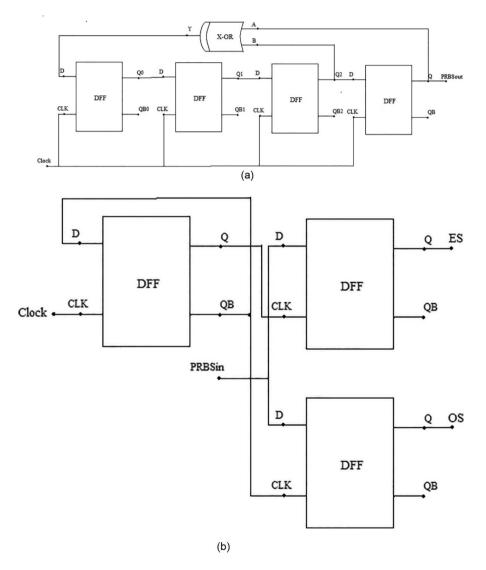

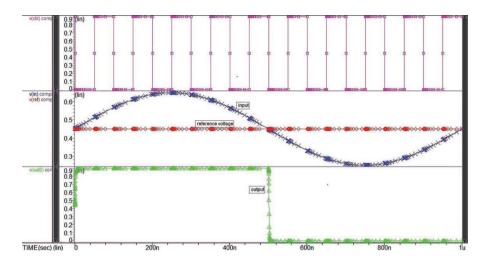

This section provides the implementation and analysis of the QPSK system. The implementation includes the leaf cells, a pseudorandom binary sequence (PRBS) generator, and bit splitter circuits of the QPSK system and the analysis of the same circuits in terms of different performance parameters in both circuit and device levels.

The implementation of the QPSK system is done in three stages:

- 1. Realization and simulation of basic blocks/leaf cells, which are an inverter cell, NAND, and X-OR gates, using n-type and p-type IG HJ-DGTFETs.

- 2. Realization and simulation of D flip-flops (DFFs) using four NAND gates and an inverter cell.

- 3. Realization and simulation of PRBS generator and bit splitter using DFFs.

After each simulation, the values of power consumption and dissipation and propagation delay are extracted. For calculation of power consumption and dissipation, schematics of circuits are verified, and then the Analog Design Environment L (ADEL) window is accessed in which transient simulation is selected for analysis; the stimulus is then given to run the simulation, and from save-all options, all pwr signals are saved. Then, the results browser can be accessed to obtain the power consumption and dissipation.

For calculation of propagation delay, the calculator is accessed from the simulation window and from special functions, the function delay is selected in which the lower and upper threshold values are provided as 0.08 and 0.4 V, respectively, since the propagation delay is defined as 10% and 50% of supply voltage, which is 0.8 V. After applying all the data, an expression is displayed which is evaluated as propagation delay.

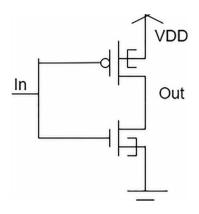

## 1.3.1 REALIZATION OF LEAF CELLS USING IG HJ-DGTFET

The leaf cells of the QPSK system are NAND and inverter cells. In this section, these cells are realized using IG HJ-DGTFETs, which are the fundamental cells in the construction of D flip-flops. The constructed D flip-flop is used to realize PRBS and even/odd sequence generators.

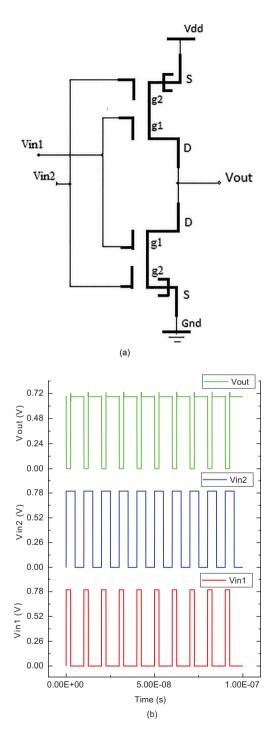

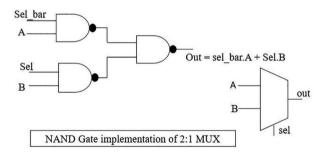

## 1.3.1.1 Realization of NAND Logic Circuit

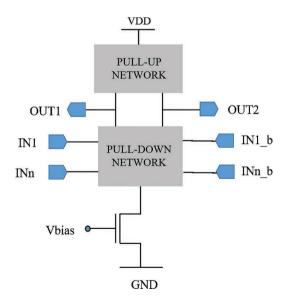

The circuit diagram of IG HJ-DGTFET based NAND is shown in Figure 1.4a. Two gates, g1 of both n- and p-type IG HJ-DGTFETs, are shorted together and given to  $V_{in1}$ . Similarly, gates g2 of both types of IG HJ-DGTFETs are shorted together and given to  $V_{in2}$ . When one of the inputs is given logic high or when both the inputs are given logic low, that is,  $V_{in1}$  to logic high and  $V_{in2}$  to logic low or  $V_{in1}$  and  $V_{in2}$  are given logic low, the transistor in the pull-up network is turned on and the output gets a logic high signal due to the shorted path between  $V_{DD}$  and the output. When both inputs are given logic high, both transistors in pull-up and pull-down networks are turned off and the output gets logic low. The timing diagram of the IG HJ-DGTFET-based NAND gate is shown in Figure 1.4b.

**FIGURE 1.4** (a) NAND gate realization using IG HJ-DGTFET. (b) Timing diagram of IG HJ-DGTFET-based NAND gate.

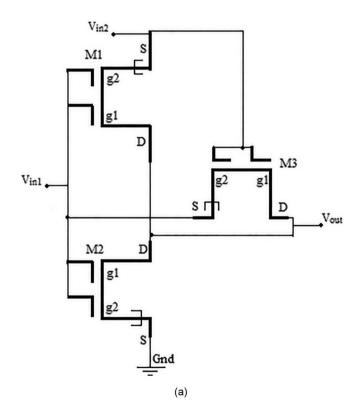

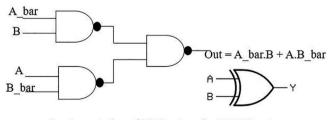

## 1.3.1.2 Realization of X-OR Logic Circuit

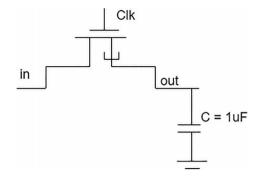

The circuit of the IG HJ-DGTFET-based X-OR gate is shown in Figure 1.5a. This circuit requires only three transistors unlike conventional X-OR gate circuits [15]. This X-OR gate is based on the inverter and pass transistor logic (PTL). In PTL, the transistors act as simple switches between the nodes to pass the logic levels using the NTFET and PTFETs [16]. When inputs are given the same logic, either logic low/ high, the output node is pulled down to logic low because of the transistor M3 being turned off owing to no potential difference between gate and source. When the inputs are different, the transistor M3 is pulled to logic high. The logic levels, logic high and logic low, for different combinations of input are shown in Table 1.2. The timing diagram of the IG HJ-DGTFET-based X-OR gate is shown in Figure 1.5b.

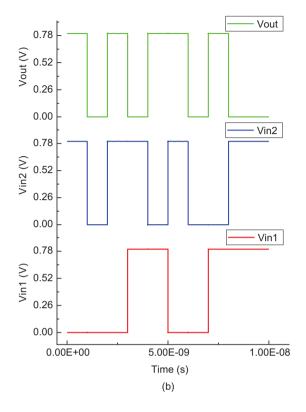

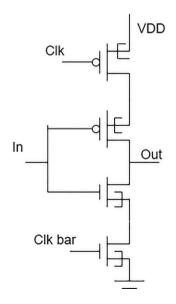

## 1.3.2 REALIZATION OF D FLIP-FLOP

In this section, D flip-flop realization using NAND and inverter logic gates is given and shown in Figure 1.6a. The input data is referred to as "D"; when the input D is given logic 1 or logic high, the flip-flop goes into a state called "SET", and when the input data is given as logic 0 or logic low, a state of "RESET" occurs in the flip-flop.

**FIGURE 1.5** (a) XOR gate realization using IG HJ-DGTFET. (b) Timing diagram of IG HJ-DGTFET-based X-OR gate.

(Continued)

**FIGURE 1.5 (CONTINUED)** (a) XOR gate realization using IG HJ-DGTFET. (b) Timing diagram of IG HJ-DGTFET-based X-OR gate.

| Output Logic<br>Combinations | Levels of X-OR Gate fo | or Different Input |

|------------------------------|------------------------|--------------------|

| Inputs                       |                        | Output             |

| А                            | В                      | Y                  |

| 0                            | 0                      | $ V_{TP} $         |

| 0                            | 1                      | $V_{DD}$           |

| 1                            | 0                      | $V_{DD} - V_{TP}$  |

| 1                            | 1                      | Gnd                |

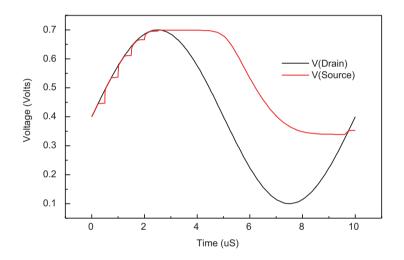

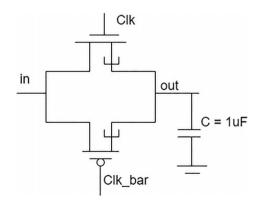

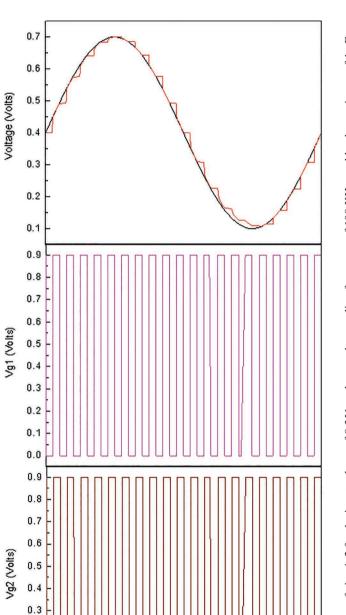

But this kind of response is not desired for the QPSK system because the output of the flip-flop will always respond to the data input D on every pulse applied. To remove this undesired effect, an additional input called "CLK" is used to make the flip-flop go into "SET" state only when "CLK" transitions from logic high to logic low, making the flop positive-edge-triggered. The timing diagram of the D flip-flop logic circuit is shown in Figure 1.6b.

**FIGURE 1.6** (a) D flip-flop realization using NAND and inverter logic gates. (b) Timing diagram of D flip-flop logic circuit.

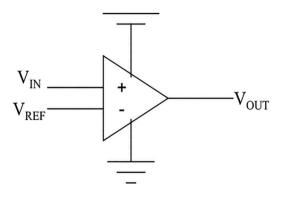

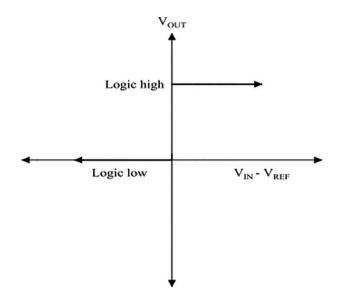

## 1.3.3 REALIZATION OF THE QPSK SYSTEM

In this section, the realization of the digital part of the QPSK system is implemented. This can be achieved by connecting the following two systems in cascade:

- 1. PRBS generator.

- 2. Bit splitter or even/odd stream generator.

The output of the PRBS generator is given to bit splitter or the even/odd sequence generator [17,18]. PRBS is based on the concept of linear feedback shift register (LFSR) in which each bit is shifted from each D flip-flop. In the PRBS circuit, an X-OR gate is used between the last two flip-flops to give the difference output to the first D flip-flop. This creates a loop to generate random sequences. Once the random sequence is generated from the PRBS circuit, the PRBS output is given to the bit splitter circuit, which splits the sequence into odd and even stream of bits.

## 1.3.3.1 Realization of PRBS Generator

## 1.3.3.2 Realization of the Even/Odd Stream Generator

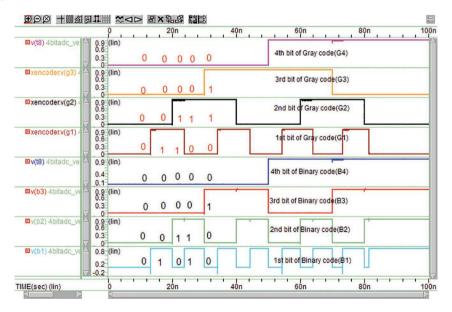

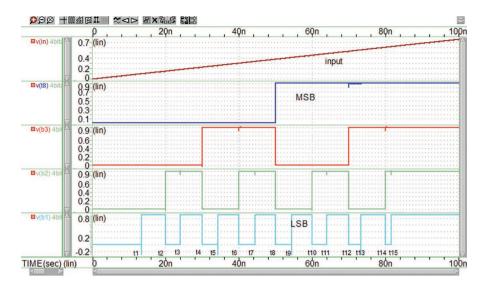

The realization of the even/odd stream generator is shown in Figure 1.7b. This stage divides the input bit sequence from PRBS into even and odd bits. The PRBS output sent to the bit splitter splits the sequence as an even bit sequence 11000100 and an odd bit sequence 1 1 0 1 0 1 1 1. The first D flip-flop is used to divide the input clock into two, which is then sent to the second and third flip-flops which split the sequence. These divisions of clocks send Q to even-splitting flip-flop and QB to the odd-splitting flip-flop. The second flip-flop shifts the bits only in even positions and the third flip-flop shifts the bits only in odd positions. The timing diagram of the bit splitter circuit is shown in Figure 1.7c.

## 1.3.4 PERFORMANCE ANALYSIS OF THE QPSK SYSTEM

This section deals with the performance analysis of the QPSK system. Both the device level and circuit-level parameters are extracted and tabulated.

## 1.3.4.1 Device Level Performance Metrics

Table 1.3 gives the device performance parameters of IG HJ-DGTFET.

In the device level, the mentioned performance metrics are affected by parameters such as drive current ( $I_{ON}$ ) and SS, which are optimized to deliver the best performance. The optimization is done as follows. As shown in equation (1.2),  $\lambda$  is directly proportional to  $t_{ox}$  and affects SS; it is directly dependent on thermal voltage shown in equation (1.4). But despite the relation between SS, rise and fall times, and thermal voltage, the effect of oxide capacitance dominates as very thin oxide of 1nm is taken. Further effects of  $C_{ox}$  are discussed in the circuit-level performance metrics section.

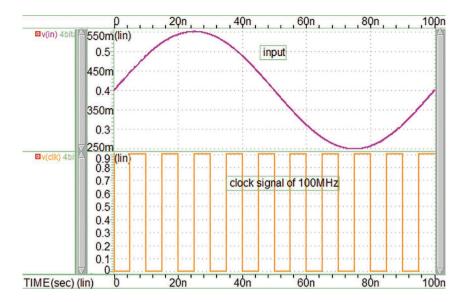

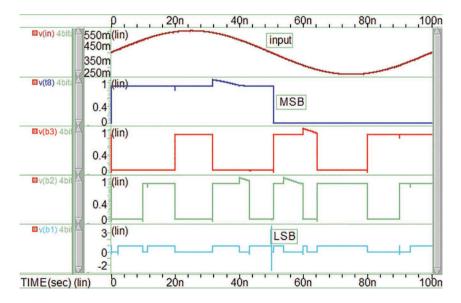

**FIGURE 1.7** (a) Realization of PRBS generator. (b) Realization of even/odd stream generator. (c) Timing diagram of PRBS and bit splitter circuits.

(Continued)

**FIGURE 1.7 (CONTINUED)** (a) Realization of PRBS generator. (b) Realization of even/ odd stream generator. (c) Timing diagram of PRBS and bit splitter circuits.

The usage of a lower-band-gap material such as GaSb-InAs material affected the band gap, which directly points to SS. From Table 1.3, it can be seen that the extracted SS is very close to the ideal SS, which is 60 mV/decade, and this feature makes it to contribute to lesser delay and temperature independency. In addition to this, the other two factors, usage of the optimized oxide thickness and GaSb-InAs material, also contributed to less leakage current ( $I_{OFF}$ ) in the device, which reduced the power dissipation in the device level. The output conductance ( $g_d$ ) is optimized by obtaining

| renormance metrics of its Hj-Duff Li |                        |

|--------------------------------------|------------------------|

| Device Parameter                     | Value                  |

| $I_{ON}$                             | 1.287 mA               |

| I <sub>OFF</sub>                     | 20.08 nA               |

| $I_{ON}/I_{OFF}$                     | $0.6409 \times 10^{5}$ |

| SS                                   | 58.8 mV/decade         |

| $C_{gd}$                             | 44.57 pF               |

| $g_d$                                | 0.162 µS               |

| $g_m$                                | 0.597 mS               |

| $f_t$                                | 979.87 GHz             |

| GBP                                  | 213.5 GHz              |

|                                      |                        |

## TABLE 1.3 Performance Metrics of IG HJ-DGTFET

a lower drain saturation voltage,  $V_{ds}$ , which is achieved by controlling the threshold voltage. Due to the higher transconductance  $(g_m)$ , the unity gain cut-off frequency  $(f_i)$  was increased, which resulted in an optimal gain-bandwidth product (GBP) needed for the QPSK system. The GBP for the device is calculated using equation (1.5) [21].

$$GBP = \frac{g_m}{20\pi \times C_{gd}}$$

(1.5)

#### 1.3.4.2 Circuit-Level Performance Metrics

The procedure to compute power and delay is explained in the Cadence manual [22,23]. The performance metrics considered here are propagation delay and power consumption and dissipation. The average power and the propagation delay are measured by performing the transient analysis of logic circuits. The parameter propagation delay is affected by the rise and fall times, and as previously discussed in device performance metrics, these rise and fall times are affected by  $C_{ox}$ , which can be seen from the rise time ( $t_{PLH}$ ) relation with respect to  $C_{ox}$  shown in equation (1.6). The inverter used in the QPSK system produced rise and fall times of 0.09 ps. With respect to variations in temperature from 27°C to 54°C, these rise and fall times are varied by a maximum of 2.3 ps. The fall time equation is given as equation (1.7).

$$t_{PLH} = \frac{C_L}{\mu_p \ C_{ox} \frac{W}{L} \left( V_{in} - V_{TH} \right)^2}$$

(1.6)

$$t_{PHL} = \frac{C_L}{\mu_n \ C_{ox} \frac{W}{L} \left(V_{in} - V_{TH}\right)^2}$$

(1.7)

where  $t_{PLH}$  and  $t_{PHL}$  are rise and fall times, respectively.  $C_L$  is the load capacitance,  $\mu$  is the mobility of the charge carriers,  $C_{ox}$  is oxide capacitance, W and L are width and

length of the channel, respectively, and  $V_{in}$  and  $V_{TH}$  are input and threshold voltages, respectively. From equations (1.6) and (1.7), propagation delay is defined as the time measured between the 50% transition points of the input and output waveforms and is calculated using equation (1.8).

$$t_{pd} = \frac{t_{PHL} + t_{PLH}}{2}$$

(1.8)

In the parameter of power, two different power metrics are shown here: one is power consumption, which is the power drawn from the supply to obtain the desired output, and the other is power dissipation, which is unproductive and undesired, such as the power drawn from supply even when the transistor in a logic circuit is in the OFF state or simply the power consumed even when input is not given. The power consumption and dissipation are given in equations (1.9 and 1.10), respectively. Table 1.4 provides the overall performance metrics of the QPSK system.

$$P_C = \left(\sum \text{ (leakage current)} \times V_{DD}\right) + C_L \times V_{DD}^2 \times f_i$$

(1.9)

$$P_D = C_{pd} \times V_{DD}^2 \times f_i \tag{1.10}$$

where  $P_c$  and  $P_D$  are power consumption and dissipation, respectively.  $C_{pd}$  is dissipation capacitance and is calculated using equation (1.11).  $V_{DD}$  is the supply voltage and  $f_i$  is the input frequency.

$$C_{pd} = \frac{I_{DS}}{V_{DD} \times f_i} - C_{L_{eff}}$$

(1.11)

$C_{L_{eff}}$  can be calculated by multiplying the number of switching bits ( $N_{SW}$ ) and drain capacitance ( $C_d$ ).

From Table 1.4, it can be inferred that the overall performance of the QPSK system can be said to be improved with the use of this IG HJ-DGTFET structure against the QPSK system, which is discussed in the literature [24]. In the circuit level, since the complexity of circuits mainly affects power consumption, it has been reduced as

## Performance Metrics of the QPSK System

**TABLE 1.4**

| Logic Gates               | <b>Propagation Delay</b> | Power Consumption | <b>Power Dissipation</b> |

|---------------------------|--------------------------|-------------------|--------------------------|

| NAND gate (IG HJ-DGTFET)  | 43.53 ps                 | 38.02 pW          | 0.652 aW                 |

| X-OR gate (IG HJ-DGTFET)  | 13.31 ps                 | 6.147 pW          | 21.78 pW                 |

| D flip-flop               | 346.1 ps                 | 66.05 nW          | 7.731 pW                 |

| PRBS generator            | 200.09 ps                | 35.19 nW          | 2.600 nW                 |

| Odd/even stream generator | ES: 39.98 ps             | 205.3 nW          | 2.156 nW                 |

|                           | OS: 106.1 ps             |                   |                          |

a first step using IG mode in NAND gate, which ultimately reduced the complexity by half, and in X-OR gate, an inverter and PTL have been applied to reduce the complexity. In the X-OR gate, reusing signals and passing them using a PTFET are performed. This reduces the delay as the signals are only passed based on the difference between logic levels, and because of the reuse of signals, no external supply is needed, which means no active power is drawn and which further reduces power consumption. Therefore, as the performance metrics are enhanced considering both device and circuit-level parameters, it can be said that the overall performance of the QPSK system is totally enhanced.

## 1.4 CONCLUSIONS

In this chapter, an IG HJ-DGTFET has been designed in such a way that the device when used in the QPSK system produces an optimal subthreshold swing, high transconductance, and GBP required for the system at the cost of the  $I_{ON}/I_{OFF}$  ratio of the device. Also, the results show negligible rise and fall times of the inverter cell, which is an advantage for the system, if it is to be used in temperature-variant surroundings. SS being close to the ideal value, lesser I<sub>OFF</sub> and the design of lowercomplexity circuits combined produced a system with very low power consumption and less propagation delay. Circuit techniques such as IG mode and PTL helped in reducing power dissipation, which contributes to the increased lifetime of the entire OPSK system. With advantages such as temperature independency, high GBP, and low power consumption, the implemented OPSK system can be used in areas such as cellular phone systems, which demands low power, satellite transmission systems, or WIFI modems, which require temperature independency and high bandwidth. Also, the obtained results of less propagation delay enable higher frequency of operation for the QPSK system. Hence, it can be concluded that the implemented system consumes less power and produces low latency, which is the key feature required for any low-power RF wireless communications.

#### REFERENCES

- S. Garg and S. Saurabh, "Implementing Logic Functions Using Independently-Controlled Gate in Double-Gate Tunnel FETs: Investigation and Analysis," in *IEEE Access*, vol. 7, pp. 117591–117599, 2019, doi: 10.1109/ACCESS.2019.2936610.

- L. Barboni, M. Siniscalchi and B. Sensale-Rodriguez, "TFET-Based Circuit Design Using the Transconductance Generation Efficiency gm/Id Method," in *IEEE Journal* of the Electron Devices Society, vol. 3, no. 3, pp. 208–216, May 2015, doi: 10.1109/ JEDS.2015.2412118.

- S. Khandelwal, J. Duarte, A. S. Medury, V. Sriramkumar, N. Paydavosi, D. Lu, C. H. Lin, M. Dunga, S. Yao, T. Morshed, et al., *BSIM-CMG 109.0. 0 Multi-Gate MOSFET Compact Model Technical Manual*. Regents University California, Berkeley, 2015.

- D. H. Morris, U. E. Avci, R. Rios and I. A. Young, "Design of Low Voltage Tunneling-FET Logic Circuits Considering Asymmetric Conduction Characteristics," in *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 4, no. 4, pp. 380–388, Dec. 2014, doi: 10.1109/JETCAS.2014.2361054.

- W. G. Vandenberghe, A. S. Verhulst, G. Groeseneken, B. Soree and W. Magnus, "Analytical Model for a Tunnel Field-Effect Transistor," MELECON 2008- The 14th IEEE Mediterranean Electrotechnical Conference, 2008, pp. 923–928, doi: 10.1109/ MELCON.2008.4618555.

- C. Convertino, C.B. Zota, H. Schmid, D. Caimi, L. Czornomaz, A.M. Ionescu and K.E. Moselund, "A Hybrid III–V Tunnel FET and MOSFET Technology Platform Integrated on Silicon," in *Nature Electronics*, vol. 4, no. 2, pp. 162–170, 2021, doi: 10.1038/ s41928-020-00531-3.

- A. Sharma, A. A. Goud and K. Roy, "GaSb-InAs n-TFET with Doped Source Underlap Exhibiting Low Subthreshold Swing at Sub-10-nm Gate-Lengths," in *IEEE Electron Device Letters*, vol. 35, no. 12, pp. 1221–1223, Dec. 2014, doi: 10.1109/ LED.2014.2365413.

- 8. H. Lu, T. Ytterdal and A. Seabaugh. Notre dame TFET model, Sep 2017.

- 9. A. Varghese, C. S. Praveen, A. P. Mani and A. Ravindran, InGaAs/GaAsSb HETEROJUNCTION TFET, 2015.

- U. Dutta, M. K. Soni and M. Pattanaik, "Design and Analysis of Tunnel FET for Low Power High Performance Applications," in *International Journal of Modern Education* and Computer Science, vol. 10, no. 1, p. 65, 2018.

- M.R. Salehi, E. Abiri, S. E. Hosseini and B. Dorostkar, "Analysis and Optimization of Tunnel FET with Band Gap Engineering," 2013 21st Iranian Conference on Electrical Engineering, 2013, pp. 1–4, doi: 10.1109/IranianCEE.2013.6599607.

- K. Boucart and A. M. Ionescu, "Double-Gate Tunnel FET with High-κ Gate Dielectric," in *IEEE Transactions on Electron Devices*, vol. 54, no. 7, pp. 1725–1733, 2007. doi: 10.1109/TED.2007.899389

- A. Madhukar and S. Das Sarma, "Intrinsic and Extrinsic States at Lattice Matched Interfaces between III-V Compound Semiconductors: The InAs/GaSb(110) System," in *Journal of Vacuum Science and Technology*, vol. 17, pp. 1120–1127, 1998, doi: 10.1116/1.570626

- 14. M. Pown and B. Lakshmi, "Performance Analysis of InAs- and GaSb-InAs-Based Independent Gate Tunnel Field Effect Transistor RF Mixers," in *Journal* of Computational Electronics, vol. 16, pp. 676–684, 2017, doi: 10.1007/ s10825-017-1005–8

- 15. K. Dhar, "Design of a Low Power, High Speed and Energy Efficient 3 Transistor XOR Gate in 45nm Technology using the Conception of MVT Methodology," 2014 International Conference on Control, Instrumentation, Communication and Computational Technologies, ICCICCT 2014, 2014, doi: 10.1109/ICCICCT.2014.6992931.

- R. Zimmermann and W. Fichtner, "Low-Power Logic Styles: CMOS Versus Pass-Transistor Logic," in *IEEE Journal of Solid-State Circuits*, vol. 32, no. 7, pp. 1079– 1090, July 1997, doi: 10.1109/4.597298.

- R. Rameshkumar and J. N. Swaminathan, "A New Hardware Design and Implementation of QPSK Modulator in Normal and 4-QAM Mode for 5G Communication Networks," International Conference on Inventive Computation Technologies, 2020, doi: 10.1007/978-3-030–33846-6\_29.

- N. Haridas and M. N. Devi, "Efficient Linear Feedback Shift Register Design for Pseudo Exhaustive Test Generation in BIST," 2011 3rd International Conference on Electronics Computer Technology, 2011, pp. 350–354, doi: 10.1109/ICECTECH.2011.5941621.

- M. JanakiRani and S. Malarkkan, "Design and Analysis of a Linear Feedback Shift Register with Reduced Leakage Power," in *International Journal of Computer Applications*, vol. 56, pp. 9–13, 2012, doi: 10.5120/8957–3159.

- B. Singh, A. Khosla and S. Bindra, "Power Optimization of Linear Feedback Shift Register (LFSR) for Low Power BIST," 2009 IEEE International Advance Computing Conference, 2009, pp. 311–314, doi: 10.1109/IADCC.2009.4809027.

- D. S. Yadav, D. Sharma, B. R. Raad and V. Bajaj, "Dual Workfunction Hetero Gate Dielectric Tunnel Field-Effect Transistor Performance Analysis," 2016 International Conference on Advanced Communication Control and Computing Technologies (ICACCCT), 2016, pp. 26–29, doi: 10.1109/ICACCCT.2016.7831593.

- 22. Cadence Tutorial 2: Schematic Entry & Digital Simulation. Cadence Tutorial 1 (cu.edu.eg).

- 23. Power measurement with Cadence EDA: Power Measurement Guide (msu.edu).

- Z. Ji, S. Zargham and A. Liscidini, "Low-Power QPSK Transmitter Based on an Injection-Locked Power Amplifier," ESSCIRC 2018- IEEE 44th European Solid State Circuits Conference (ESSCIRC), 2018, pp. 134–137, doi: 10.1109/ESSCIRC.2018.8494300.

# 2 Modeling and Simulation of Emerging Low-Power Devices

*M. Venkatesh* REVA University

G. Lakshmi Priya VIT University

S. Arun Samuel National Engineering College

*M. Karthigai Pandian* GITAM University

## CONTENTS

| 2.1 | Introduction               |                                      |    |

|-----|----------------------------|--------------------------------------|----|

| 2.2 | Gordon Moore's Law Scaling |                                      |    |

| 2.3 | 3 Basics of Tunnel FET     |                                      |    |

|     | 2.3.1                      | Components of Tunnel FET             | 22 |

|     | 2.3.2                      | Scaling of MOSFET                    | 24 |

| 2.4 | Short-                     | Channel Effects                      |    |

|     | 2.4.1                      | Drain-Induced Barrier Lowering       | 25 |

|     | 2.4.2                      | Channel-Length Modulation            | 25 |

|     | 2.4.3                      | Hot Carrier Effects                  | 25 |

|     | 2.4.4                      | Velocity Saturation                  | 26 |

|     | 2.4.5                      | Gate Oxide Leakage                   | 26 |

| 2.5 | Noncla                     | assical MOSFET Structures            | 27 |

| 2.6 | Engine                     | eering Techniques                    | 27 |

|     | 2.6.1                      | Multigate Architectures              |    |

|     | 2.6.2                      | Gate Oxide Engineering               |    |

|     | 2.6.3                      | High-K Gate Dielectrics              |    |

|     | 2.6.4                      | Stacked Gate Oxide Structure         |    |

|     | 2.6.5                      | Channel Engineering                  |    |

| 2.7 | Model                      | ling Techniques of Low-Power Devices | 34 |

|     | 2.7.1                      | Analytical Modeling                  |    |

|     | 2.7.2                      | Quasi Transport Modeling             | 34 |

|      | 2.7.3   | Charge-Based Modeling                                   | 35 |  |

|------|---------|---------------------------------------------------------|----|--|

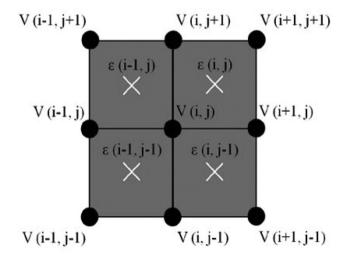

|      | 2.7.4   | Numerical Modeling                                      | 35 |  |

|      | 2.7.5   | Finite Element Modeling                                 | 35 |  |

|      | 2.7.6   | Finite Difference Modeling                              | 36 |  |

|      | 2.7.7   | Monte Carlo Modeling                                    | 37 |  |

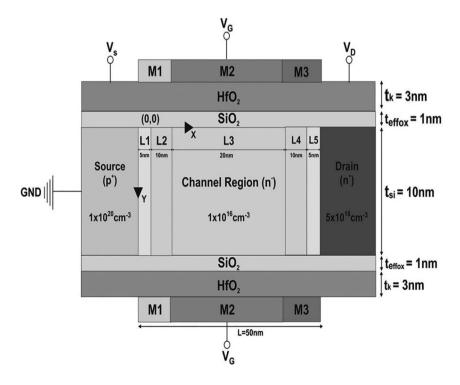

| 2.8  | Double  | e-Halo Gate-Stacked Triple-Material Double L-Gate TFET: |    |  |

|      | Perform | nance Analysis                                          | 37 |  |

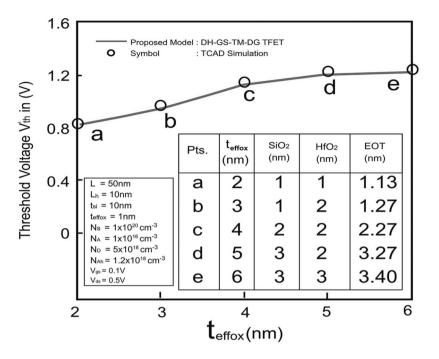

|      | 2.8.1   | Threshold Voltage Modeling                              | 38 |  |

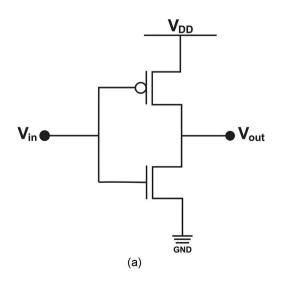

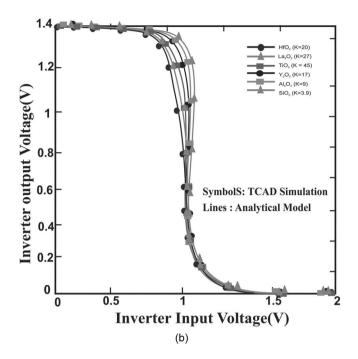

| 2.9  | Impler  | nentation of CMOS Inverter in Halo-Doped Tunnel FET     | 38 |  |

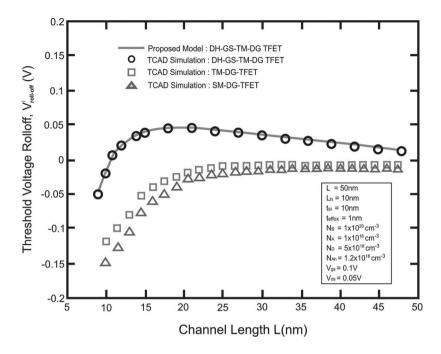

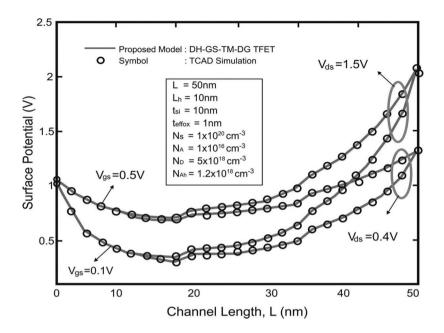

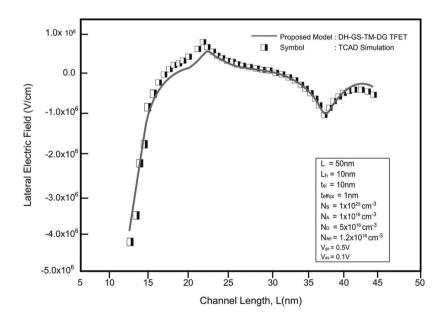

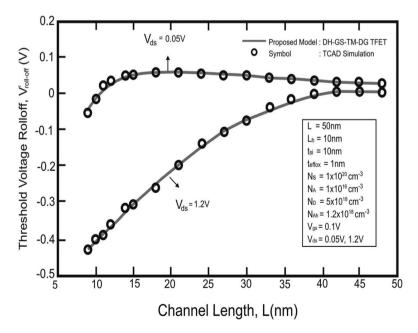

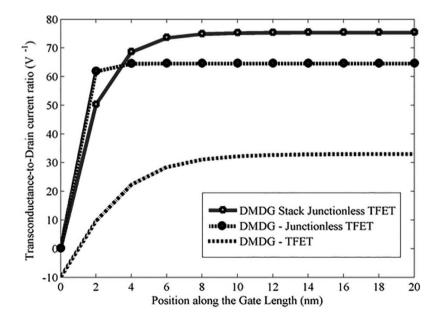

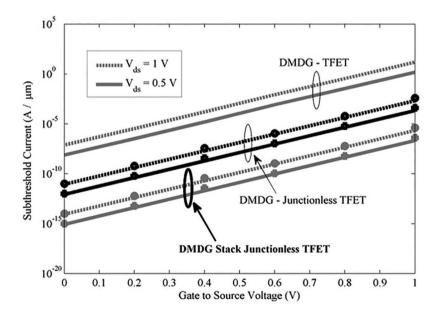

| 2.10 | Perform | Performance Investigation of DH-GS-TM-DG TFET4          |    |  |

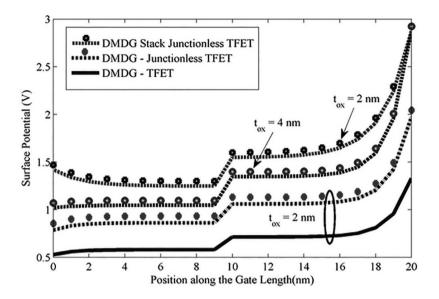

|      | 2.10.1  | Surface Potential Analysis                              | 41 |  |

|      | 2.10.2  | Lateral Electric Field Analysis                         | 41 |  |

|      | 2.10.3  | Effective Oxide Thickness                               | 41 |  |

|      | 2.10.4  | Threshold Voltage Roll-Off                              | 41 |  |

| 2.11 | Conclu  | isions                                                  | 44 |  |

| Refe | rences  |                                                         | 44 |  |

|      |         |                                                         |    |  |

## 2.1 INTRODUCTION

The human body is comprised of a huge number of biological cells, and an integrated circuit (IC) is comprised of a huge number of transistors. Transistors are a fundamental structure of present-day electronic devices. As far back as the appearance of complementary metal oxide semiconductor (CMOS) circuits, the components of the transistor have been ceaselessly downsized so as to pack more rationale on to a silicon wafer and furthermore to lessen power control utilization in circuits. In the recent scenario, with cell phones gaining prevalence, the quest for low-control gadgets with steep switching attributes has become significant. Profoundly scaled metal oxide semiconductor field effect transistors (MOSFETs) are rendered inadmissible for low-power-control applications because of their thermal point in their switching behavior. Consequently, the tunnel field effect transistor (TFET) is being investigated widely for ultralow-power applications. Tunnel FET has a steep switching trademark as it operates upon the principle of band-to-band tunneling (BTBT) effect. In the course of recent years, TFETs have been vigorously studied by researchers in the field of semiconductor gadgets over the world.

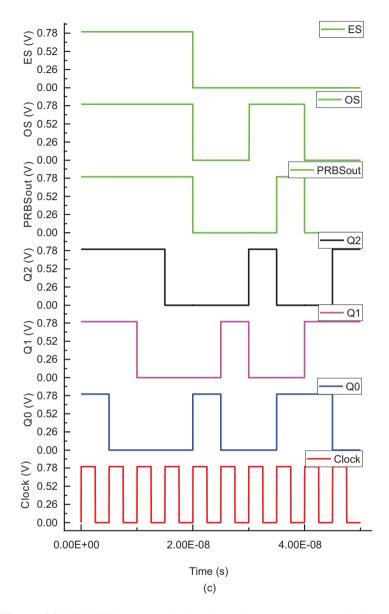

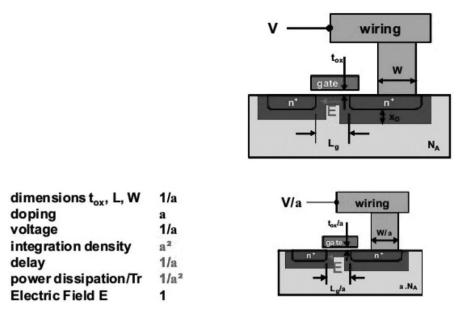

## 2.2 GORDON MOORE'S LAW SCALING

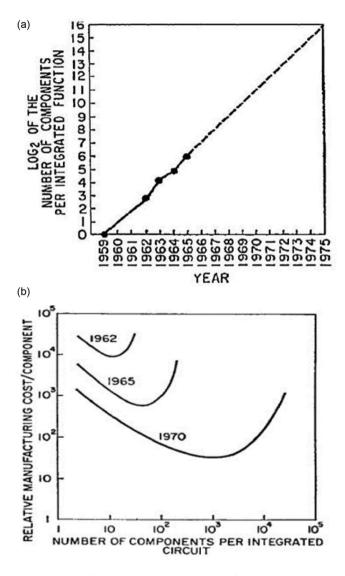

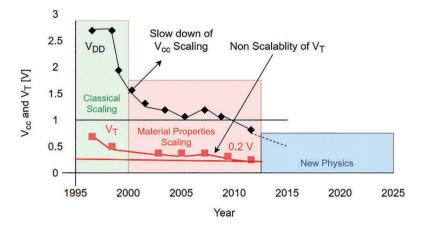

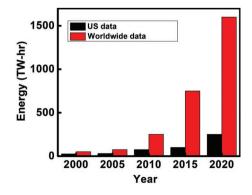

Scaling, as portrayed by Moore's perception, has multiplied the thickness with each generation rate with the related cost decrease of an integrated circuit. By the 1980s, complementary MOS (CMOS) was developed as the innovation of things to come, and by the 1990s, the CMOS overwhelmed all of the microelectronic applications and is dominant to date [1,2]. This is fundamentally a direct result of the low power utilization of CMOS circuits and their capacity to downsize to incredibly small scales as shown by Dennard of IBM. Figure 2.1 shows the component size and gate length as an element of time. One hundred nanometers is a principal innovation milestone. It is the division point between small-scale innovation and nanotechnology.

FIGURE 2.1 Moore's law.

The semiconductor manufacturing surpassed it in the twenty-first century from micro-ICs to nano-ICs. Moore's law has been the marker of progress in IC innovation throughout the five previous decades. According to Moore's law, the MOS innovation crosses a few innovation hubs during its downsizing venture.

## 2.3 BASICS OF TUNNEL FET

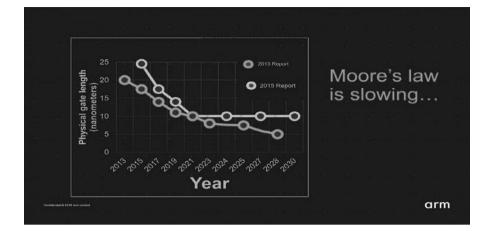

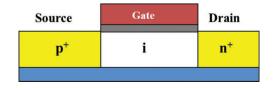

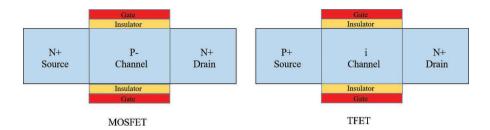

"Tunnel field effect transistor" (TFET) is a reverse-biased gated p-i-n diode. Because of the band-to-band tunneling of charge carriers between the source and the channel, the TFET's output current is determined by this BTBT process [3]. However, the carrier injection mechanism in MOSFETs is dependent on heat injection. Because of its decreased leakage current and fewer short-channel effects (SCEs), the TFET device is ideal for low-power applications. On the source side, the BTBT area is approximately 10 nm<sup>2</sup>, and the device may be scaled up to 20 nm. These include reduced subthreshold swing (60 mV/decade), increased working speed, and a reduced threshold voltage roll-off ( $V_{troll-off}$ ). In addition, the TFET does not have a punch-through effect because of its reverse-biased p-i-n architecture.

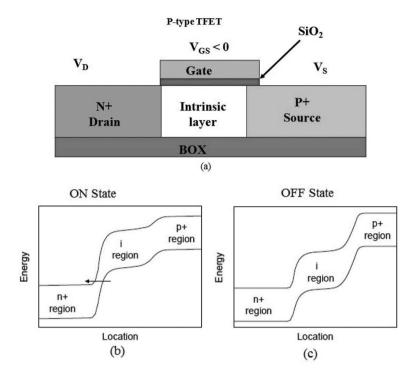

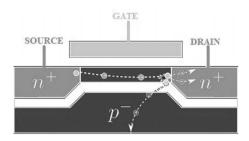

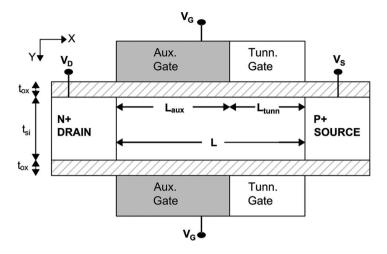

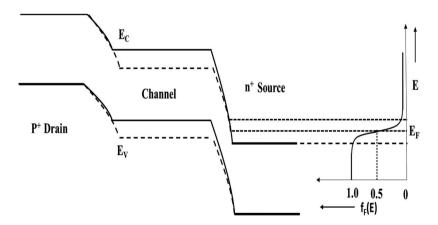

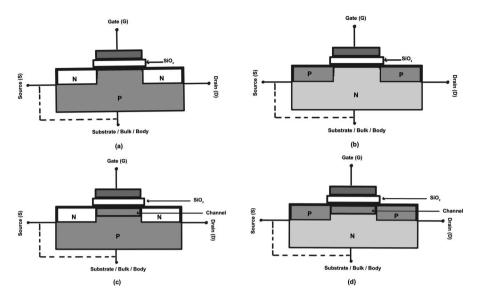

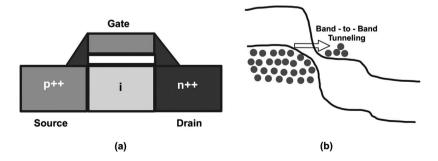

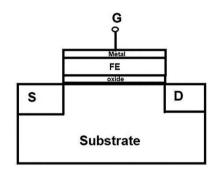

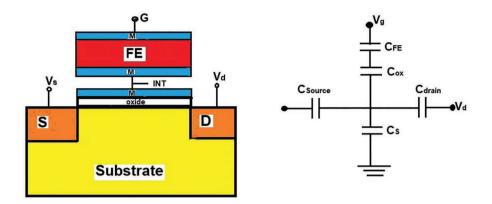

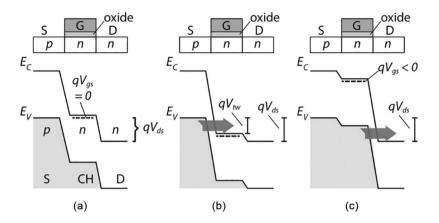

To replace MOSFET in low-power applications, TFET is being recognized as one of the most promising technologies. An N-type TFET schematic design is presented in Figure 2.2a. The p-i-n structure is reverse-biased, and a voltage is provided to the gate to turn the device on. There are p-type and n-type areas that are heavily doped at the source and the drain of the transistor. Intermediate channels consist of an intrinsic layer moderately doped [4]. Rather than using titanium dioxide (TiO<sub>2</sub>) as a gate dielectric, SiO<sub>2</sub> is used. If a positive or negative voltage is connected to the gate terminal  $V_{GS}$ , the device functions as an N-type tunnel FET or a P-type tunnel FET. An N-TFET can be used with positive gate voltage, and a P-TFET can be used without it when a negative gate voltage is applied. As the gate voltage is increased, the energy barrier between the source and the intrinsic region is lowered, allowing for the n-type TFET to operate. A downward force is exerted on the intrinsic energy bands, as seen in Figure 2.2b.

**FIGURE 2.2** (a) N-type tunnel FET device structure. (b) ON state with a positive bias on the gate leading to N-TFET-type behavior. (c) OFF state where the only current is from p-i-n leakage.

Tunneling from one band to another is known as band-to-band (BTB) tunneling. This is followed by electron migration in the direction of an n<sup>+</sup>-doped drain region. Electrons move to the n<sup>+</sup>-doped drain area as a result of drift diffusion. Alternatively, the p-i-n diode leakage current (less than 1 fA/µm) flows between them when the source/drain voltage of the n-TFET is turned off ( $V_{GS}$ =0). Figure 2.2c illustrates the OFF state n-TFET energy barrier diagram (c).

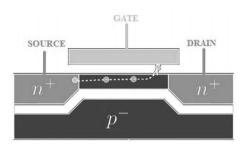

The energy barrier between the drain and the intrinsic region is reduced when the negative gate voltage ( $V_{GS} < 0$ ) is increased in a p-type TFET as shown in Figure 2.3a. It is clear from Figure 2.3b that energy barrier bands in the intrinsic area under the gate have been pushed up. Band-to-band tunneling occurs between the intrinsic band and the n<sup>+</sup>-region conduction band, generating the ON current. A p-tunnel FET is switched OFF ( $V_{GS}=0$ ), as shown in Figure 2.3c, and the leakage current flows between the drain and source regions.

#### 2.3.1 COMPONENTS OF TUNNEL FET

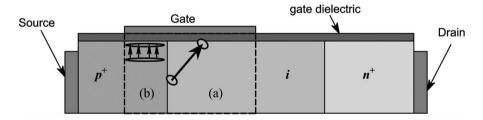

The TFET device's operating concept relies on gate-controlled BTBT. As a result of line tunneling, BTBT occurs in a direction orthogonal to the gate, whereas the channel area is used for BTBT tunneling [5,6]. Figure 2.4 illustrates the two different

**FIGURE 2.3** (a) P-type tunnel FET device structure. (b) ON state with a positive bias on the gate leading to P-TFET-type behavior. (c) OFF state where the only current is from p-i-n leakage.

**FIGURE 2.4** Illustration of (a) point tunneling contribution and (b) line tunneling contribution in a TFET with the gate over the source.

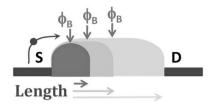

components of tunneling. Source-channel interface point tunneling is also known as lateral tunneling. Increasing the positive gate voltage results in a depletion zone that changes the channel potential profile. From the drain, a small amount of charge will flow into the channel. The source region is heavily doped and closely linked to the gate edge in order for BTB tunneling from the p+ source area to the channel region in order to improve the ON current. This is because dielectric thickness and band-gap width are important factors in determining the ON current in point tunneling. As a result of the source's excessive doping, a portion of the source's region overlaps

FIGURE 2.5 Constant field scaling of digital MOS circuits.

the gate region. Tunneling occurs in the p+ source region as a result. It starts in the valence band and tunnels to the gate dielectric, where it continues to tunnel [7]. As the gate voltage rises, the tunneling continues in the conduction band at the gate dielectric interface. For example, a longer gate overlap over the source allows for a larger line tunneling current, which in turn allows for a greater tunneling current.

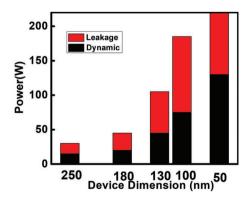

## 2.3.2 SCALING OF MOSFET

Robert Dennard established a set of scaling principles for MOSFETs in 1974, based on his experience in the field. Dennard's rules of thumb have been used to guide the scaling of MOSFETs. A dynamic and static rise in the thickness of a PC's power control is depicted in Figure 2.5. Since supply voltage continues to fall and static power usage increases, power control thickness is increased. It was Dennard's law that the supply voltage scaled according to the voltage necessary to produce a sufficiently high drive current [8,9]. Decreased voltages caused a linear drop in OFF state current ( $I_{off}$ ) and threshold voltage.

## 2.4 SHORT-CHANNEL EFFECTS

To begin, FET dimensions are scaled by maintaining the device aspect ratio. A gadget's dynamic vertical element is defined as a ratio between the gateway length and the gadget's dynamic vertical element. In MOSFETs, the vertical measurement indicates the oxide thickness  $t_{ox}$ , the source and channel intersection  $t_{channel}$ , and the exhaustion profundities  $W_s$  and  $W_d$  at the source and channel intersection [10]. Small-channel conduct is characterized by a low aspect ratio.

FIGURE 2.6 DIBL structure of MOS transistor.

## 2.4.1 DRAIN-INDUCED BARRIER LOWERING

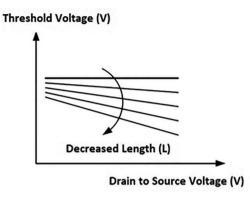

As shown in Figure 2.6, threshold voltage is a measure of the quality of the barrier against the infusion of charge carriers from source to channel.  $L < L_{min}$  short-channel systems with drain channel bias may be able to overcome this obstacle [11]. As the Vt of n-channel MOSFETs is lowered, the subthreshold current increases as  $V_{DS}$  is increased.

## 2.4.2 CHANNEL-LENGTH MODULATION

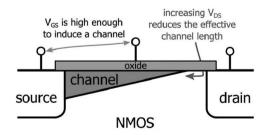

When the drain channel–source bias of a FET advances near the drain channel saturation zone, an area of high electric field is framed close to the drain channel, and the electron speed in this locality is saturated (in long gadgets, we would rather have a pinch-off where  $N_s$  turns out to be slightly close to the drain area). In the saturation zone, the length L of the high-electric-field area increases toward the source with increasing  $V_{DS}$ , and the MOSFET continues to function as though the effective channel length has been shortened by L [12]. This is termed channel-length modulation (CLM), as seen in Figure 2.7.

## 2.4.3 HOT CARRIER EFFECTS

Impacts of hot carriers on FET measurements in deep submicrometer systems are a major problem. Stable voltage scaling, or decreasing the channel length while maintaining high-control supply levels, causes the electric field characteristics in the channel to increase, forcing the charge carriers to accelerate and warm up, as illustrated in Figure 2.8. For example, impact ionization leads to the development of

FIGURE 2.7 Illustration of channel-length modulation.

FIGURE 2.8 Illustration of impact ionization.

FIGURE 2.9 Illustration of hot electrons.

interface states and entering currents generated by hot-electron discharge over the interface boundary, whereas charge carrier tunneling results in oxide charges, and electron–hole recombination causes photocurrents, as shown in Figure 2.9.

## 2.4.4 VELOCITY SATURATION

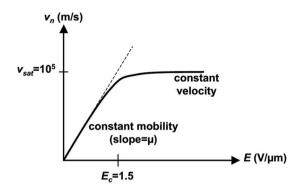

There is a tendency for charge carriers to slow down in high electric fields because of the mobility immersion that occurs when the field is high. To maintain the same electric fields in a shrunk transistor, a constant field scaling can be used [13]. Nevertheless, the scaling trend adopted in semiconductor manufacturing is not a field-wide one. In Figure 2.10, for example, the oxide thickness is scaled up and the supply voltages are scaled back. This results in a larger electric field in the nanoscale MOSFETs as a result of the increased current flow. As the electric field expands, the speed increases. This would have been a low-centrality issue if the immersion that occurs at channel voltages was higher [14,15].

## 2.4.5 GATE OXIDE LEAKAGE

As far as MOSFET devices are concerned,  $SiO_2$  is a good insulator. However, when the gateway oxide's thickness is reduced to below 3 or 2 nm, the possibility of device tunneling increases, leading to an increased oxide overflow current in either case. Using a high-K dielectric can alleviate this problem by minimizing the direct tunneling excess of current [16].

FIGURE 2.10 Illustration of velocity saturation effect.

## 2.5 NONCLASSICAL MOSFET STRUCTURES

Because of technological breakthroughs in process innovation, the basic structure of MOSFET devices has evolved throughout the years, although the fundamental structure has remained constant for some time. Bulk MOSFETs have altered in the drain channel and substrate design, leading to the depicted designs.

- i. Lightly Doped Drain (LDD) structure: Using drain channel engineering, particle implantation is utilized to generate a gently doped channel. Thus, the electric field surrounding the channel is reduced in MOS devices and hot-electron-related quality issues are reduced.

- ii. Substrate with a reversible doping pattern: There is a requirement for channel construction in this design in order to reduce the amount of mass punch through and leakage current.

- iii. Structure of the ground plane with a thin coating of silicon: To grasp the properties of a retrograde substrate structure, chemical vapor deposition technique-based nuclear layer innovation of silicon on a mass substrate is substituted for embed innovation [17,18].

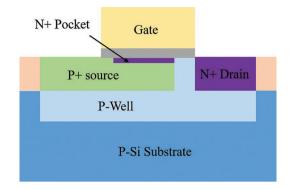

- iv. Halo doping: The DIBL (drain-induced barrier lowering) influence can be reduced by creating a halo-doped pocket near the source and drain channels. A current expansion overflow might result as a result of band-to-band tunneling between the source and drain sides.

## 2.6 ENGINEERING TECHNIQUES

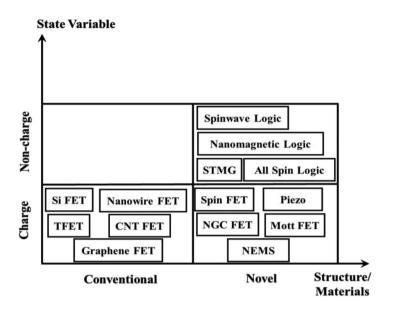

As microelectronics evolved into nanoelectronics, high leakage current and SCEs become a bottleneck to circuit designers. Colinge [19] has investigated a number of nonclassical devices, including double-gate MOSFETs, dual-material-gate MOSFETs, and surrounding-gate MOSFETs. But they face the thermionic limit of subthreshold slope limited to 60 mV/decade, which slowed down supply voltage scaling. Currently, the development of very large-scale integration (VLSI) technology is mostly directed toward the miniaturization of semiconductor devices. Scaling can be

defined as the reduced feature size, which generally leads to better and faster performance and more gate per chip. With the help of scaling, more complex machines have been built with high speed. Nanostructures with high functionality, high device drive, and low power dissipation emerge as a result of device downscaling, which is critical for the advancement of electronics.

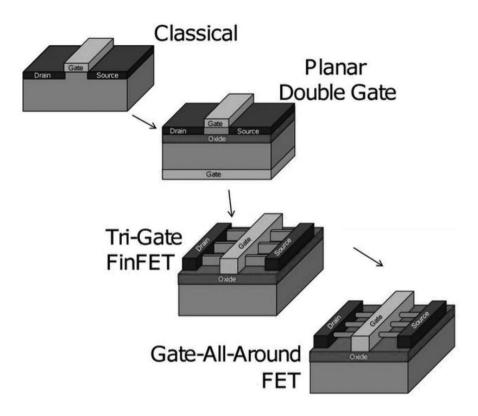

#### 2.6.1 MULTIGATE ARCHITECTURES

The progressing semiconductor industry has greatly revolutionized human lives. Owing to various geometrical scaling issues in a semiconductor device, researchers are taking efforts to put forth new concepts of gate metal work function engineering. The ON state current is greatly improved by combining two or three distinct materials with various work functions in the gate metal. For several decades, planar bulk transistors have been an integral part of ICs, during which the size of these transistors have steadily decreased. Scaling the device dimensions has reached its physical limit and is on the verge of stagnation in various new technologies. The major limitations include undesirable SCEs, subthreshold leakage current, extreme heat dissipation, and power consumption of the device. To surmount all of these shortchannel issues, the best solution can be to increase the electrostatic gate control over the channel. The gate has to be strong in establishing its control over the movement of electrons from source to drain. Therefore, double-, triple-, and surrounding/gateall-around structures have been proposed to effectively suppress the subthreshold conduction and its corresponding leakage current. In general, having more than one gate can enhance the device characteristics, and such a configuration is called multigate device as shown in Figure 2.11.

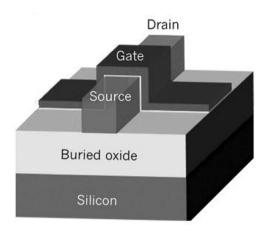

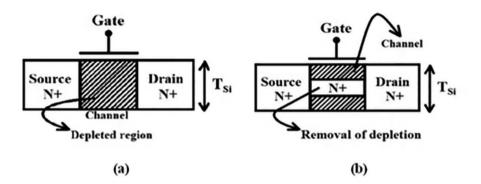

The channel is entirely enclosed by several gates on many surfaces in a multigate device. There is an increase in the ON state current when many gates are used. With this structure, higher gain and transconductance ratio is achieved. Higher transconductance increases the electron generation efficiency and reduces the static power dissipation of the device. Improved mobility and reduced SCEs may be seen in Figure 2.12 using the double-gate (DG) MOSFET with top and bottom gates. For lightly doped devices, the subthreshold slope of DG MOSFET is less [20]. The front and back gates are biased separately providing more drive current. The gate electrode is highly successful at controlling the channel voltage; therefore, leakage current is kept to a minimum.

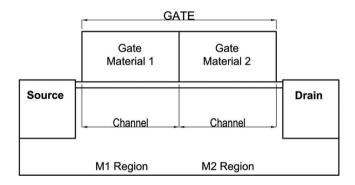

In triple-gate (TG) MOSFET, the channel is surrounded by the gate material on three sides as shown in Figure 2.13. As the number of gates increases, the electric field from the lateral and vertical side exerts more control on the top and bottom side of the channel. With this, the subthreshold swing of the transistor can be increased. Gate metal work function engineering is used in a variety of gate topologies to improve the overall performance of the device. The ON state current can be dramatically improved in gate metal engineering by combining two or three materials with varying work functions.

Figure 2.14 shows how the gate metals M1 and M2 are positioned with relation to the source and drain ends, respectively. The work function of the gate metals on

FIGURE 2.11 Various multigate configurations.

FIGURE 2.12 Schematic view of a double-gate MOS transistor.

either side of the source and drain is different. The drain end gate metal has a lower peak electric field near the drain because it has a smaller work function. As a result, many SCEs will be reduced.

FIGURE 2.13 Schematic view of a trigate FET.

FIGURE 2.14 Structure of a dual-material-gate (DMG) FET.

Figure 2.15 shows how gate metal engineering and multigate architectures have been employed to construct new device structures. Both the top and bottom gates of the DMG DG TFET, as seen in the figure, include materials with distinct work functions. It is possible to obtain substantial performance in terms of minimal sub-threshold swing if the source and drain gate materials have adequate work functions.

Figure 2.16 shows how a binary metal alloy gate with a continuous horizontal fluctuation of mole fraction in a MOS structure incorporates the new notion of work function engineering.

#### 2.6.2 GATE OXIDE ENGINEERING

Gate oxide is the most significant element in designing short-channel transistors. The study of metal oxide semiconductor (MOS) breakdown and most of the short-channel issues begin with the gate oxide material. Gate oxide/gate dielectric region is the most fragile region as it has become extremely thin due to scaling. Downscaling

FIGURE 2.15 Schematic cross-sectional view of DM-DG TFET.

FIGURE 2.16 Schematic cross-sectional view of cylindrical MOSFET.

the thickness of gate oxide creates numerous problems such as hot carrier effect, subthreshold conduction, and threshold voltage roll-off. These issues make the device more susceptible to subthreshold leakage current and high dissipation of heat, and ultimately, this leads to the breakdown of the device. The present state of the art of the semiconductor industry is to utilize alternate gate dielectric materials and heterogate dielectric layers to enhance the device reliability.

## 2.6.3 HIGH-K GATE DIELECTRICS

Many years ago, silicon dioxide was the preferred gate oxide material  $(SiO_2)$ . Silicon dioxide has been steadily thickened to improve the driving current by shrinking transistors owing to gate oxide scaling. A high-K gate dielectric material can be used

to increase gate capacitance by substituting silicon dioxide. As a result of this, certain dielectric materials have higher permittivity than silicon dioxide. Since high-K gate dielectric materials are used, the industry has "electric charge-holding capacity" [21]. Titanium oxide ( $TiO_2$ ) has a greater dielectric constant, which increases the ratio of transconductance and drain current. An increase in carrier generation efficiency in the channel area has been achieved by replacing standard gate dielectric material (silicon dioxide,  $SiO_2$ ) with high-K gate dielectric material. Smaller oxide thicknesses and high-K gate dielectric materials are used to remove the effect of the drain on the source side. Higher substrate doping and extremely efficient gate oxide materials are used to increase the current drive in FETs.

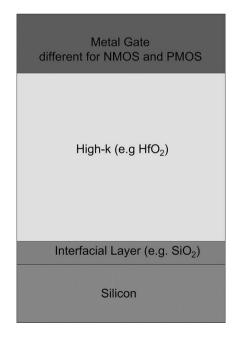

#### 2.6.4 STACKED GATE OXIDE STRUCTURE

The gate has increased electrostatic control over the channel when using high-K gate dielectric material. The only drawback in using high-K gate dielectric material is its imperfect expression due to the occurrence of interface traps, fixed bulk charges, and phase stability issues. Also, replacing  $SiO_2$  with high-K gate dielectrics may result in difficulties in oxidizing other dielectric materials. Oxidation of silicon dioxide is direct and easier, as  $SiO_2$  is a native oxide of silicon. But the oxidation of high-K materials involves a different oxidation process; hence, a novel approach of gate stack architecture is proposed. It is also known as a heterodielectric gate stack. Any high-K dielectric material may be generated by oxidation on top of the standard silicon dioxide, illustrated in Figure 2.17, as the foundation material. In the stacked

FIGURE 2.17 Gate stack architecture.

gate design, an ultrathin low-K interlayer is used in conjunction with a high-K layer to enhance device stability. Device properties may be affected because of the higher electrical focus on the low-K dielectric layer due to continuous displacement of the low-K dielectric layer by the fringing fields.

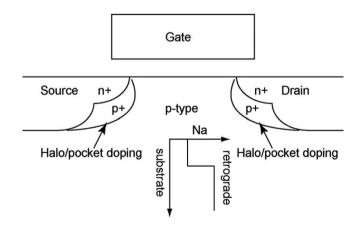

#### 2.6.5 CHANNEL ENGINEERING

SCEs can also be reduced using the channel engineering technique. This includes halo doping and nonuniform channel profiles in a lateral direction. Using this approach, the threshold voltage's dependency on the channel length may be reduced. There are asymmetrical and symmetrical implants at the source or drain. There are two types of halo implants: vertical and slanted. A gate pattern is generally finalized before adding them. As a result, the implants provide a greater barrier between source drain junctions and the channel. The threshold voltage reduction in miniaturized transistors is the commonly known notification of the SCEs. This unfavorable roll-off effect is possibly the most frightening roadblock in the upcoming MOSFET design. On the other hand, for channel lengths below 50 nm, DG MOSFETs still show evidence of considerable leakage currents. To overcome these SCEs, different channel engineering techniques have been deployed [22]. To reduce the threshold voltage roll-off effects, lateral channel engineering has been used to increase the doping concentration in the channel at source/drain junctions. Figure 2.18 shows the halo-implanted MOSFET channel area. The channel length is designated as L, and L is expanded as shown in equation (2.1)

$$L = L_{halo} + L_{channel} \tag{2.1}$$

where  $L_{halo}$  is the length of the halo-implanted and heavily doped channel region and  $L_{channel}$  is the lightly doped channel region.

$$N_{halo} = N_{channel} + \Delta_N \tag{2.2}$$

FIGURE 2.18 Halo-implanted MOSFET channel.

where  $N_{halo}$  is the doping concentration of the halo region,  $N_{channel}$  is the doping concentration of the channel, and  $\Delta_N$  is the difference in the channel doping measured in cm<sup>2</sup>.

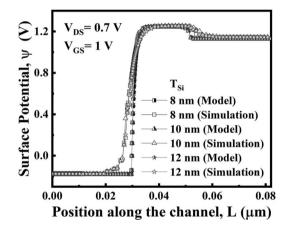

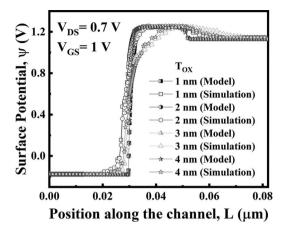

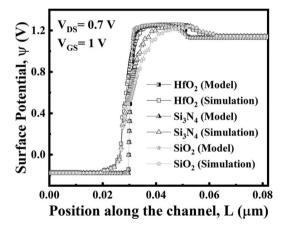

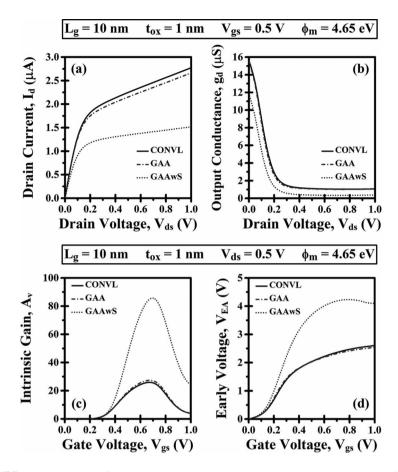

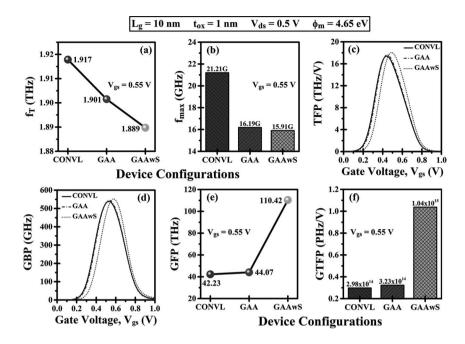

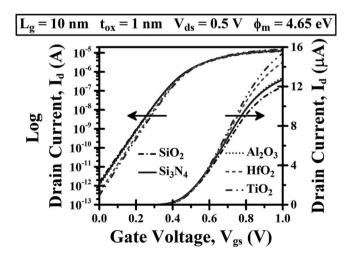

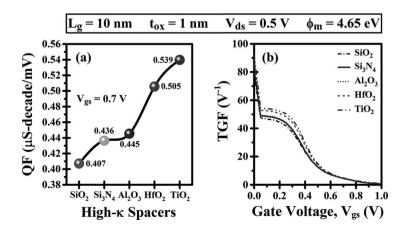

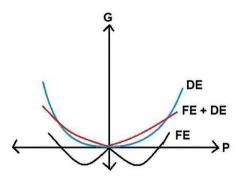

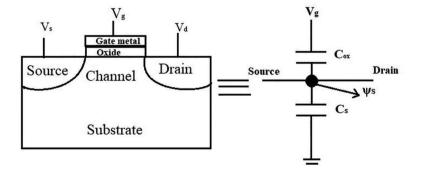

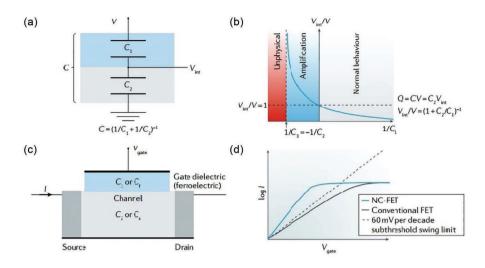

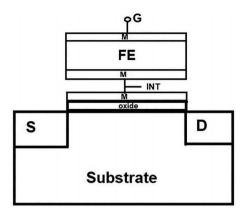

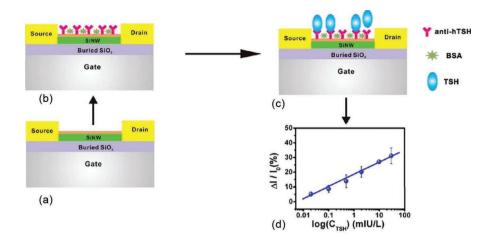

## 2.7 MODELING TECHNIQUES OF LOW-POWER DEVICES