MATERIALS, DEVICES, AND CIRCUITS: DESIGN AND RELIABILITY

## DEVICE CIRCUIT CO-DESIGN ISSUES IN FETs

### EDITED BY SHUBHAM TAYAL BILLEL SMAANI SHIROMANI BALMUKUND RAHI SAMIR LABIOD ZEINAB RAMEZANI

# Device Circuit Co-Design Issues in FETs

This book provides an overview of emerging semiconductor devices and their applications in electronic circuits, which form the foundation of electronic devices. *Device Circuit Co-Design Issues in FETs* provides readers with a better understanding of the ever-growing field of low-power electronic devices and their applications in the wireless, biosensing, and circuit domains. The book brings researchers and engineers from various disciplines of the VLSI domain together to tackle the emerging challenges in the field of engineering and applications of advanced low-power devices in an effort to improve the performance of these technologies. The chapters examine the challenges and scope of FinFET device circuits, 3D FETs, and advanced FET for circuit applications. The book also discusses low-power memory design, neuromorphic computing, and issues related to thermal reliability. The authors provide a good understanding of device physics and circuits, and discuss transistors based on the new channel/dielectric materials and device architectures to achieve low-power dissipation and ultra-high switching speeds to fulfill the requirements of the semiconductor industry.

This book is intended for students, researchers, and professionals in the field of semiconductor devices and nanodevices, as well as those working on device-circuit co-design issues.

#### Materials, Devices, and Circuits: Design and Reliability

Series Editor: Shubham Tayal, K. K. Paliwal, Amit Kumar Jainy

#### **Tunneling Field Effect Transistors**

Design, Modeling and Applications Edited by T.S. Arun Samuel, Young Suh Song, Shubham Tayal, P. Vimala and Shiromani Balmukund Rahi

#### Quantum-Dot Cellular Automata Circuits for Nanocomputing Applications

Edited by Trailokya Sasamal, Hari Mohan Gaur, Ashutosh Kumar Singh, Xiaoqing Wen

#### **Device Circuit Co-Design Issues in FETs**

Edited by Shubham Tayal, Billel Smaani, Shiromani Balmukund Rahi, Samir Labiod and Zeinab Ramezani

For more information about this series, please visit: https://www.routledge.com/Materials-Devices-and-Circuits/book-series/MDCDR#

# Device Circuit Co-Design Issues in FETs

Edited by Shubham Tayal, Billel Smaani, Shiromani Balmukund Rahi, Samir Labiod and Zeinab Ramezani

CRC Press is an imprint of the Taylor & Francis Group, an informa business

Designed cover image: © Shutterstock

First edition published 2024 by CRC Press 6000 Broken Sound Parkway NW, Suite 300, Boca Raton, FL 33487-2742

and by CRC Press 4 Park Square, Milton Park, Abingdon, Oxon, OX14 4RN

#### CRC Press is an imprint of Taylor & Francis Group, LLC

© 2024 selection and editorial matter, Shubham Tayal, Billel Smaani, Shiromani Balmukund Rahi, Samir Labiod and Zeinab Ramezani; individual chapters, the contributors

Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, access www.copyright.com or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. For works that are not available on CCC please contact mpkbookspermissions@tandf.co.uk

Trademark notice: Product or corporate names may be trademarks or registered trademarks and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Names: Tayal, Shubham, editor. | Smaani, Billel, editor. | Rahi, Shiromani Balmukund, editor. | Labiod, Samir, 1981- editor. | Ramezani, Zeinab, editor. Title: Device circuit co-design issues in FETs / edited by Shubham Tayal, Billel Smaani, Shiromani Balmukund Rahi, Samir Labiod and Zeinab Ramezani. Other titles: Device circuit co-design issues in field-effect transistors Description: Boca Raton : CRC Press, 2024. | Series: Materials, devices, and circuits | Includes bibliographical references and index. Identifiers: LCCN 2023007962 (print) | LCCN 2023007963 (ebook) | ISBN 9781032414256 (hardback) | ISBN 9781032416823 (paperback) | ISBN 9781003359234 (ebook) Subjects: LCSH: Field-effect transistors. | Electronic circuit design. | Semiconductors. Classification: LCC TK7871.95 .D48 2024 (print) | LCC TK7871.95 (ebook) | DDC 621.3815/284--dc23/eng/20230503 LC record available at https://lccn.loc.gov/2023007963

ISBN: 9781032414256 (hbk) ISBN: 9781032416823 (pbk) ISBN: 9781003359234 (ebk)

#### DOI: 10.1201/9781003359234

Typeset in Times by Deanta Global Publishing Services, Chennai, India

## Contents

| Editor biogr |                                                                                                                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1    | Modeling for CMOS circuit design1<br>Husien Salama, Alain Tshipamba, and Khalifa Ahmed                                                                                          |

| Chapter 2    | Conventional CMOS circuit design                                                                                                                                                |

|              | Samir Labiod, Abdelmalek Mouatsi, Zakaria Hadef, and Billel<br>Smaani                                                                                                           |

| Chapter 3    | Compact modeling of junctionless gate-all-around MOSFET for circuit simulation: Scope and challenges                                                                            |

|              | Billel Smaani, Fares Nafa, Abhishek Kumar Upadhyay,<br>Samir Labiod, Shiromani Balmukund Rahi,<br>Mohamed Salah Benlatreche, Hamza Akroum,<br>Maya Lakhdara, and Ramakant Yadav |

| Chapter 4    | Novel gate-overlap tunnel FETs for superior analog, digital, and ternary logic circuit applications                                                                             |

|              | Simhadri Hariprasad, Ramakant Yadav, and Surya Shankar Dan                                                                                                                      |

| Chapter 5    | Phase transition materials for low-power electronics                                                                                                                            |

| Chapter 6    | Impact of total ionizing dose effect on SOI-FinFET with spacer engineering                                                                                                      |

|              | Abhishek Ray, Alok Naugarhiya, and Guru Prasad Mishra                                                                                                                           |

| Chapter 7    | Scope and challenges with nanosheet FET-based circuit design 161<br>Atefeh Rahimifar and Zeinab Ramezani                                                                        |

| Chapter 8    | Scope with TFET-based circuit and system design 181<br>P. Suveetha Dhanaselvam, B. Karthikeyan, P. Vanitha, and P. Anand                                                        |

| Chapter 9  | An overview of FinFET-based capacitorless 1T-DRAM 189                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------|

|            | Mitali Rathi and Guru Prasad Mishra                                                                                   |

| Chapter 10 | Literature review of the SRAM circuit design challenges                                                               |

|            | Ismahan Mahdi, Yasmine Guerbai, Yassine Meraihi, and<br>Bouchra Nadji                                                 |

| Chapter 11 | Challenges and future scope of gate-all-around (GAA)<br>transistors: Physical insights of device-circuit interactions |

|            | Shobhit Srivastava and Abhishek Acharya                                                                               |

| Index      |                                                                                                                       |

## Preface

Our daily lifestyle is a witness to the importance of CMOS science and technology. CMOS changes our daily life. Nearly all modern industries and other cutting-edge developments including artificial intelligence (AI), autonomous systems, 5G communications, and quantum computing rely on it. The world population's use of electronics, communications, computers, and information technology (IT) applications has increased dramatically in recent years. Users can easily be identified in most places in our daily activities. Mobile technology is the best example of its applications. Scaling is the main and most important feature of CMOS devices. This feature of CMOS devices has continuously helped to develop various types of circuits and systems for our daily life uses, medical sciences, aerospace, and military-based development over the past four decades. Only due to the scaling of conventional MOSFET, various types of circuits and systems have developed for mankind's better life. The journey of scaling MOSFET technology is continuous and has reached the 5 nm range.

Scaling of the CMOS channel length below 0.5 u/m and increasing chip density to the VLSI range has placed power dissipation on an equal footing with performance as a figure of merit in digital circuit design. Portability and reliability have also played a major role in the emergence of low-power, low-voltage, digital circuits, and system designs. In this regard, the need to extend the battery life, have inexpensive packaging and cooling systems, and reduce the weight and size of the equipment have been the driving forces. The demand for low-power and high-speed FET devices has grown exponentially to meet the requirements of these applications. FETs are the leading electronics technology and will continue to advance in future CMOS. MOSFET has played a leading role in the development of VLSI circuits and systems. This device was a basic building block of CMOS technology and, as a consequence, the predominant device of integrated circuits and system development. The demand for small, portable, and affordable electronic equipment is growing by the day. In order to satisfy consumer demand, researchers are constantly searching for new semiconductor devices. This book, Device Circuit Co-Design Issues in FETs, provides industry professionals and beginners with an overview of emerging semiconductor devices and their applications in VLSI circuits and systems. The goal of this book is to provide readers with a better understanding of the ever-growing field of low-power electronic devices and their applications.

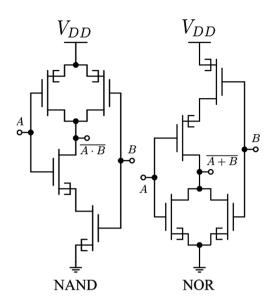

Through detailed derivations, discussions, layout, and simulation examples, Chapter 1 provides a concise summary of the thought process and practical implementation of CMOS IC design for the reader. The foundation of all digital designs is the inverter. Designing increasingly complex structures like NAND gates, adders, multipliers, and microprocessors becomes significantly easier once their operations and attributes are thoroughly understood. By extrapolating the conclusions found for inverters, it is possible to extract the electrical behaviors of these intricate circuits almost entirely. Inverter analysis is frequently expanded to explain the operations of more complicated gates, such as NAND, NOR, or XOR, which serve as the basis for components like multipliers and processors. The static CMOS inverter, also known as the CMOS inverter, is the only iteration of the inverter gate on which this chapter focuses. The inverter, NAND, and NOR gates are implemented and simulated using the LT-spice computer-aided design (CAD) tool. Similar to other CAD tools, this method can be used to simulate more complex circuits by combining or altering these fundamental elements.

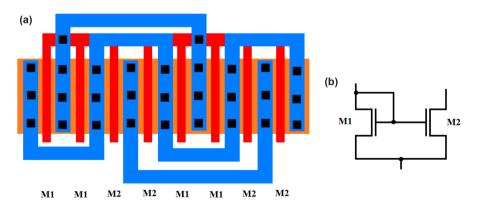

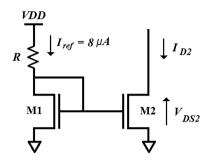

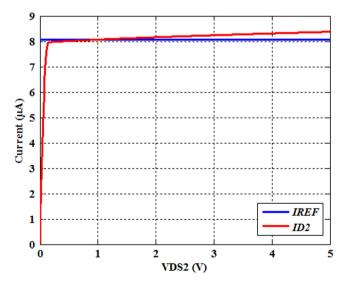

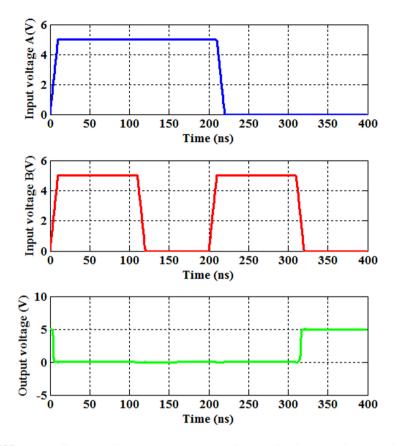

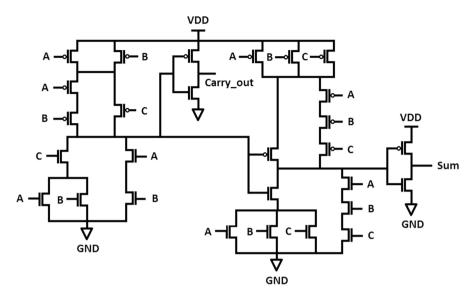

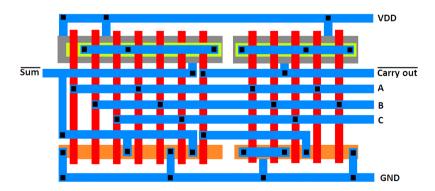

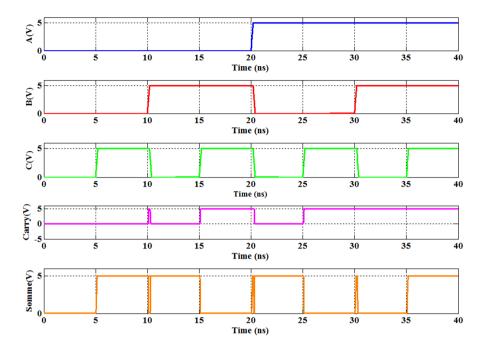

The design and simulation of CMOS integrated circuits are covered in Chapter 2. Beginning with a brief overview of CMOS process integration, this section focuses on interconnects, providing information on propagation delay and simulating certain parasitic effects. In the chapter, some fundamental understanding concepts for the analog design, layout techniques, and simulation of current mirror are presented. Moreover, DC characteristics and dynamic behavior have been analyzed. In addition to this, the layout of the basic CMOS static logic gates (inverter, NAND, and NOR) and arithmetic functions such as the full adder are presented. SPICE simulations have been performed on both 50 nm (short-channel) and 1  $\mu$ m (long-channel) technologies.

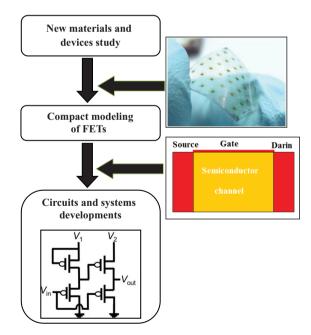

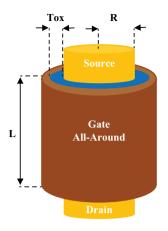

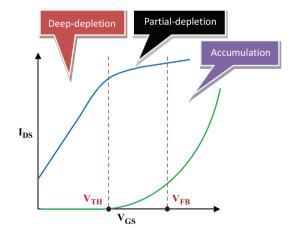

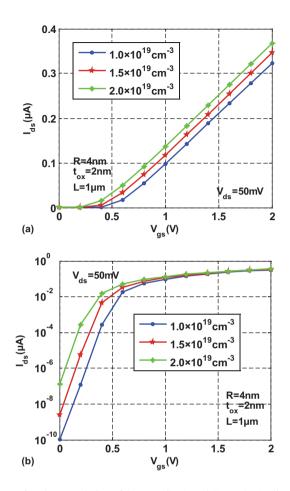

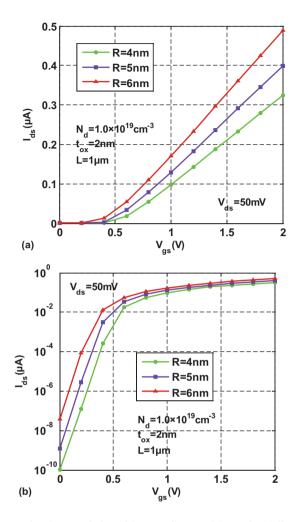

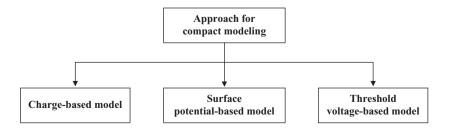

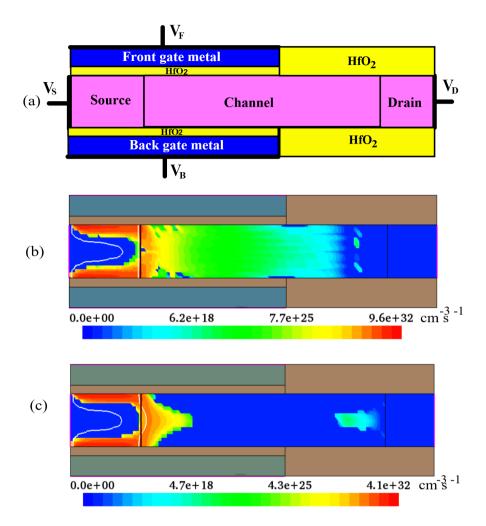

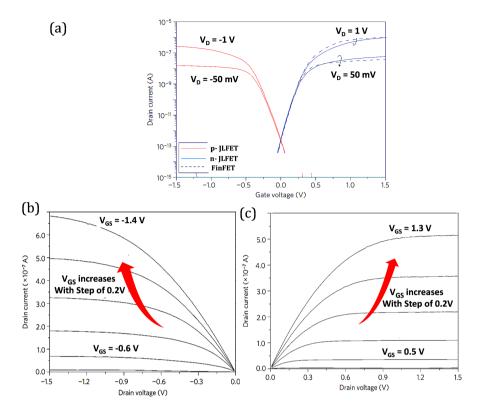

The existing limitations of conventional CMOS technology are presented in Chapter 3. Conventional CMOS technology has reached its physical and technological limits, according to semiconductor experts, and as a result, numerous fieldeffect transistor (FET) architectures have been developed. The junctionless (JL) gate-all-around (GAA) MOSFET has attracted a great deal of research interest. In addition, compact models of FETs need to be incorporated into circuit simulators using a hardware description language (HDL), such as VHDL and Verilog-A. This is for the potential use of emerging transistors in various integrated circuits. The compact modeling of JL GAA MOSFET as an important issue is addressed here. The chapter begins with a discussion of the characteristics of compact models for the development of new electronic systems and applications. The value of hardware description language for the design and simulation of circuits is then demonstrated. In addition to the theoretical basis and main approach for developing compact models of JL GAA MOSFET, the charge-based, surface-potential-based, and thresholdvoltage-based models are also presented. The most significant compact models are surface-potential-based and charge-based, specially dedicated to circuit simulation and design. Furthermore, the challenges of compact modeling of JL GAA MOSFET are also discussed.

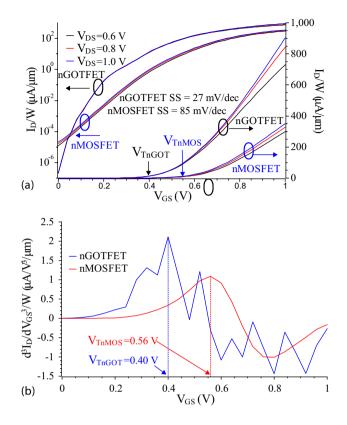

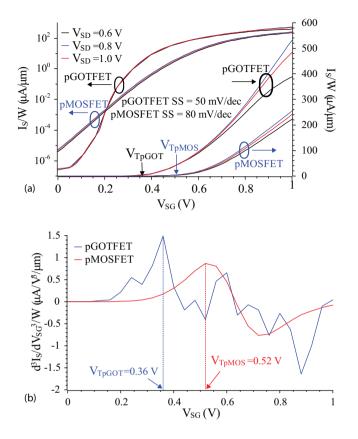

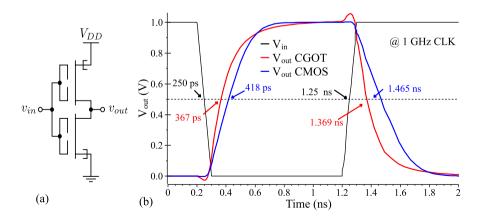

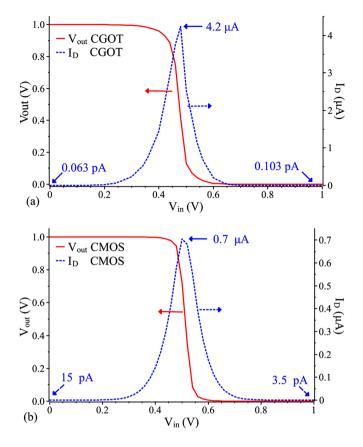

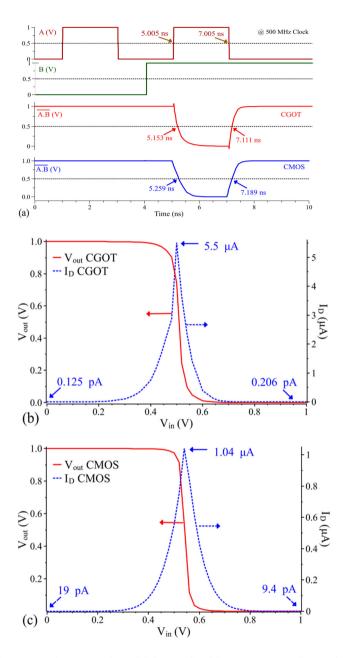

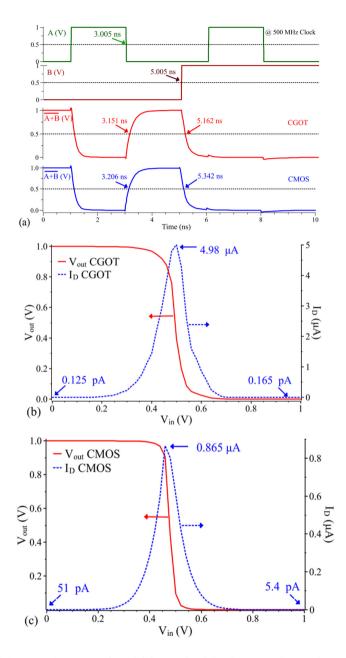

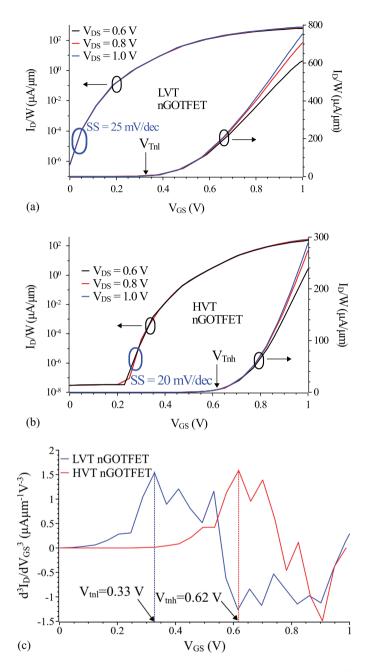

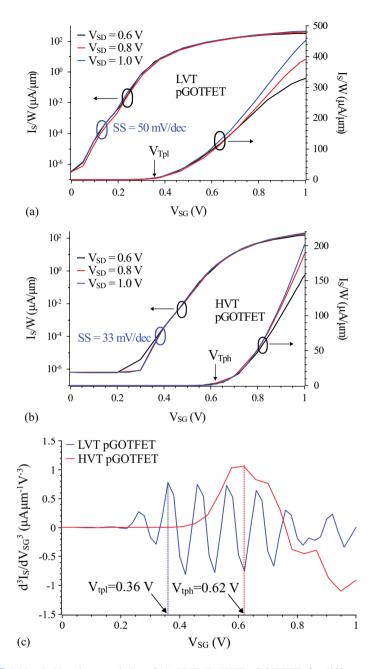

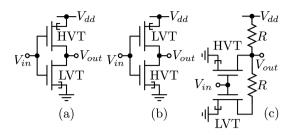

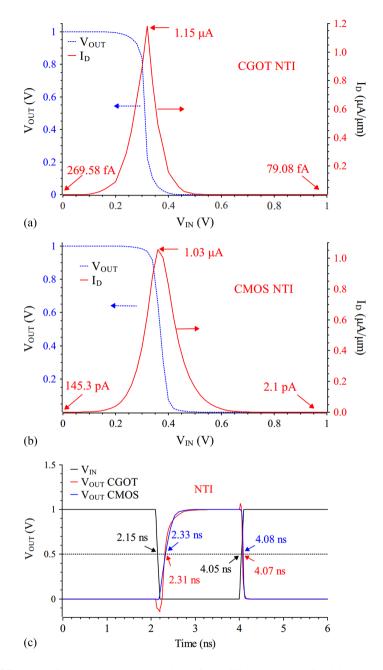

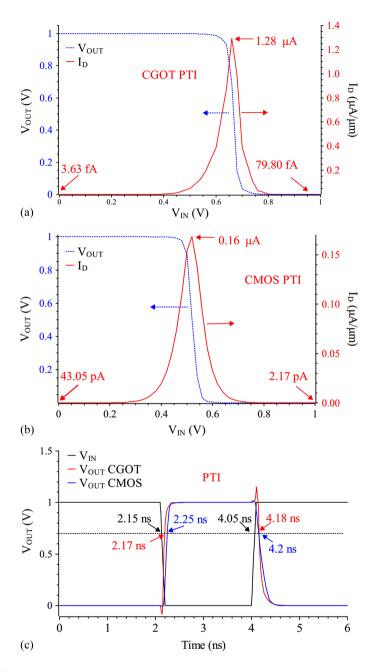

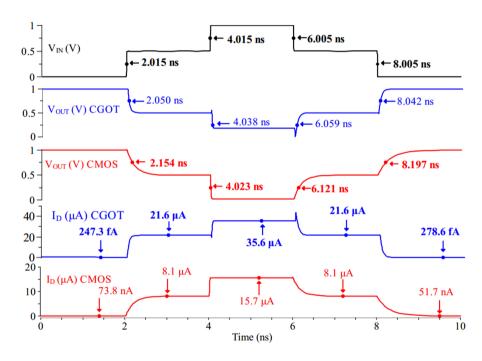

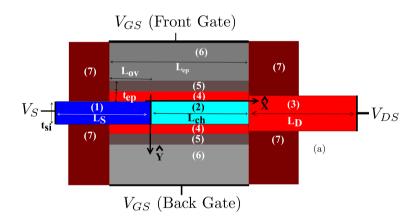

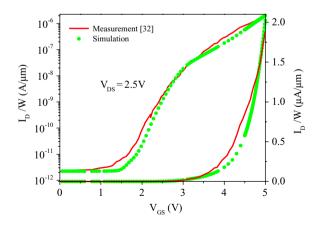

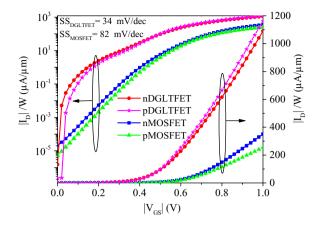

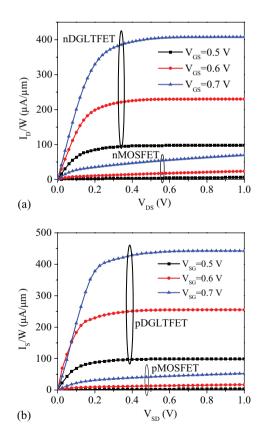

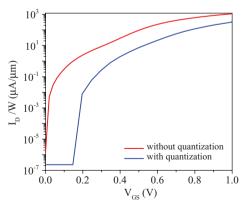

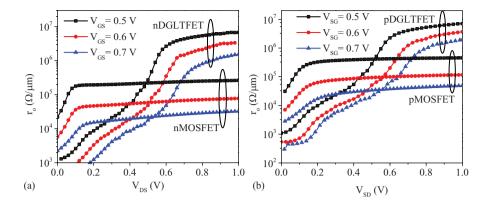

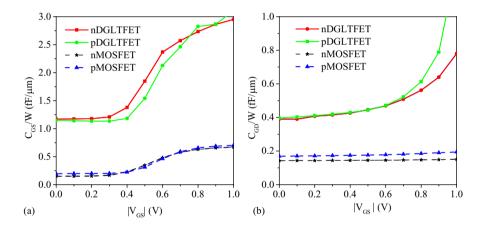

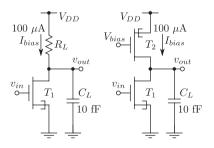

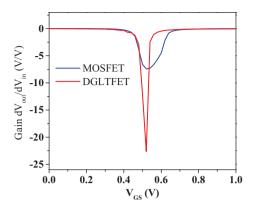

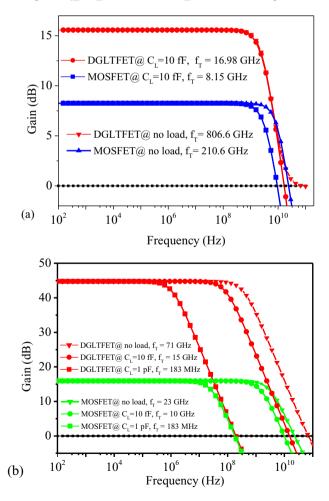

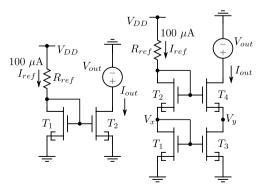

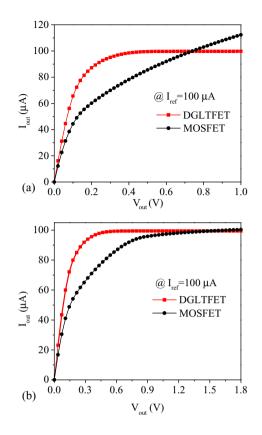

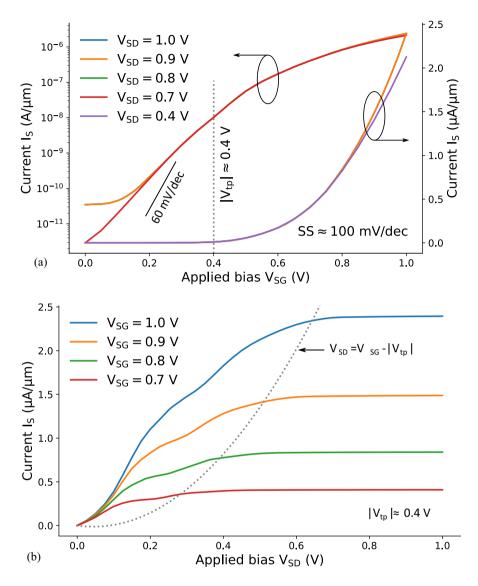

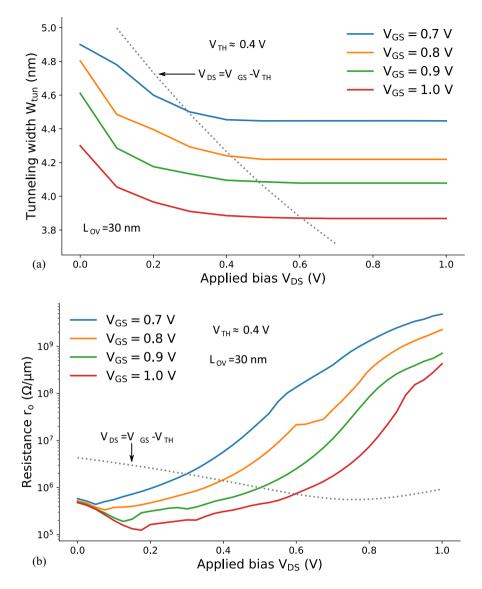

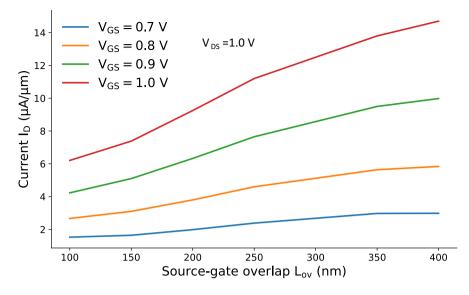

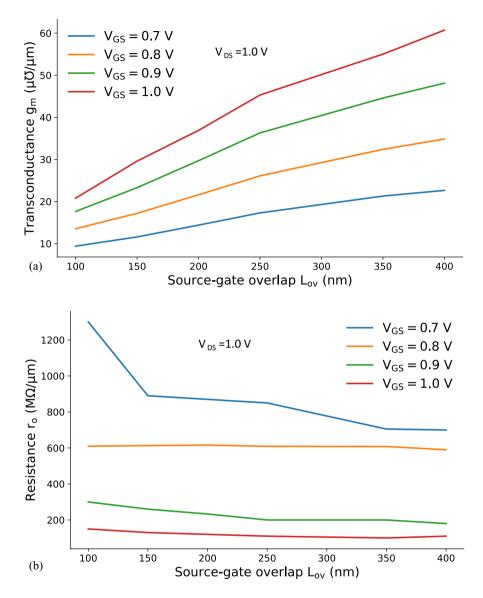

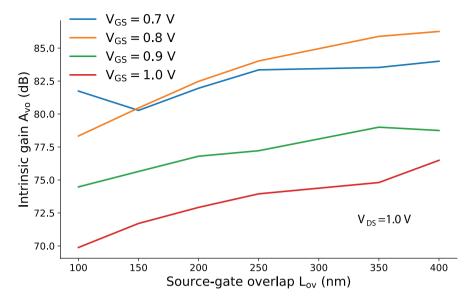

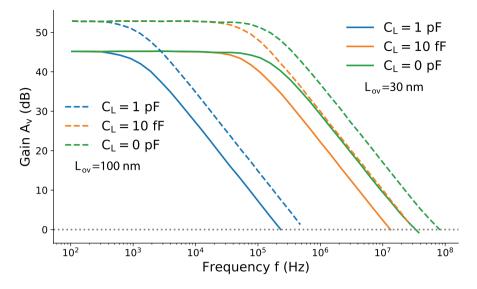

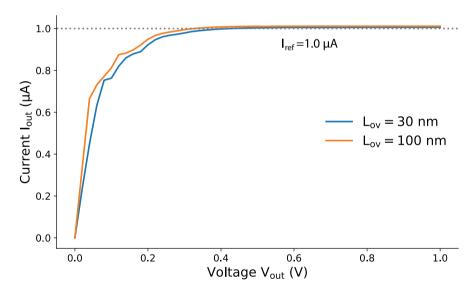

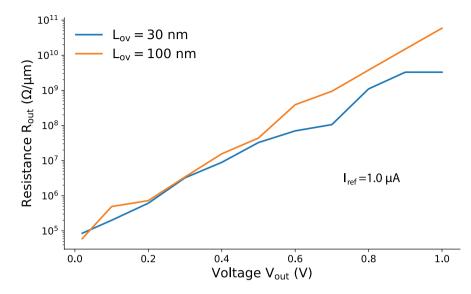

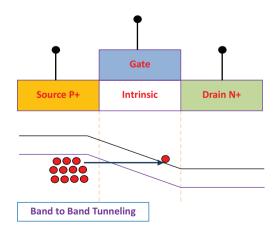

Chapter 4 presents different variations of the novel gate-overlap tunnel field-effect transistors (GOTFETs) and their applications in analog, digital, and ternary logic circuits. For benchmarking their device and circuit performance with the industry-standard 45 nm CMOS technology, the presented GOTFETs have an effective channel length of 45 nm, commensurate with the technology node. These devices have a higher band-to-band generation rate than the conventional TFET devices, due to the gate fully overlapping on the source side, resulting in excellent improvement in the  $I_{on}$  levels while maintaining very low  $I_{off}$ . Introduction of an epi-layer between the source and oxide layers, the proposed variant of GOTFET, the line TFET (LTFET), exhibits almost flat drain current saturation characteristics, leading to very high  $R_{out}$

for superior analog circuit applications. Optimization of the LTFET device has been done by changing critical parameters such as epi-thickness, gate-to-source overlap, and doping concentration, and has shown its influence on analog performance. Therefore, the proposed LTFET has a two-order improvement in  $r_a$  leading to a twoorder improvement in the intrinsic gain  $A_{vo}$  over the MOSFET. Due to lower connection, smaller chip footprint, and faster-operating speeds, the GOTFET structure has been further modified for ternary logic circuit applications. The intended LVT and HVT GOTFET shave been designed such that low threshold voltage  $V_{TI} \approx V_{DD}/3$ and high threshold voltage  $V_{TH} \approx 2V_{DD}/3$  for the unique voltage levels  $\{0-V_{DD}/3\}$ ,  $\{V_{DD}/3-2V_{DD}/3\}, \{2V_{DD}/3-V_{DD}\}$  correspond to ternary logic states 0, 1, and 2. The proposed LVT and HVT TFET devices will be the starting point for all applications involving ternary logic. This chapter is, in essence, a comprehensive review of the GOTFET devices and their circuits performance, such that the readers of this book chapter will learn about specialized TFETs (GOTFETs), which perform much better than conventional CMOS when switched on while consuming less power than conventional TFETs when switched off. Consequently, complementary GOTFET (or CGOT) technology combines the robustness and high performance of CMOS with the low-power benefits of TFET in a single-device technology.

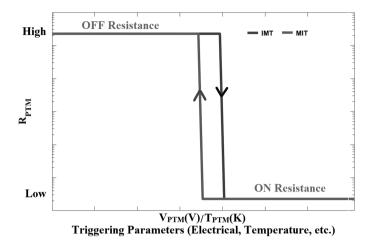

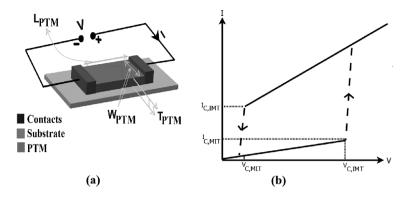

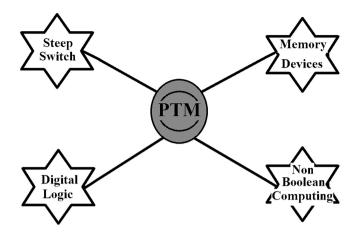

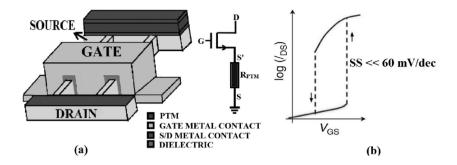

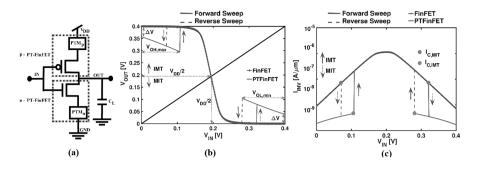

Chapter 5 is devoted to the few years when the development of ultra-low-power oxide electronics devices has been facilitated by abrupt, ultrafast, nanoscale switching caused by an insulator-to-metal transition in phase transition materials. These transitions, particularly those caused by electrical triggering, aid in the achievement of dimensional scaling at the lower technology node. The unique electrical properties of these materials can be used to create innovative devices and circuits for next-generation electronics. This chapter examines the history of the phase transition materials family, including its origin, history, modeling, and application in cutting-edge devices. There is a focus on various applications of phase transition materials in low-power electronics, such as steep switching devices, digital circuits, memory, and non-Boolean computing.

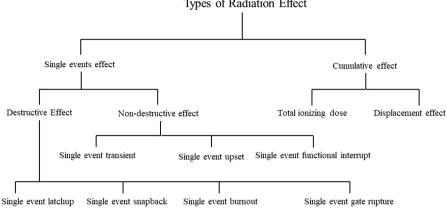

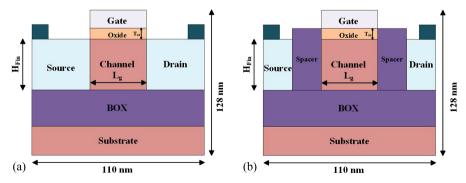

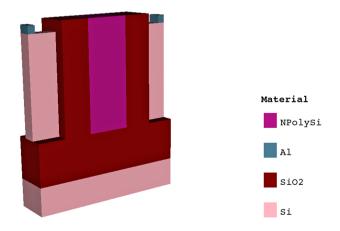

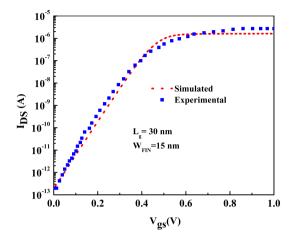

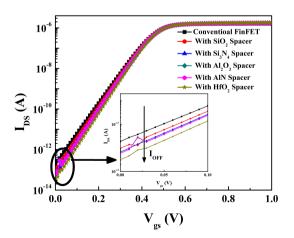

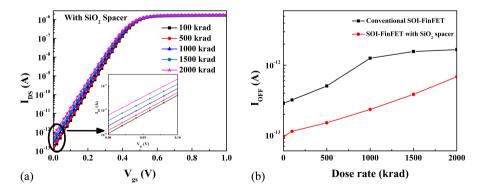

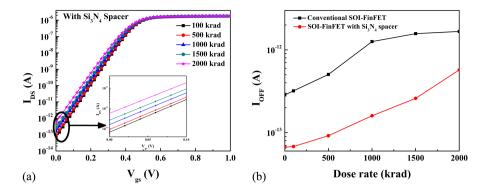

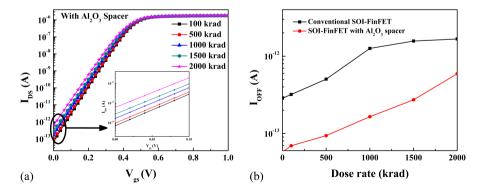

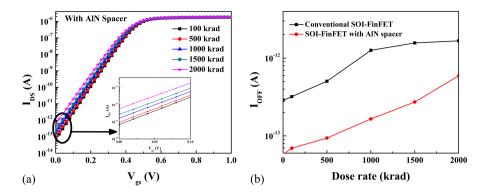

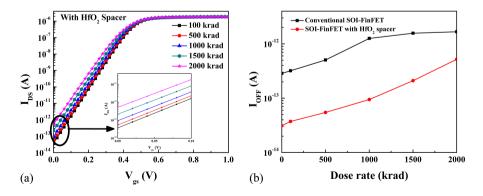

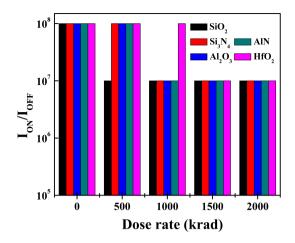

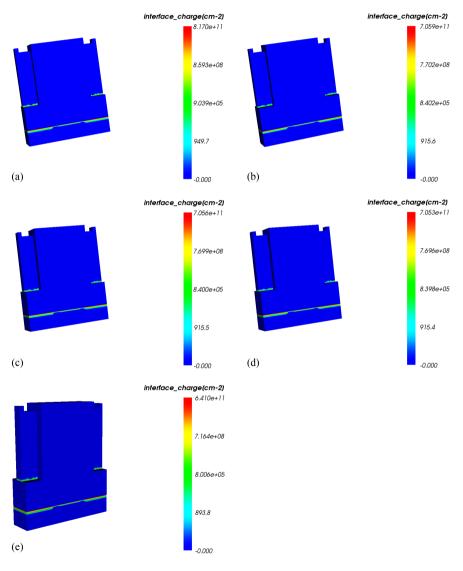

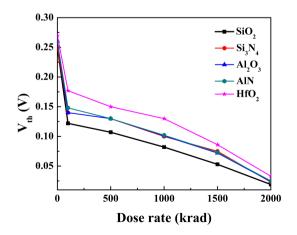

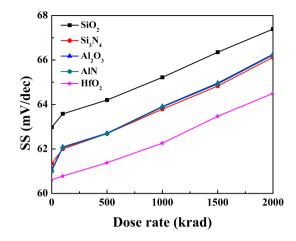

Chapter 6 describes the extensive use of semiconductor devices in the electronic systems of satellites. In the outer atmosphere, natural radiation is the major threat to semiconductor devices. The radiation raises there liability issues of these types of devices when the irradiation accumulation of trap charges is found in the oxides and semiconductor/insulator interfaces. These trap charges are well capable of shifting the threshold voltage towards negative and increasing the leakage current. The radiation effects are classified into two categories: total ionizing dose (TID) effects and single event effects (SEEs). The impact of TID on SOI-FinFET with the spacer technique is investigated. At a higher radiation dose of 2000 krad, the high-k dielectric (HfO<sub>2</sub>) spacer maintains lower leakage current and positive threshold voltage. The proposed engineering technique enhances the OFF-state device performance after and before the irradiation of the device. For the pre-radiation condition, a 48% improvement in OFF-state current (I<sub>OFF</sub>) is observed for the SiO<sub>2</sub> spacer-based device and an 83% improvement is obtained for the HfO<sub>2</sub> spacer. The HfO<sub>2</sub> spacerbased device shows 4.2%, 2.6%, 2.5%, and 2.4% lower subthreshold swing (SS) after the 2000 krad dose as compared to SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, and AlN, respectively. An improvement of 23% in  $I_{OFF}$  and a 42% lower shift in threshold voltage is observed for the HfO<sub>2</sub> spacer SOI-FinFET as compared to SiO<sub>2</sub> spacer-based SOI-FinFET. This investigation shows that SOI-FinFET with HfO<sub>2</sub> spacer-based device is best suited for electronic systems in space applications.

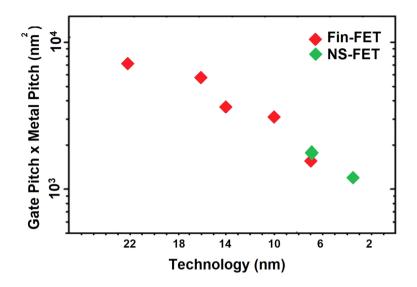

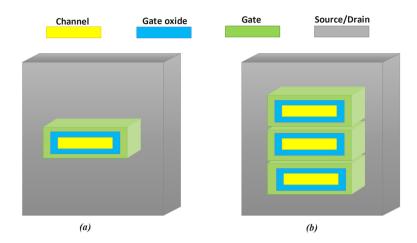

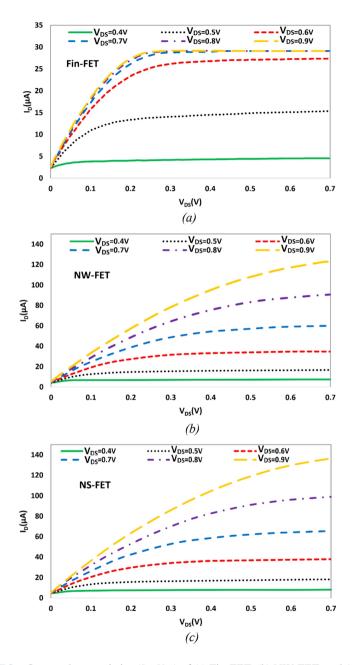

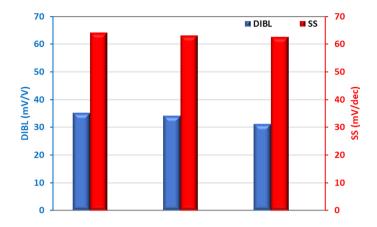

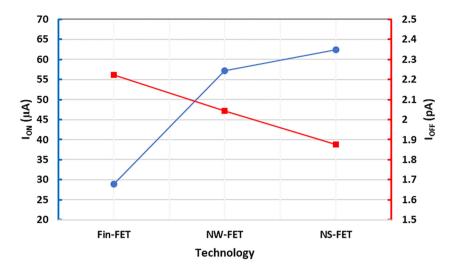

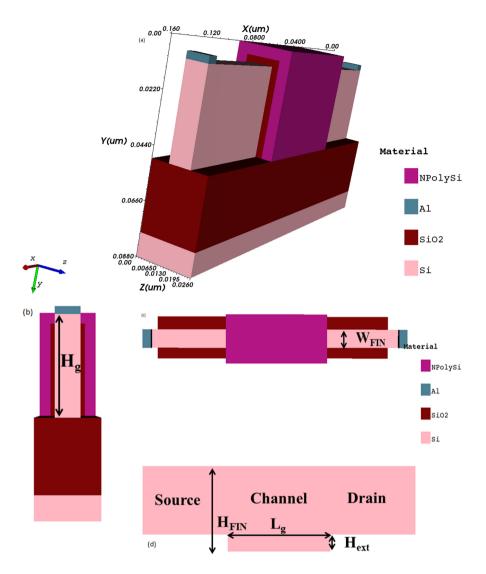

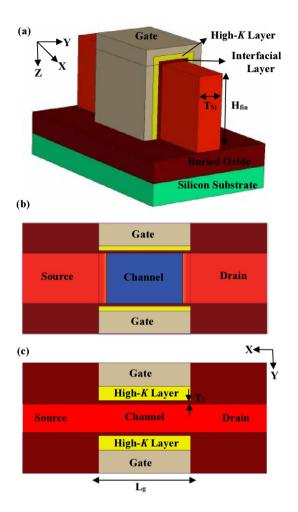

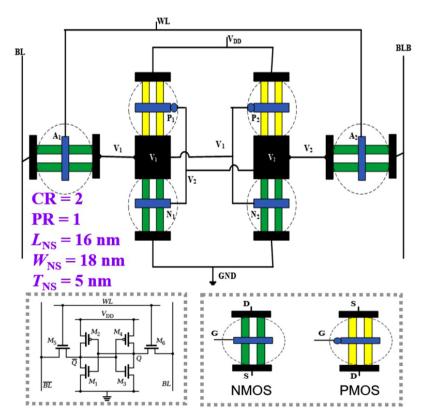

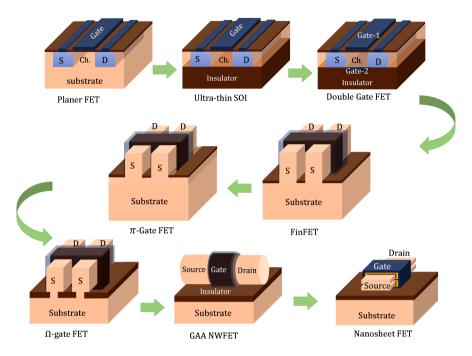

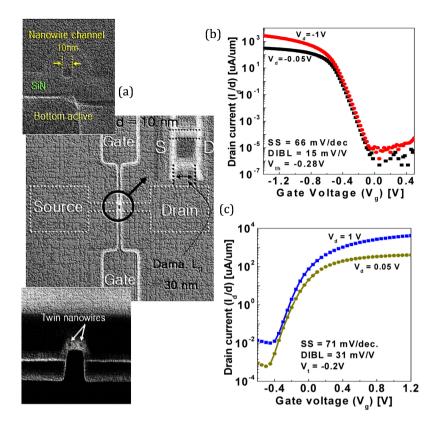

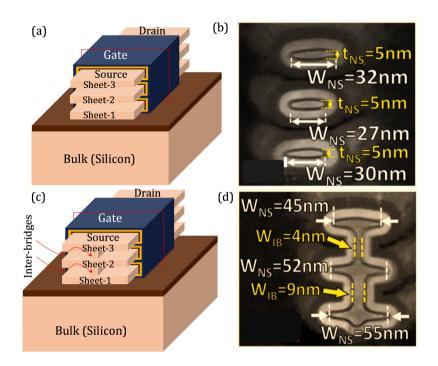

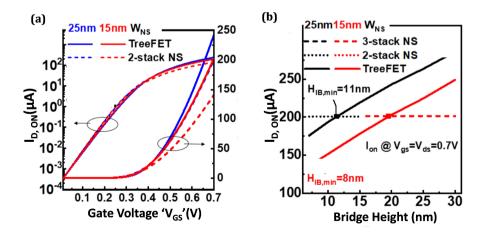

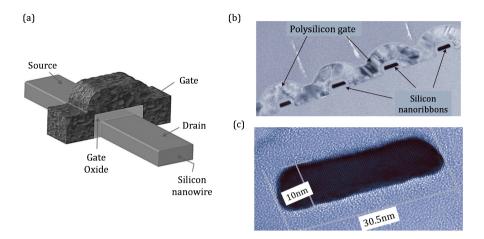

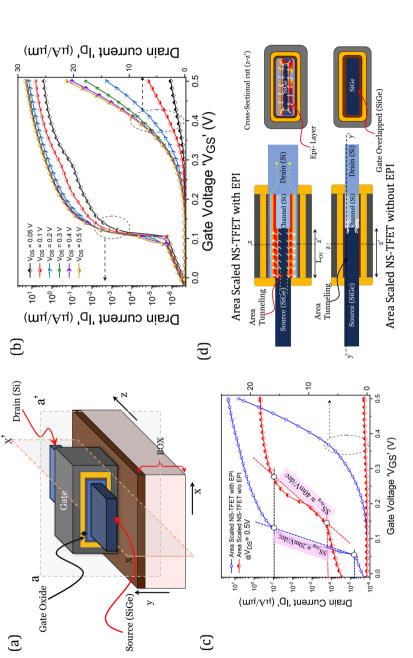

Chapter 7 is dedicated to the rapid development of technology that has increased the density, speed, and performance of transistors embedded in modern chips. According to the presented literature, FinFET technology down to 7 nm has shown more acceptable performance than others. However, further scaling down to 5 and 3 nm scales imposes undeniable challenges to this technology. Thus, the community of semiconductor designers, in order to introduce a suitable alternative to FinFET, proposed the technology of nanosheet FET (NSFET) to overcome these challenges. Fundamentally NSFET is an advanced version of FinFET. The prominent feature of the NSFET is having a horizontal gate stacked around the channel in all directions. This feature gives the gate more control over the channel. Therefore, it significantly improves the performance and ON current of the NSFET compared to other FETs. This has made the NSFET more popular than other devices, especially for scaling down to 3 nm. On the other hand, the successful fabrication of NSFET by Samsung/ IBM for sub-7-nm technology has pushed the semiconductor industry towards these devices. In this regard, to deal with the performance of NSFET in integrated circuits, it is of particular importance to investigate the electrical characteristics of these devices from the perspective of the circuit. In this chapter of the book, NSFET is introduced, and two key challenges of nanodevices, the self-heating and short channel effects, are investigated. Subsequently, in more detail, the behavior and challenges of this device have been analyzed from the circuit point of view.

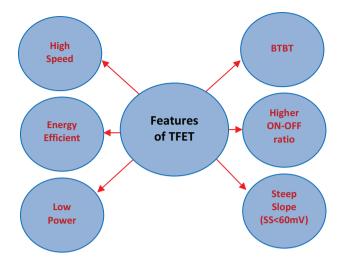

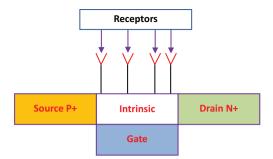

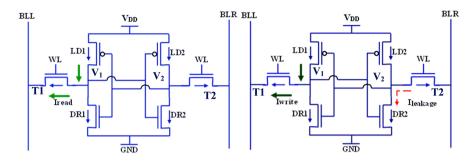

In Chapter 8, the authors provided a brief introduction to tunneling FET. Tunneling FET surpasses the subthreshold swing limitation and off-state current issues of conventional CMOS devices. The structure of TFET, its characteristics, and its scope with specific applications are discussed in this chapter. This will be useful for researchers who have just started their research on TFET. Only certain applications are explored in this chapter. Still, there are many more applications in the research to explore.

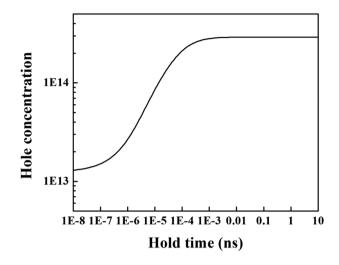

In Chapter 9, the demand for memory is increasing day by day, and the downscaling of conventional 1T-1C DRAM in sub-10 nm technology is becoming a topic of concern. The fabrication and scalability of 3-D cell storage capacitors are extremely difficult. To overcome this issue, the concept of capacitorless 1T-DRAM is introduced. The silicon-on-insulator (SOI) transistor will store the charges in the floating body of the metal oxide semiconductor field-effect transistor (MOSFET) by impact ionization. Further scaling of MOSFET devices is approaching its boundary, and it is giving rise to short-channel effects. Hence multi-gate transistors (such as FinFET, GAA FET, and RFET), in which more than one gate surrounds the channel are introduced. In this chapter, FinFET-based capacitorless 1T-DRAM is introduced, due to its simplicity in fabrication. In FinFET, the gate controls the channel from three sides; hence the electrostatic control over the channel increases and the leakage current also reduces. Preface

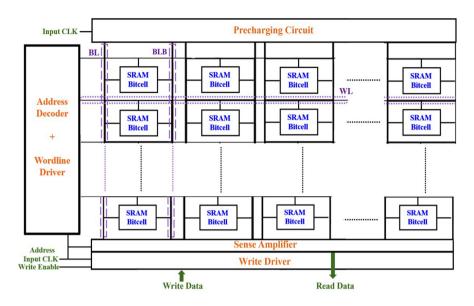

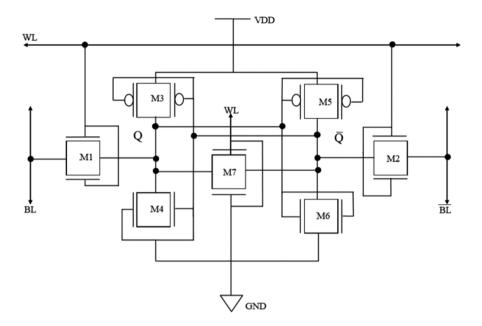

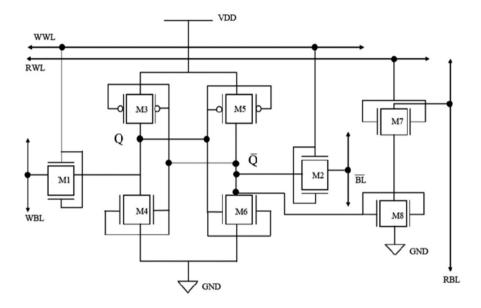

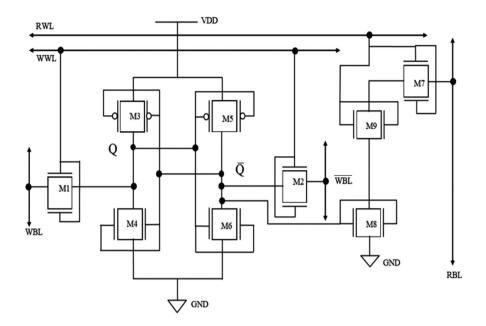

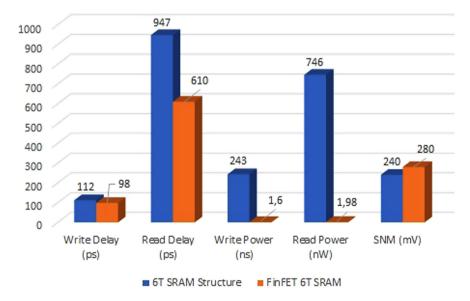

In Chapter 10, the majority of current embedded systems use microprocessors equipped with volatile cache memory based on static random access memory (SRAM) technology. As part of a core computing component, its performance is critical and needs to have more attention. Actual systems-on-chips (SoCs) need to be more performant because less than 20% of the globally integrated transistors are used for arithmetic and logic operations, and the rest of the transistors, about 80%, are mostly used for the cache memory. Additionally, modern implantable electronic components and devices, for specific and general use, are based on artificial intelligence (AI) and require efficient and reliable SRAM circuits designed for having enhanced and fast responses to compute-in-memory (CIM). In order to reach desired performances, reliability should be maintained, especially with regard to the most recent technological areas. In this chapter, the authors have cited, for example, embedded systems using low power supplies, which may pose a risk to the stability of the SRAM circuits and also their unavailability. In sophisticated devices, the process variations change the transistor design parameters and consequently the design integrity. Additionally, sensitive information treatment, environmental conditions (such as temperature variation, shocks, and vibration), and static charge emission from adjacent integrated circuits can affect SRAM reliability. Fin field-effect transistor (FinFET) technology has been used to design SRAMs to enhance the overall performance, which takes into account efficiency, power, and area. In this work, we have reviewed various colossal challenges to SRAM design after classifying them into five distinct categories and each one will be presented with viable solutions.

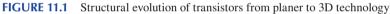

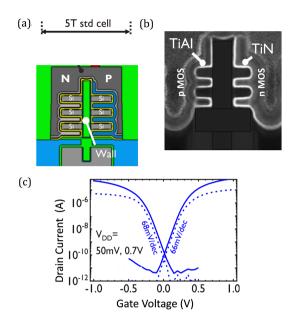

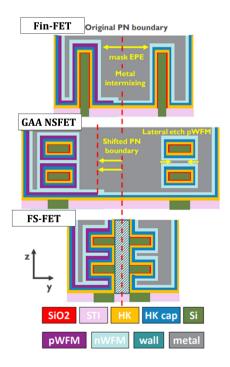

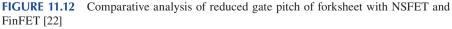

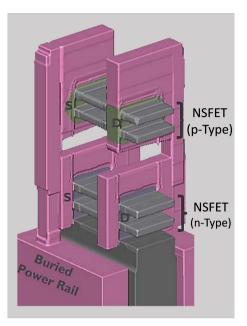

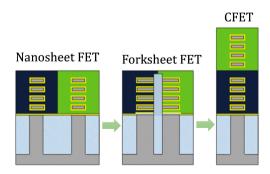

In Chapter 11, FinFET technology is discussed, which is the slogger of today's semiconductor world. However, the demand for further scaling with a desire for ultra-low power and high-speed applications leads to undesired short-channel effects, where new transistors are required for the next generation. Thanks to science and technological innovation, different transistors from the GAA (gate-all-around) FET family and their competitive benefits have been brought together. This chapter tries to answer why and how 3D devices emerge for future computing paradigms. In addition to the limitation of FinFET, it further discusses the scope and challenges of different members of the GAAFET family, such as nanowire FET, nanosheet FET, junctionless nanosheet FET, complementary FET, and forksheet FET.

## **Editor biographies**

**Shubham Tayal** is an assistant professor in the Department of Electronics and Communication Engineering at SR University, Warangal, India. He has more than six years of academic/research experience teaching at undergraduate and postgraduate levels. He received his Ph.D. in microelectronics and VLSI design from the National Institute of Technology, Kurukshetra, M.Tech (VLSI Design) from YMCA University of Science and Technology, Faridabad, and B.Tech (Electronics and Communication Engineering) from MDU, Rohtak.

He has published more than 40 research papers in various international journals and conferences of repute, and many papers are under review. He is on the editorial and reviewer panel of many SCI/SCOPUS-indexed international journals and conferences. He is editor/co-editor of eight books published by CRC Press (Taylor & Francis Group, USA) and Springer Nature. He acted as a keynote speaker and delivered professional talks on various forums. He is a member of various professional bodies including IEEE and IRED. He is on the advisory panel of many international conferences. He is a recipient of the Green ThinkerZ International Distinguished Young Researcher Award 2020. His research interests include the simulation and modeling of multi-gate semiconductor devices, device-circuit co-design in the digital/analog domain, machine learning, and IoT.

**Billel Smaani** received his Ph.D. degree from the University of Frère Mentouri, Constantine, Algeria, in 2015. He joined the Centre Universitaire Abdelhafid Boussouf, Mila, Algeria, in 2021, where he has been an associate professor since June 2022. From 2015 to 2021, he was with the University of M'hamed Bougara Boumerdes, Algeria. His current research interests include the study, analysis, and compact modeling of advanced nanoscale field-effect transistors for analog and digital circuit co-design.

**Shiromani Balmukund Rahi** received a B.Sc. (Physics, Chemistry Mathematics) in 2002, an M.Sc. (Electronics) from Deen Dyal Upadhyaya Gorakhpur University, Gorakhpur, in 2005, M. Tech. (Microelectronics) from Panjab University Chandigarh in 2011, and a Doctorate of Philosophy in 2018 from the Indian Institute of Technology, Kanpur, India. He completed his Master project (M.Sc.) at the Central Electronics Engineering Research Institute (CEERI, 2005), Pilani Rajasthan, under the supervision of Dr. P C Panchariya (Director and Chief Scientist, CEERI, Pilani) and thesis (M. Tech.) under Prof. RenuVig (director and Professor, UIET Panjab University Chandigarh), post-doctoral research (Department of Computer Science, Korea Military Academy, Seoul, Republic of Korea). He has 25 international publications and ten book chapters. He has edited two books for CRC publication. He is associated with research with the Indian Institute of Technology Kanpur, India, and in the electronics department at the University Mostefa Benboulaid of Algeria, developing ultra-low power devices such as tunnel FETs, NC TFET, negative capacitance, and nanosheet FETS.

**Samir Labiod** was born in Constantine, Algeria, on January 5, 1981. He received electrical engineering and magister degrees in electronics from Constantine University, Algeria, in 2005 and 2008, respectively. He also received his Ph.D. from Constantine University Institute of Sciences and Technology, Constantine, Algeria, in 2013. His current research interests include the numerical modeling of electromagnetic compatibility of semiconductor devices.

**Zeinab Ramezani** received her Ph.D. in Electrical and Computer Engineering in 2017. She worked as an assistant professor at IAU University from 2017 to 2019 and as a research scientist at Northeastern University in Boston, MA, USA, from 2019 to 2021. She is a scientist with over ten years of experience in modeling, simulation, and characterization of novel structures; micro-and nanoelectronics; nanotechnology; nanophotonic and nanomagnetic power semiconductor devices; wide bandgap semiconductors; optoelectronic devices; plasmonic devices; and bioelectron-

ics and biosensors. Her current research at the University of Miami, FL, USA, is focused on developing and modeling new materials and electronic tools to enable leapfrog advancements in health applications.

## Contributors

Atefeh Rahimifar Department of Electrical Engineering, Karoon Institute of Higher Education, Ahvaz, Iran

Abdelmalek Mouatsi Boumerdes University, Faculté de Technologie, Laboratoire d'Ingénierie des Sytémes et des Telecommunication, Boumerdes, Algeria

Abhishek Acharya S.V. National Institute of Technology, Surat, India

Abhishek Kumar Upadhyay 3X-FAB Semiconductor Foundries, Erfurt, Germany

Abhishek Ray Department of Electronics and Communication Engineering, National Institute of Technology Raipur, Chhattisgarh, India

Alain Tshipamba University of Connecticut, Storrs, CT, USA

Alok Naugarhiya Department of Electronics and Communication Engineering, National Institute of Technology Raipur, Chhattisgarh, India

**B. Karthikeyan** Velammal College of Engineering and Technology, Madurai, Tamilnadu, India

**Bhaskar Awadhiya** Department of Electronics and Communication, Manipal Institute of Technology, Manipal Academy of Higher Education, Manipal, Udupi, Karnataka, India

Billel Smaani Centre Universitaire Abdel Hafid Boussouf, Mila, Algeria

**Bouchra Nadji** Department of Automation University Mhamed Bougara Boumerdes Algeria

**Fares Nafa** Boumerdes University, Faculté de Technologie, Laboratoire d'Ingénierie des Sytémes et des Telecommunication, Algeria

Guru Prasad Mishra Department of Electronics and Communication Engineering, National Institute of Technology Raipur, Chhattisgarh, India

Hamza Akroum Laboratoire d'Automatique Appliquée, Université M'Hamed Bougara de Boumerdes, Algeria

Husien Salama University of Connecticut, Storrs, CT, USA

Ismahan Mahdi Department of Electrical Systems Engineering, University Mhamed Bougara Boumerdes, Algeria

Khalifa Ahmed University of Turkish Aeronautical Association, Ankara, Turkey

**Maya Lakhdara** Département d'Electronique, Faculté des Sciences et de la Technologie, Laboratoire Hyperfréquences et Semi-conducteurs, Université des frères Mentouri Constantine 1, Constantine, Algeria

**Mitali Rathi** Department of Electronics and Communication Engineering, National Institute of Technology Raipur, Chhattisgarh, India

Mohamed Salah Benlatreche Centre Universitaire Abdelhafid Boussouf, Mila, Algeria

**P. Anand** Velammal College of Engineering and Technology, Madurai, Tamilnadu, India

**P. Suveetha Dhanaselvam** Velammal College of Engineering and Technology, Madurai, Tamilnadu, India

**P.N Kondekar** Department of Electronics and Communication Engineering, PDPM-Indian Institute of Information Technology, Design & Manufacturing, Jabalpur, India

P. Vanitha SRMIST Ramapuram Campus, Chennai, India

Ramakant Yadav Electrical & Electronics Engineering Department, Mahindra University, Hyderabad, India

Sameer Yadav Department of Electronics and Communication Engineering, PDPM-Indian Institute of Information Technology, Design & Manufacturing, Jabalpur, India

Samir Labiod Department of Physics, Faculty of Sciences, Universite 20 Aout 1955, Skikda, Algeria

Shiromani Balmukund Rahi Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur 208016, India

Shobhit Srivastava S.V. National Institute of Technology, Surat, India

Simhadri Hariprasad BITS Pilani, Hyderabad Campus, India

Surya Shankar Dan BITS Pilani, Hyderabad Campus, India

Yasmine Guerbai Department of Electrical Systems Engineering University Mhamed Bougara Boumerdes, Algeria

Yassine Meraihi Department of Electrical Systems Engineering University Mhamed Bougara Boumerdes, Algeria

Zakaria Hadef Department of Physics, Faculty of Sciences, Universite 20 Aout 1955, Skikda, Algeria

Zeinab Ramezani Electrical and Computer Engineering Department, University of Miami, Miami, FL, USA

## 1 Modeling for CMOS circuit design

Husien Salama, Alain Tshipamba, and Khalifa Ahmed

#### CONTENTS

| 1.1  | CMOS    | S devices                                             | 1  |

|------|---------|-------------------------------------------------------|----|

|      | 1.1.1   | Introduction                                          | 1  |

|      | 1.1.2   | Switch of CMOS                                        | 2  |

|      | 1.1.3   | The implementation and operation of the CMOS inverter | 3  |

| 1.2  | The C   | MOS IC design process                                 | 4  |

|      | 1.2.1   | Background                                            | 4  |

|      | 1.2.2   | CMOS inverter characteristics                         |    |

| 1.3  | The lo  | gic circuit of CMOS                                   | 10 |

|      | 1.3.1   |                                                       |    |

|      |         | 1.3.1.1 Overview                                      | 10 |

|      |         | 1.3.1.2 Simulation                                    | 10 |

|      | 1.3.2   | CMOS NAND gate                                        | 12 |

|      |         | 1.3.2.1 Overview                                      | 12 |

|      |         | 1.3.2.2 Simulation                                    | 13 |

|      | 1.3.3   | CMOS NOR gate                                         | 13 |

|      |         | 1.3.3.1 Overview                                      | 13 |

|      |         | 1.3.3.2 Simulation                                    | 15 |

| 1.4  | CMOS    | S technology and applications                         | 15 |

| 1.5  | Layou   | t of CMOS                                             | 16 |

| 1.6  | Conclu  | ision                                                 | 18 |

| Refe | rences. |                                                       | 18 |

#### 1.1 CMOS DEVICES

#### 1.1.1 INTRODUCTION

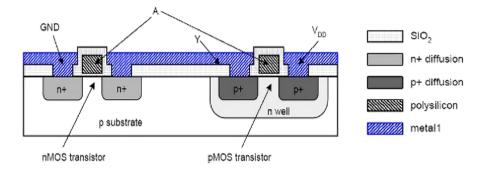

A CMOS transistor consists of a P-channel MOS (PMOS) and an N-channel MOS (NMOS) [1]. The operation of a CMOS device is like other types of field effect transistors (FET) except it depends on an added oxide layer between the gate and the substrate. CMOS are active devices, meaning they require external power sources

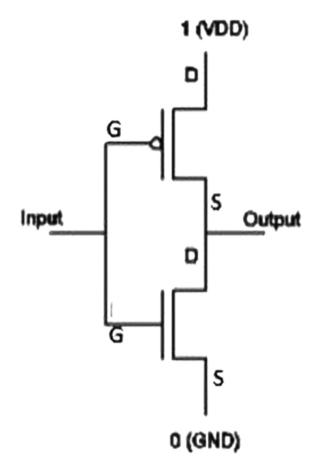

FIGURE 1.1 CMOS (complementary metal oxide semiconductor). [1]

to operate. For this reason, shown in Figure 1.1, CMOS devices are designed with a power supply, input voltage terminal  $(V_{IN})$ , output voltage  $(V_{OUT})$ , gate, drain, and PMOS and NMOS transistors which are connected to the gate and the drain terminals [2].

The main advantage of CMOS over NMOS and PMOS technology is a much smaller power dissipation, which has become a crucial element for scalability in IC design. Unlike NMOS, PMOS, or bipolar circuits, a CMOS circuit has almost no static power dissipation. Power is only barely dissipated if the circuit switches between high and low power levels or states. This superior performance of CMOS technology enables the integration of more CMOS gates on an IC than with NMOS or bipolar technology.

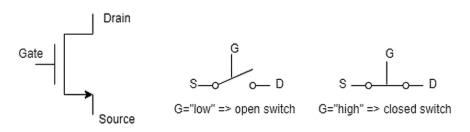

#### **1.1.2** Switch of cmos

In basic CMOS concepts, we see the use of transistors for designing logic gates. The same approach can be used to design other blocks (such as flip-flops or memories). Ideally, a transistor behaves like a switch [3] for logic implementation. For NMOS transistors, if the input is a logic high, the switch is ON; otherwise, it is OFF. On the other hand, for the PMOS, if the input is a logic low the transistor is ON; otherwise, the transistor is OFF [4].

A graphic representation is shown in Figure 1.2.

FIGURE 1.2 MOS as a switch

For the NMOS in Figure 1.1, the gate (G) can be thought of as the switch's handle and the signal flowing through the gate as the force acting on it. Considering an initially inactivated switch, if one does not apply enough force on the switch (i.e., a logic low is applied), then the switch remains open (Figure 1.2 on G = low). However, if sufficient force is applied (i.e., a logic high is acting on the switch), the switch closes (Figure 1.2 on G = "high"), and electric contact is established between the drain (D) and the source (S). The PMOS operates similarly with the main difference being that its activation is a logic low.

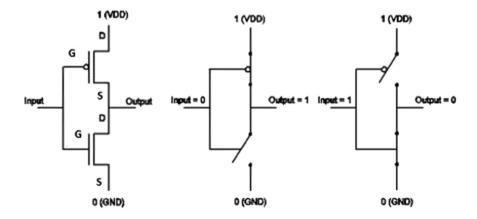

#### 1.1.3 THE IMPLEMENTATION AND OPERATION OF THE CMOS INVERTER

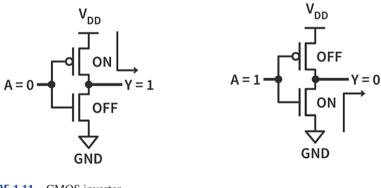

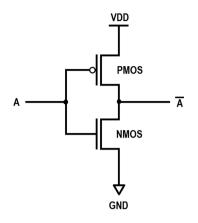

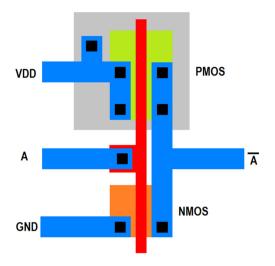

We have seen that a CMOS device is a combination of NMOS and PMOS technology. To understand the basics of operation, we will design a simple inverter gate. Figure 1.3 shows the CMOS implementation of the inverter and how it works for different inputs (1 and 0) [5]. The symbol VDD is the source voltage (or logic 1), and GND is the ground (or logical 0).

The CMOS inverter operation is simple and straightforward. Referring to Figure 1.3, when the low input voltage (0) is given to the CMOS inverter's gate, the PMOS transistor is switched ON, whereas the NMOS transistor is switched OFF. Since the PMOS is connected to VDD, this facilitates the provision of a low resistance path for electrons from VDD to the output through the PMOS, hence the generation of a logic high output for a low input [6].

Similarly, when the high input voltage (1) is given to the CMOS inverter's gate, the PMOS transistor is OFF, whereas the NMOS transistor is now switched ON. Since the NMOS is connected to the ground, this renders the ground a low resistance path for electrons and, consequently, from the output to the ground, hence the generation of a logic low output for a high input voltage [7]. As a result, Figure 1.3 works like an inverter.

FIGURE 1.3 CMOS inverter and switch equivalent [2]

#### 1.2 THE CMOS IC DESIGN PROCESS

The CMOS circuit design process consists of defining circuit inputs and outputs, hand calculations, circuit layout, simulations including parasitic revaluation of circuit inputs and outputs, fabrication, and testing [8]. The circuit specifications are usually set at the beginning of the design and adjusted as the process evolves and matures. This will be the result of trade-offs made between cost and performance, changes within the marketability of the chip, or just changes in the customer's needs. However, in most cases, major changes after the chips have gone into production are impossible [9].

#### 1.2.1 BACKGROUND

The CMOS concept is relatively newer to other semiconductor technologies and was first introduced to the semiconductor community around 1963. The thought that a circuit could be made with discrete complementary MOS devices – an NMOS (N-channel MOSFET) transistor and a PMOS (P-channel) transistor – was quite novel at the time given the immaturity of MOS technology and the rising popularity of the bipolar junction transistor (BJT) as a replacement for the vacuum tube [10].

The inverter circuit shown in Figure 1.4 consists of PMOS and NMOS FET. The input is the gate voltage for both transistors.

#### **1.2.2** Cmos inverter characteristics

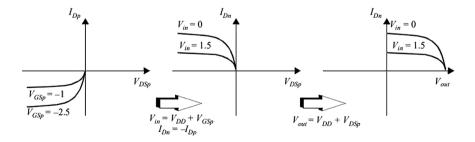

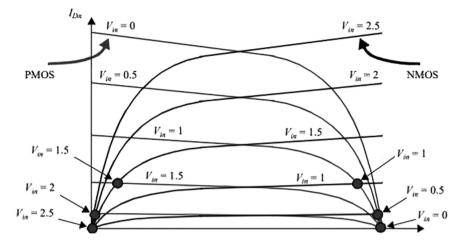

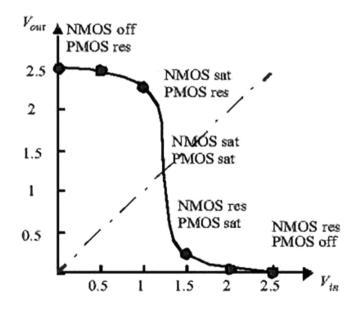

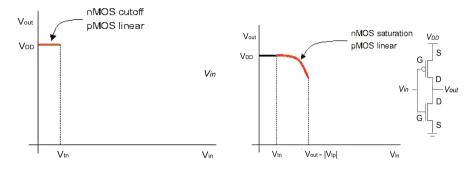

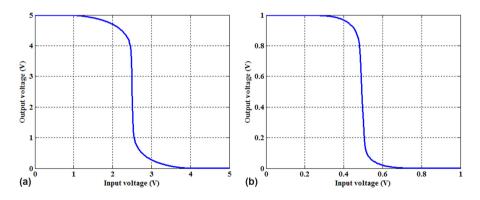

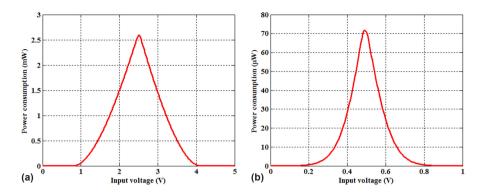

CMOS inverters are the most widely used and adaptable MOSFET inverters used in chip design. They operate with little to no power loss and at relatively high speeds. Furthermore, the CMOS inverter has good logic buffer characteristics: its capacitance in both low and high states is large. A CMOS inverter consists of a set of PMOS and an NMOS transistor connection [11]. In this setting, the supply voltage VDD is placed at the PMOS drain terminal, and the NMOS source terminal is connected to the ground.  $V_{IN}$  is connected to the gate terminals of both transistors, and  $V_{OUT}$  is set between the drain of the NMOS and the source of the PMOS (Figure 1.4). It is important to note that the CMOS inverter does not contain any resistors, which makes it more power efficient than a regular resistor of a MOSFET inverter. Because the voltage at the input of the CMOS device varies between 0 and VDD, the state of the NMOS and PMOS varies accordingly. Figure 1.5 and Figure 1.6 show the characteristics and modes of CMOS [12].

To constitute an operating point, the currents via the NMOS and PMOS bias must be equal. This indicates graphically that the DC points must be situated at the intersection of the relevant load-lines. A few of those points (for VIN = 0, 0.5, 1, 1.5, 2, and 2.5 V) are indicated on the graph. It is evident that every operating point lies either at the upper or lower end of the line.

The voltage transfer characteristic (VTC) of the inverter hence exhibits a narrow transition zone. This zone results from the high gain during the switching flash when

FIGURE 1.4 CMOS inverter [2]

**FIGURE 1.5** Transforming PMOS I-V characteristic to a common coordinate set (assuming VDD = 2.5 V)

**FIGURE 1.6** Load curves for the static CMOS inverter's NMOS and PMOS transistors (VDD = 2.5 V). The dots represent various input voltages' dc operation points [12].

both NMOS and PMOS are temporarily ON. In that operation region, a small change in the input voltage results in a large variation [13].

The VTC shown in Figure 1.7 looks like an inverted step function that specifies accurate switching between ON and OFF. However, in real bias, a gradual transition region exists. The voltage transfer characteristic specifies that for lower input voltage  $V_{IN}$ , the circuit generates high voltage  $V_{OUT}$ , whereas, for high input, it generates 0 volts.

FIGURE 1.7 Characteristics of an inverter [12]

#### FIGURE 1.8 CMOS inverter VTC

The transition region pitch is a measure of quality steep pitches that exact switching. The noise can be calculated by assessing the difference between the input to the output for every region of the ON-OFF mode of operation [12].

Figure 1.8 shows the mode equations for PMOS and NMOS.

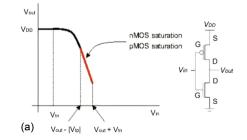

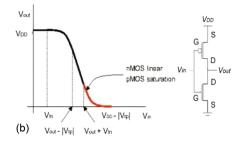

Below are the mode equations for PMOS and NMOS. Figures 1.9a and 1.9b show the operation modes of CMOS.

• Setting PMOS linear IDS equal to NMOS saturation IDS

$$k_n \left(\frac{(V_{in} - V_{in})^2}{2}\right) = k_p \left((V_{in} - V_{DD} - V_{tp})(V_{out} - V_{DD}) - \frac{(V_{out} - V_{DD})^2}{2}\right)$$

(1)

$$\frac{\left(V_{out} - V_{DD}\right)^2}{2} - \left(V_{in} - V_{DD} - V_{ip}\right)\left(V_{out} - V_{DD}\right) + \frac{k_n \left(V_{in} - V_{in}\right)^2}{2} = 0$$

(2)

$$(V_{out} - V_{DD}) = (V_{in} - V_{DD} - V_{tp}) + \sqrt{(V_{in} - V_{DD} - V_{tp})^2 - \frac{k_n}{k_p} (V_{in} - V_{tn})^2}$$

(3)

FIGURE 1.9A CMOS saturation mode

FIGURE 1.9B NMOS linear and PMOS saturation modes

$$V_{out} = (V_{in} - V_{tp}) + \sqrt{(V_{in} - V_{DD} - V_{tp})^2 - \frac{k_n}{k_p} (V_{in} - V_{tn})^2}$$

(4)

• Setting NMOS linear  $I_{DS}$  equal to PMOS saturation  $I_{DS}$

$$k_p \left(\frac{\left(V_{in} - V_{DD} - V_{tp}\right)^2}{2}\right) = k_n \left(\left(V_{in} - V_{tn}\right)V_{out} - \frac{V_{out}^2}{2}\right)$$

(5)

$$\frac{V_{out}^2}{2} - \left(V_{in} - V_{in}\right)V_{out} + \frac{k_p \left(V_{in} - V_{DD} - V_{ip}\right)^2}{2} = 0$$

(6)

$$V_{out} = (V_{in} - V_{tn}) - \sqrt{(V_{in} - V_{tn})^2 - \frac{k_p}{k_n} (V_{in} - V_{DD} - V_{tp})^2}$$

(7)

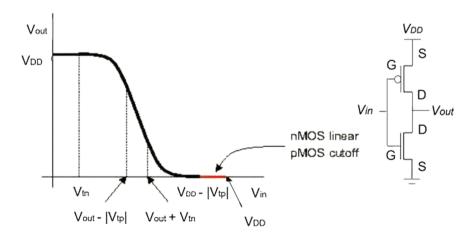

Figure 1.10 shows the linear and cutoff modes of CMOS.

All modes are summarized in Table 1.1.

FIGURE 1.10 NMOS linear and PMOS cutoff modes

|                         | NMOS<br>mode V <sub>our</sub> | Cutoff V <sub>DD</sub> | Saturation<br>$V_{out} = (V_{in} - V_{p}) + \sqrt{(V_{in} - V_{DD} - V_{p})^{2} - \frac{k_{n}}{k_{p}} (V_{in} - V_{m})^{2}}$ | Saturation Transition, V <sub>our</sub> drops     | Linear $V_{out} = (V_m - V_m) - \sqrt{(V_m - V_m)^2 - \frac{k_p}{k_n}(V_m - V_{DD} - V_p)^2}$ | Linear 0                                  |

|-------------------------|-------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------|

|                         | PMOS<br>mode                  | Linear                 | Linear                                                                                                                       | Saturation                                        | Saturation                                                                                    | Cutoff                                    |

| TABLE 1.1<br>CMOS modes | 2 ×                           | $V_{in} < V_{in}$      | $V_i < V_{in} < V_{out} - V_{ip}$                                                                                            | $V_{out} -  V_{t_n}  < V_{in} < V_{out} + V_{in}$ | $V_{out} + V_m < V_m < V_{DD} - V_p$                                                          | $V_{in} > V_{DD} - \left  V_{ip} \right $ |

#### **1.3 THE LOGIC CIRCUIT OF CMOS**

Combinational logic gates with one or more inputs and one output make up static CMOS circuits. Here are some significant CMOS logic gates [14].

#### **1.3.1** The inverter

#### 1.3.1.1 Overview

The inverter is the most basic logic gate. Understanding how an inverter works and its characteristics will make it much simpler to examine other logic gates, adders, and other components of digital design and memory devices [15]. Figure 1.11 shows the operation of a CMOS inverter in low (0) and high (1) inputs.

The NOT gate is another name for the CMOS inverter. The circuit shown above demonstrates that an N-channel MOSFET (NMOS) and a P-channel MOSFET make up a CMOS inverter (PMOS). The NMOS transistor is OFF and the PMOS transistor is ON when the input A is LOW, or logic 0. The VDD has a path to the output thanks to the P-channel MOSFET. The output is HIGH as a result.

Logic 1 as is NMOS is ON and PMOS is OFF when the input is HIGH. The output signal is LOW and connected to GND.

The operation of the inverter is summarized in Table 1.2.

#### 1.3.1.2 Simulation

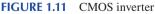

We can use computer-aided design (CAD) software to simulate the operation of the CMOS inverter described above. Figure 1.12 shows the circuit implementation of a CMOS inverter in LTspice for simulation.

# Input Output 0 1 1 0

FIGURE 1.12 CMOS inverter schematic

Now that we have demonstrated how a CMOS device operates and how to design basic logic CMOS gates, we will see how one can use CAD tools to simulate our design and confirm its feasibility. There are many tools that designers use, from freeware like LTspice to licensed tools such as Cadence [16].

In this chapter, we use LTspice for both its user-friendly interface and availability (free of charge).

To design a device, there is a set of parameters that should be provided in a ".txt" file to define the device. Without a template, designing can be challenging for both experienced and junior users. Alternatively, one can use predefined NMOS and PMOS devices provided in LTspice and modify parameters to meet the needs, requirements, and specifications of one's device.

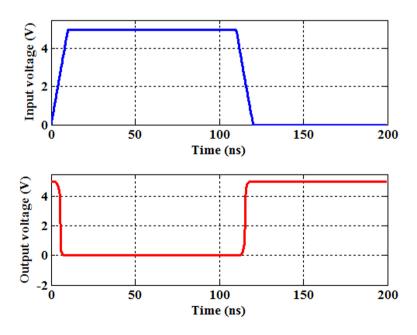

The inverter in Figure 1.12 uses two voltage sources: the biasing power (V1) and the signal to be inverted (V2). This signal is presented to the input as a pulsed voltage source with high and low levels representing 1s and 0s, respectively.

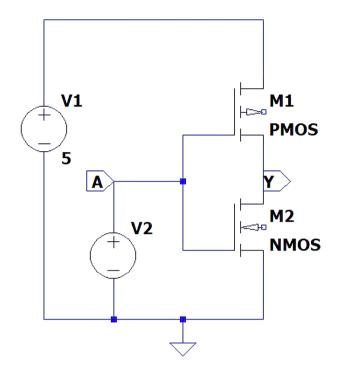

Figure 1.13 shows the input voltage V(a) and its corresponding inverted output V(y). This confirms the proper operation of the circuit as the inverter of CMOS with results matching the truth table (see Table 1.2 for context).

FIGURE 1.13 Simulation results of CMOS inverter

#### 1.3.2 CMOS NAND GATE

#### 1.3.2.1 Overview

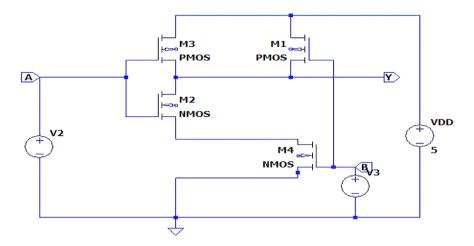

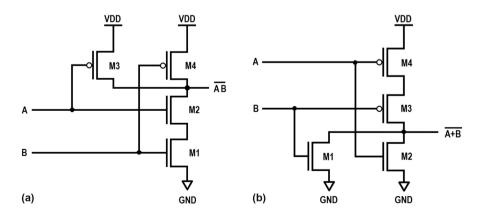

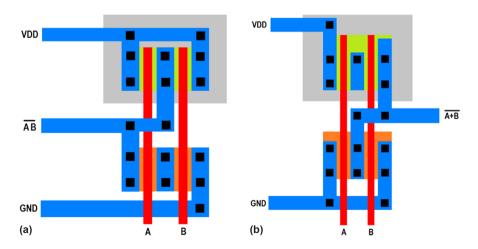

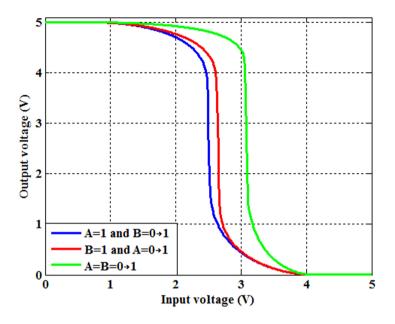

Two N-channel MOSFETs are connected in series between Y (the output) and GND, and two P-channel MOSFETs are connected in parallel between VDD and Y in a two-input NAND gate. A NAND gate's schematic is shown in Figure 1.14 in LTspice for simulation.

At least one of the NMOS transistors will be OFF if either input A or B is low (logic 0). Since the NMOS transistors are wired in series and lead to the GND, this disrupts the path from Y to GND. To complete a path from Y to VDD in this instance, however, at least one of the PMOS transistors will be VDD. This makes the output Y high (logic 1) [17].

If A and B are high (logic 1), both NMOS transistors are ON. This completes the path from Y to GND. This makes Y low (logic 0). The output Y will be high for all other combinations of inputs A and B. The truth table of the NAND logic gate is given below [18]. The truth table below shows the inputs/output of the NAND gate.

FIGURE 1.14 CMOS NAND circuit

#### 1.3.2.2 Simulation

The circuit of Figure 1.14 is an LTspice implementation of the NAND logic gate. Upon providing pulsed inputs V(a) and V(b), as may be seen, the result of V(y) matches the NAND function behavior demonstrated in Table 1.3 and depicted in the simulation results of Figure 1.15.

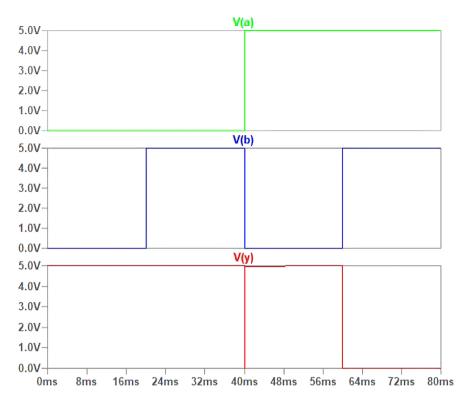

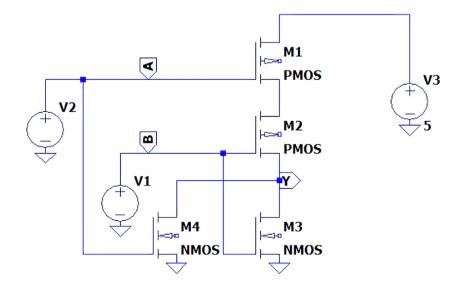

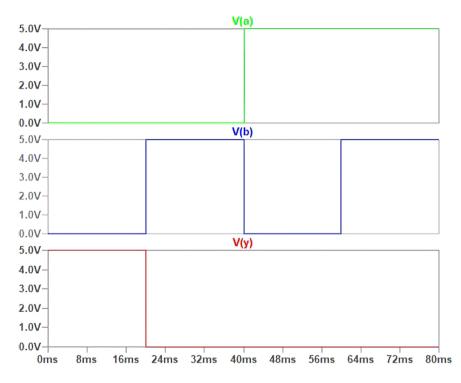

#### 1.3.3 CMOS NOR GATE

#### 1.3.3.1 Overview

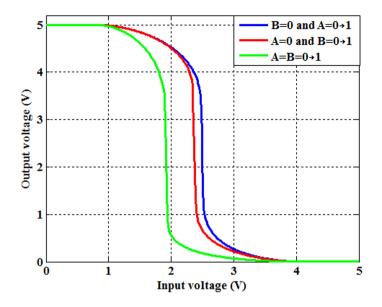

The NMOS transistors and PMOS transistors are coupled in series and parallel, respectively, in a two-input NOR gate. At least one NMOS transistor pulls the output low when at least one of the inputs is high. Only when both inputs are low does the output become high. Figure 1.16 represents the schematic of a NOR gate in LTspice for simulation. The truth table of the NOR logic gate is presented in Table 1.4 (Figure 1.17).

| TABLE 1.3NAND truth table |                               |  |  |

|---------------------------|-------------------------------|--|--|

| Input B                   | Output                        |  |  |

| 0                         | 1                             |  |  |

| 1                         | 1                             |  |  |

| 0                         | 1                             |  |  |

| 1                         | 0                             |  |  |

|                           | <b>Input B</b><br>0<br>1<br>0 |  |  |

FIGURE 1.15 CMOS NAND simulation

FIGURE 1.16 CMOS NOR circuit

| TABLE 1.4NOR truth table |         |        |  |  |

|--------------------------|---------|--------|--|--|

| Input A                  | Input B | Output |  |  |

| 0                        | 0       | 1      |  |  |

| 0                        | 1       | 0      |  |  |

| 1                        | 0       | 0      |  |  |

| 1                        | 1       | 0      |  |  |

FIGURE 1.17 CMOS NOR simulation

#### 1.3.3.2 Simulation

The simulated results for the NOR circuit design are shown in Figure 1.16 with their corresponding response to given inputs matching the NOR truth table of Table 1.4.

#### 1.4 CMOS TECHNOLOGY AND APPLICATIONS

Due to its adaptability and efficiency in the use of electricity, CMOS is the technology of choice for the manufacture of integrated circuits (ICs). The low power design is the most dependable of the current technologies and offers the benefit of little heat dissipation [19]. Depending on the circuit layout, P- and N-type transistors can be set up to create logic gates.

CMOS technology is one of the most popular technologies in the computer chip design industry. This technology makes use of both the P-channel and N-channel semiconductor biases. CMOS is one of the most popular MOSFET technologies available [20]. This is the dominant semiconductor technology for all semiconductor devices including memory devices, volatile and non-volatile, and logic gate circuits.

The N-channel MOSFET and the P-channel MOSFET are both made with matching properties thanks to their design (ON and OFF). The primary benefit of CMOS technology over bipolar or the formerly common NMOS technologies is its exceptionally low power consumption in static settings because it only consumes power during switching operations [21].

When compared to bipolar or NMOS technology, this enables the integration of a significantly greater number of sensing gates on the VLSI IC. It is simpler to create various logic functions when NMOS and PMOS bias are combined in CMOS logic gates. The size of the transistor can be varied and further shrunk thanks to developments in CMOS IC production methods [22].

By scaling down the transistor, it is possible to incorporate more logical operations into the same IC without sacrificing performance. CMOS IC technology was initially employed to create digital logic ICs. CMOS technology is now used in analog ICs and mixed-signal designs because of its low cost and greater functionality [23]. CMOS logic has two different modes: low power dispersion and high noise perimeters. In both modes, it operates over a wide range of source and input voltages.

#### 1.5 LAYOUT OF CMOS

The CMOS design layouts are based on the following components:

- (a) Substrates.

- (b) Wells: for NMOS and PMOS devices, respectively, wells are P-type and N-type.

- (c) Diffusion areas: in these regions, the transistors are produced and are referred to as an active layer. For NMOS and PMOS transistors, respectively, these are denoted by n+ and p+.

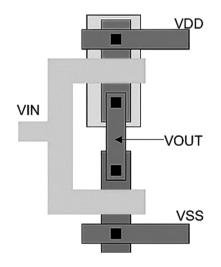

Figure 1.18 shows a layout for a CMOS with P-substrate and N-well.

The circuit architecture (mask layout) and initial transistor scaling are the first steps in the iterative process of designing the physical (mask layout) of CMOS logic gates (to realize the desired performance specifications). Based on the fan-out, the number of devices, and the anticipated length of the interconnection lines, the designer can only make an estimate of the overall parasitic load at the output node at this time [24].

If the logic gate contains more than four transistors, the ideal ordering of the transistors in logic gates with more than four transistors. Now, it is possible to design

FIGURE 1.18 CMOS Inverter layout

a straightforward stick diagram layout that displays the contacts' locations, as well as the transistors' local interconnections [25]. Figure 1.19 depicts a mask layout for a CMOS inverter architecture.

The layout's topology is created by drawing the mask layers in accordance with the layout design guidelines (using a layout editor tool). To account for all design principles, this technique may need to go through multiple tiny iterations, but the fundamental topology shouldn't be significantly altered. The finished layout is subjected to a circuit extraction technique after the final design rule check (DRC) to

ascertain the true transistor sizes and, more crucially, the parasitic capacitances at each node. The extraction step's outcome is often in-depth [26].

# **1.6 CONCLUSION**

The CMOS circuit configuration process comprises characterizing circuit information sources and results, hand computations, circuit recreations, circuit format, reconsideration of circuit sources of info and results, creation, and testing. The analysis of inverters is often extended to elucidate the behaviors of more complex gates such as NAND, NOR, or XOR, which successively form the building blocks for modules like multipliers and processors. In this chapter, we specialize in one single incarnation of the inverter gate, the static CMOS inverter, or the CMOS inverter short. We implement and simulate the inverter, NAND, and NOR gates using the LTspice CAD tool. The process is like other CAD tools and can be used to simulate more complex circuits by combining or modifying these basic elements. A green revolution in the CMOS domain using low-cost MOSFET is not far from being realized [27, 28].

#### REFERENCES

- B. Hoeneisen and C. A. Mead, "Fundamental limitations in microelectronics—I. MOS technology." *Solid-State Electronics*, 15(7), 819–829 (1972).

- T. Sakurai and A. R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas." *IEEE Journal of Solid-State Circuits*, 25(2), 584–594 (1990). doi: 10.1109/4.52187.

- J.-H. Wang, H.-H. Hsieh, and L.-H. Lu, "A 5.2-GHz CMOS T/R switch for ultra-low-voltage operations." *IEEE Transactions on Microwave Theory and Techniques*, 56(8), 1774–1782 (2008).

- R. H. Caverly, "Linear and nonlinear characteristics of the silicon CMOS monolithic 50-ohm microwave and RF control element." *IEEE Journal of Solid-State Circuits*, 34(1), 124–126 (1999).

- I. Baturone, S. Sanchez-Solano, A. Barriga, and J. L. Huertas, "Implementation of CMOS fuzzy controllers as mixed-signal integrated circuits." *IEEE Transactions on Fuzzy Systems*, 5(1), 1–19 (1997). doi: 10.1109/91.554443.

- R. A. Blauschild, P. A. Tucci, R. S. Muller, and R. G. Meyer, "A new NMOStemperaturestable voltage reference." *IEEE Journal of Solid-State Circuits*, SC-13, 767–774 (1978).

- 7. X. Zhang and E. I. EI-Masry, "A novel CMOS OTA based on body-driven MOSFETs and its applications in OTA-C filters." *IEEE Transaction on Circuits and Systems Part I: Fundamental Theory and Applications*, 54(6), 1204–1212 (2007).

- A. A. Cherepanov, I. L. Novikov, and V. Y. Vasilyev, "An evaluation of CMOS inverter operation under cryogenic conditions." In 2018 19th International Conference of Young Specialists on Micro/Nanotechnologies and Electron. Devices (EDM), 2018, pp. 40–43. doi: 10.1109/EDM.2018.8435038.

- H. Salama, B. Saman, E. Heller, R. H. Gudlavalleti, R. Mays, and F. Jain, "Twin drain quantum well/quantum dot channel spatial wave-function switched (SWS) FETs for multi-valued logic and compact DRAMs." *International Journal of High Speed Electronics and Systems*, 27(03n04), 1840024 (2018).

- S. Mahapatra, V. Vaish, C. Wasshuber, K. Banerjee, and A. M. Ionescu, "Analytical modeling of single electron transistor for hybrid CMOS-SET analog IC design." *IEEE Transactions on Electron Devices*, 51(11), 1772–1782 (2004). doi: 10.1109/ TED.2004.837369.

- L. Bisdounis, S. Nikolaidis, and O. Koufopavlou, "Analytical transient response and propagation delay evaluation of the CMOS inverter for short-channel devices." *IEEE Journal of Solid-State Circuits*, 33(2), 302–306 (1998).

- M. R. Bruce and V. J. Bruce, "ABCs of photon emission microscopy." *Electronic Device Failure Analysis*, 5(3), 13–22 (2003).

- C.-C. Huang, C.-Y. Wang, and J.-T. Wu, "A CMOS 6-bit 16-GS/s time-interleaved ADC using digital background calibration techniques." *IEEE Journal of Solid-State Circuits*, 46(4), 848–858 (2011). doi: 10.1109/JSSC.2011.2109511.

- C. Chen et al., "Integrating poly-silicon and InGaZnO thin-film transistors for CMOS inverters." *IEEE Transactions on Electron Devices*, 64(9), 3668–3671 (2017). doi: 10.1109/TED.2017.2731205.

- C. Schlünder, F. Proebster, J. Berthold, K. Puschkarsky, G. Georgakos, W. Gustin, and H. Reisinger, "Circuit relevant HCS lifetime assessments at single transistors with emulated variable loads." In 2017 IEEE International Reliability Physics Symposium (IRPS), 2017, pp. 2D–2. IEEE.

- H. Salama, B. Saman, R. H. Gudlavalleti, P. Y. Chan, R. Mays, B. Khan, E. Heller, J. Chandy, and F. Jain, "Simulation of stacked quantum dot channels SWS-FET using multi-FET ABM modeling." *International Journal of High Speed Electronics and Systems*28(03n04), 1940025 (2019).

- R. H. Gudlavalleti, B. Saman, R. Mays, H. Salama, E. Heller, J. Chandy, and F. Jain, "A noveladdressing circuit for SWS-FET based multi-valued dynamic random access memory array." *International Journal of High Speed Electronics and Systems*, 29, 2040009 (2020).

- A. Boglietti, P. Ferraris, M. Lazzari, and M. Pastorelli, "Influence of the inverter characteristics on the iron losses in PWM inverter-fed induction motors." *IEEE Transactions* on *Industry Applications*, 32(5), 1190–1194 (1996).

- B. G. Lee, A. V. Rylyakov, W. M. J. Green, S. Assefa, C. W. Baks, R. Rimolo-Donadio, D. M. Kuchta et al., "Monolithic silicon integration of scaled photonic switch fabrics, CMOS logic, and device driver circuits." *Journal of Lightwave Technology*, 32(4), 743– 751 (2013).

- B. Lu and S. K. Sharma, "A literature review of IGBT fault diagnostic and protection methods for power inverters." *IEEE Transactions on Industry Applications*, 45(5), 1770–1777 (2009). doi: 10.1109/TIA.2009.2027535.

- H. T. Bui, Y. Wang, and Y. Jiang, "Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates." *IEEE Transactions on Circuits and Systems. Part II: Analog and Digital Signal Processing*, 49(1), 25–30 (2002). doi: 10.1109/82.996055.

- 22. M. G. Johnson, "A symmetric CMOS NOR gate for high-speed applications." *IEEE Journal of Solid-State Circuits*, 23(5), 1233–1236 (1988).

- S. Kang, B. Choi, and B. Kim, "Linearity analysis of CMOS for RF application." *IEEE Transactions on Microwave Theory and Techniques*, 51(3), 972–977 (2003). doi: 10.1109/TMTT.2003.808709.

- 24. H. Salama, B. Saman, R. Gudlavalleti, R. Mays, E. Heller, J. Chandy, and F. Jain, "Compact 1-bit full adder and 2-bit SRAMs using n-SWS-FETs." *International Journal of High Speed Electronics and Systems*, 29(01n04), 2040013 (2020).

- 25. R. J. Baker, et al. *CMOS: Circuit Design, Layout, and Simulation.* Rev. 4th ed., 2019. IEEE Press.

- K. H. Cirne and S. P. Gimenez, "Layout design of CMOS inverters with circular and conventional gate MOSFETs by using IC station mentor." In: *Proc. 9th Microeletronics Students Forum*, SBmicro 2009 (2009).

- L. Zhang, R. Fakhrabadi, M. Khoshkhoo, and S. Husien, "A robust second-order conic programming model with effective budget of uncertainty in optimal power flow problem.", *Journal of Energy and Power Technology*, (4) 1–15, (2022).

- 28. H. Salama, "Quantum dot solar cells." arXiv Preprint ArXiv:2211.06898 (2022).

# 2 Conventional CMOS circuit design

Samir Labiod, Abdelmalek Mouatsi, Zakaria Hadef, and Billel Smaani

# CONTENTS

| 2.1  | Introdu                                    | action                         | . 21 |  |  |  |

|------|--------------------------------------------|--------------------------------|------|--|--|--|

| 2.2  | CMOS                                       | fabrication technology         | .23  |  |  |  |

|      | 2.2.1                                      | Well formation                 |      |  |  |  |

|      | 2.2.2                                      | MOSFET fabrication process     | .23  |  |  |  |

|      | 2.2.3                                      | Interconnections               | .26  |  |  |  |

|      | 2.2.4                                      | Layout of MOS transistor       | .27  |  |  |  |

|      | 2.2.5                                      | Long and short-channel MOSFETs | .27  |  |  |  |

| 2.3  | Parasitics associated with CMOS technology |                                |      |  |  |  |

|      | 2.3.1                                      | RC delay through the n-well    | . 29 |  |  |  |

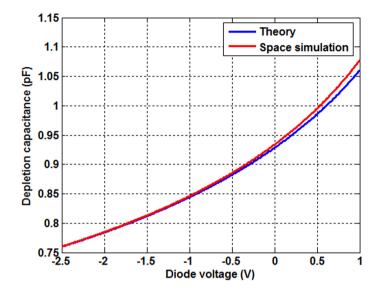

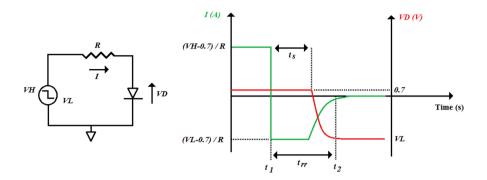

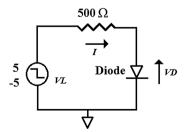

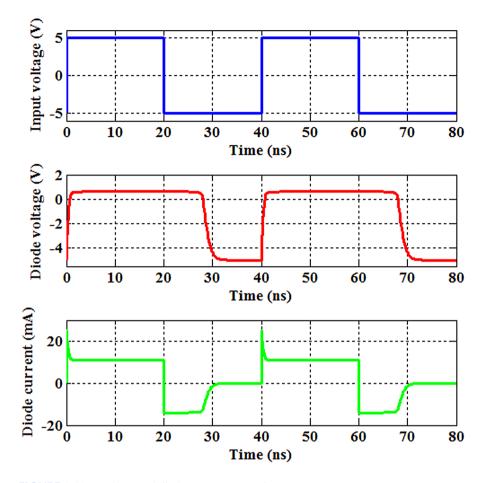

|      | 2.3.2                                      | Depletion capacitance          | . 33 |  |  |  |

|      | 2.3.3                                      | Storage capacitance            | .36  |  |  |  |

|      | 2.3.4                                      | Metal-substrate capacitance    |      |  |  |  |

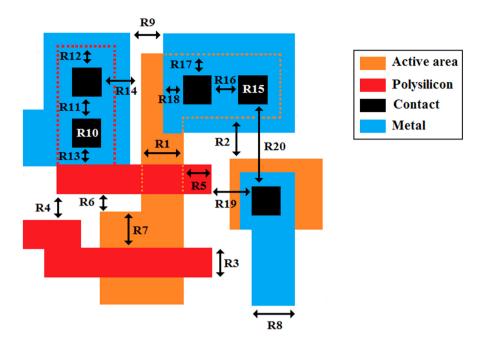

| 2.4  | Layout                                     | design rules                   | . 39 |  |  |  |

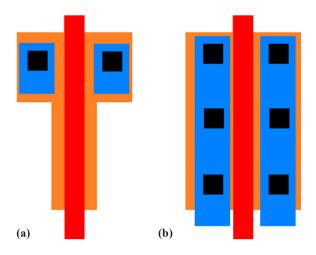

| 2.5  | Analog and digital CMOS circuit design     |                                |      |  |  |  |

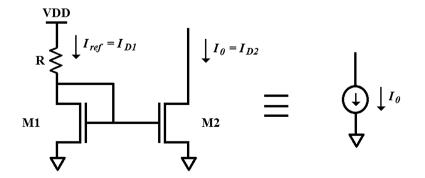

|      | 2.5.1                                      | Current mirrors                | .40  |  |  |  |

|      | 2.5.2                                      | Inverter                       | .43  |  |  |  |

|      | 2.5.3                                      | NAND and NOR gates             | .47  |  |  |  |

|      | 2.5.4                                      | Full adder                     | . 51 |  |  |  |

| 2.6  | Conclu                                     | ision                          | . 52 |  |  |  |

| Refe | References                                 |                                |      |  |  |  |

|      |                                            |                                |      |  |  |  |

# 2.1 INTRODUCTION

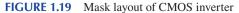

Digital CMOS (complementary metal-oxide semiconductor) integrated circuits (ICs) have been the driving force behind very large-scale integration (VLSI) for high-performance computing and engineering applications [1–3]. Low power, reliable performance, and circuit techniques for high speed, such as using dynamic circuits and ongoing improvements in processing technology, are prominent features and the reason behind the constant demand for digital CMOS ICs. With this kind of technology, it can be seen that the level of integration which once existed in several millions of transistors for logic chips and reached an even higher level in the case of memory

**FIGURE 2.1** Evolution of technologic in integrated circuits versus time: (a) minimum feature size and (b) level of memory and logic chips integrations

ones, is now available in only one chip. It presents an immense challenge for chip developers in processing, methodology, design, testing, and project management.

Advances in device manufacturing technology allow the steady reduction of minimum feature size. Figure 2.1a shows the progress of the minimum feature size of transistors in integrated circuits since the late 1970s. In 1980, at the beginning of the VLSI era, the typical minimum feature size was  $2 \mu m$ , and a feature size of 14 nm was expected around the year 2017. The actual development of the technology, however, has far exceeded these expectations. A minimum feature size of 0.25  $\mu mn$  had been reached by 1995.

When the integration density of circuits is inspected, there is clearly a distinction between the memory and the logic chips. Figure 2.1b shows the level of integration through time for memory and logic circuits, beginning in 1970. The increase of transistors number has continued at an exponential rate over the last three decades, effectively confirming Gordon Moore's prediction on the growth rate of chip complexity, which was made in the early 1960s (Moore's Law) [4]. In this chapter, we present a brief overview of CMOS process integration. Process integration refers to the well-defined collection of semiconductor processes required to fabricate CMOS integrated circuits [5, 6]. We provide more information and examples related to the layout of the different interconnections, and MOSFETs. Design rules and the main fundamental layout techniques have been covered [7].

To illustrate the effect of miniaturization, different simulations were performed for long and short-channel MOSFETs models. The parasitic effect plays a very important role in the field of CMOS circuit design [8], and for this, it is essential to do some simulations to illustrate these effects.

A current mirror is a basic building block for analog circuit design [9]. Fundamental understanding and layout techniques for analog circuit design have been presented and simulated.

Finally, the main concepts for digital circuit design have been presented, such as the basic CMOS static logic gates inverter, NAND, and NOR) and arithmetic function (full adder). SPICE simulations have been performed for DC and dynamic characteristics.

# 2.2 CMOS FABRICATION TECHNOLOGY

The CMOS (complementary metal-oxide silicon) fabrication technology is recognized as the leader of VLSI systems technology.

# 2.2.1 Well formation

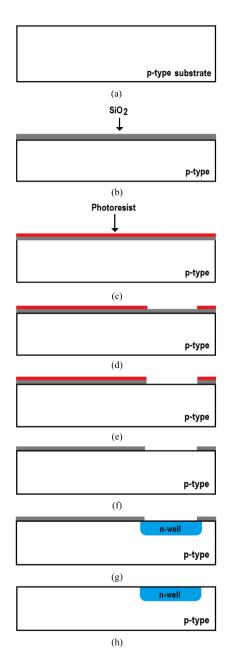

Figure 2.2 shows cross-sections of the wafer after each processing step involved in forming the n-well [10, 11]. Figure 2.3a illustrates the bare substrate before processing. Changing the substrate from p-type to n-type in the region of the well by adding enough dopants into it is what is required to form the n-well. The growth of a protective layer of oxide over the entire wafer, and relocating it to where we want the wells, is necessary for us to define what regions receive n-wells.

In a high-temperature (typically 900–1200 °C) furnace, the wafer is first oxidized, due to Si and O<sub>2</sub> reacting and becoming SiO<sub>2</sub> on the wafer surface (Figure 2.2b). The pattern of oxide is obligated to define the n-well. An organic photoresist that softens when exposed to light is spun onto the wafer (Figure 2.2c). The photoresist is exposed through the n-well mask (Figure 2.3b), which allows light to pass through only where the well should be. The softened photoresist is removed to expose the oxide (Figure 2.2d).

The oxide part that is not protected by the photoresist is etched with hydrofluoric acid (HF) (Figure 2.2e), then the acids mixture called piranha etch is for cleaning out the remaining photoresist (Figure 2.2f). The well is formed where the substrate is not covered with oxide. Two ways to add dopants are diffusion and ion implantation. In the diffusion process, the wafer is placed in a furnace with a gas containing the dopants. When heated, dopant atoms diffuse into the substrate. Notice how the well is wider than the hole in the oxide on account of lateral diffusion (Figure 2.2g). With ion implantation, dopant ions are accelerated through an electric field and blasted into the substrate. In either method, the atoms are prevented from entering the substrate where no well is intended. Finally, stripping the remaining oxide with HF leaves the bare wafer with wells in the appropriate places.

#### 2.2.2 MOSFET FABRICATION PROCESS

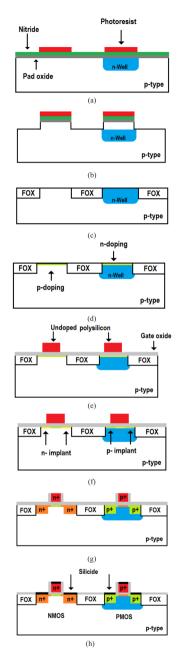

A general CMOS process flow is demonstrated in Figure 2.3. Fabrication of NMOS and PMOS devices is detailed in [13, 14]. The first step, Figure 2.3a, is to grow a thin pad oxide on the surface of the entire wafer. Depositing nitride and photoresist layers follow this. The photoresist is then patterned using the active mask. The remaining photoresist, seen in Figure 2.3a, ultimately defines the openings in the field oxide (FOX) [15].

In Figure 2.3b, the areas not covered by the photoresist are etched. The etching extends down into the wafer so that shallow trenches are formed. In Figure 2.3c, the shallow trenches are filled with  $SiO_2$ . These trenches isolate the active areas and form the field regions (FOX). This type of device isolation is called shallow trench isolation (STI).

FIGURE 2.2 Cross-section while manufacturing the n-well [12].

FIGURE 2.3 General CMOS process flow [16].

In Figure 2.3d, adjusting the threshold voltages of the devices is performed with two separate implants. A photoresist is patterned (twice) to select the areas for threshold voltage adjustment.

Figure 2.3e shows the results after the deposition and patterning of polysilicon. This is followed by various implants. In Figure 2.3f, we see a shallow implant forming the MOSFET's lightly doped drains (LDD). The LDD implants prevent the electric field directly next to the source/drain regions from becoming too high. Note that the poly gate is used as a mask during this step.

The next step is to grow a spacer oxide on the sides of the gate poly (Figure 2.3g). After the spacer is grown, the n+/p+ implants are performed. This implant dopes the areas used for the source and drain of the MOSFETs as well as the gate poly. The last step is to silicide the source and drain regions of the MOSFET. Finally, note that the process sequence seen in Figure 2.3 is often referred to, in the manufacturing process, as the front-end-of-line (FEOL). The fabrication of the metal layers and associated contacts/vias is referred to as the back-end-of-line (BEOL).

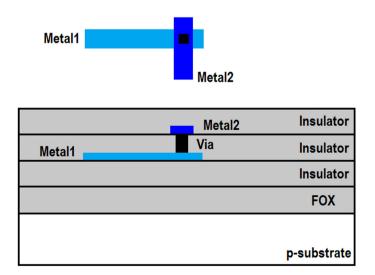

### 2.2.3 INTERCONNECTIONS

Typical metalization is used with aluminum, while contact holes are filled by a plug of tungsten. Low resistivity and low dielectric isolation layers have been used to minimize the RC time constants of the interconnection lines. Metalization level and a via are established at the same time in the dual damascene technique. Figure 2.4 shows an example layout and cross-section view. The vial layer connects metal and metal2. In the location indicated, the via layer specifies that the insulator will be removed. Once metal2 is set, the two metals are connected by the plug [17]. Notice

that in the case of using more than two layers of metal, via2 would connect metal2 to meta3, and via3 would connect metal3 to metal4.

The contact layer connects metall to either active (n+/p+) or poly. Unless we want to form a rectifying contact (a Schottky diode), we never connect metal directly to the substrate or well.

Further, we won't connect metal to poly without having the silicide in place. Never put a suicide block around a contact to poly [18].

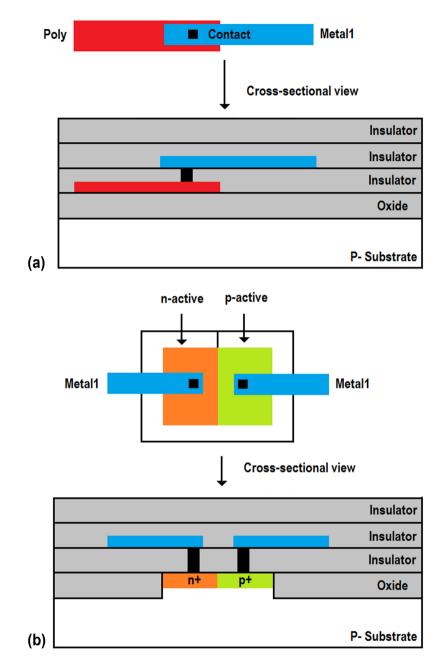

Figure 2.5a shows a layout and corresponding cross-sectional view of the layers metall, contact, and poly (a contact to poly). Figure 2.5b shows a connection to n+ and p+.

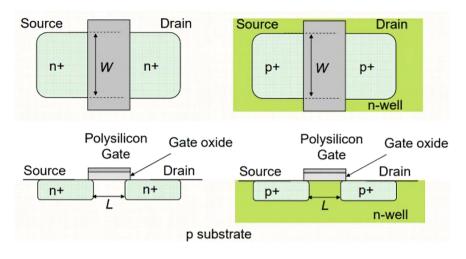

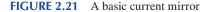

# 2.2.4 LAYOUT OF MOS TRANSISTOR

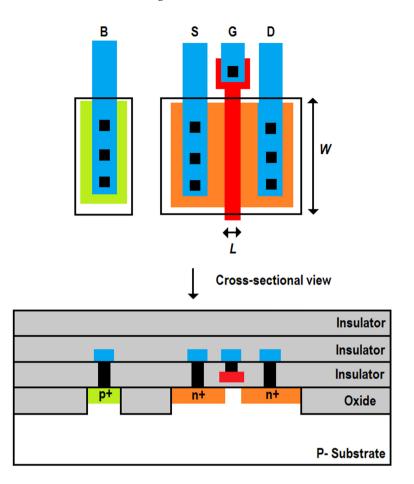

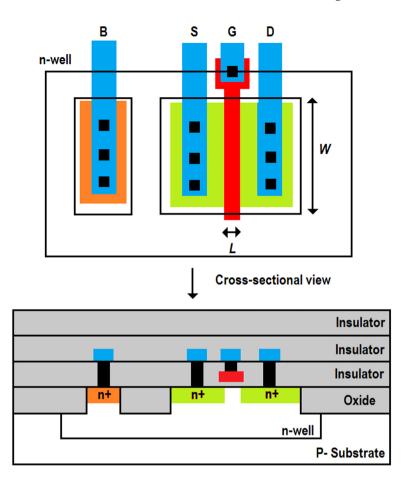

Layout and cross-section views of the NMOS device are shown in Figure 2.6. We recall that the MOSFET is a four-terminal device drain, source, gate, and substrate. Figure 2.6 shows the bulk connection in the layout and in the schematic. In an n-well process, the bulk is tied to ground, so the bulk connection is normally not shown in the schematic symbol. Source and drain are interchangeable.

Cross-section and layout views for the NMOS device are shown in Figure 2.7. Note how we lay the device out in an n-well. Also seen in the figure is the schematic symbol for the PMOS device. Again, the source and drain of the MOSFET are interchangeable. The n-well is normally tied to the highest potential,  $V_{DD}$ , in the circuit to keep the parasitic n-well/p-substrate diode from forward biasing.

#### 2.2.5 LONG AND SHORT-CHANNEL MOSFETS

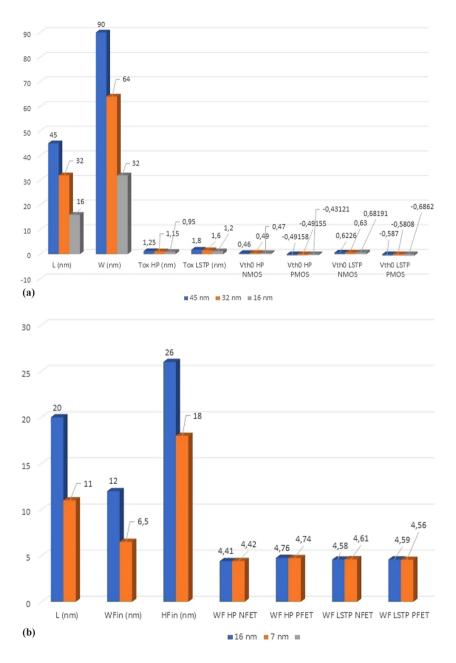

In this section, we will perform electrical simulations to present the main results for long and short-channel MOSFET. The typical parameters for the sizes and electrical parameters used for long and short-channel CMOS are shown in Table 2.1.

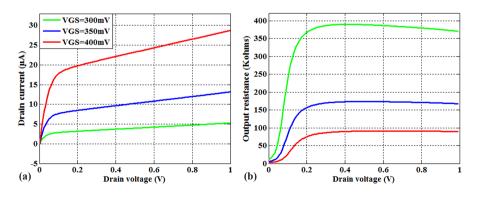

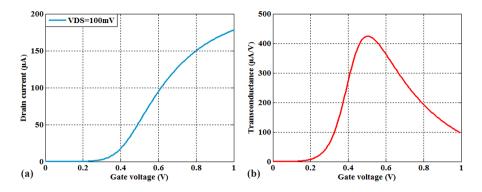

Figure 2.8a shows the I-V curves for a 50/2 NMOS device (actual size of 2.5  $\mu m/100 nm$  device) with different values of  $V_{GS}$ =300 mV, 350 mV, and 400 mV. The current shows significant variation as  $V_{DS}$  changes. When  $I_D$  change with  $V_{DS}$  and  $V_{GS}$ =350 mV, the drain current is 10  $\mu$ A as an approximation. Figure 2.8b presents the output resistance for a 50/2 NMOS device. We get the output resistance by taking the reciprocal of the drain current's derivative in Figure 2.8a. To calculate the  $V_{DSsat}$ , we can look at the point where the output resistance starts to increase. In the case where  $V_{GS}$ =350 mV, we have  $V_{DSsat}$ =50 mV. However, notice that if we use larger  $V_{DS}$ , we get considerably higher output resistances.

Figure 2.9a shows a plot of drain current versus  $V_{GS}$  for a MOSFET in the shortchannel process. The threshold voltage is calculated by the linear extrapolation back to the axis of the gate voltage. In Figure 2.9b, we take the derivative of (a) to get the  $g_m$  of the device. We can linearly extrapolate the threshold voltage back to the gate voltage axis. The two methods give different results; from (a) the threshold voltage is  $V_{THN}$ =358.3 mV, while from (b)  $V_{THN}$ =281.4 mV.

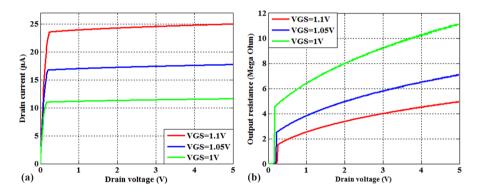

Figure 2.10a depicts the I-V curves for a 10/2 NMOS device (actual size of 10  $\mu m/2 \mu m$  device) with different values of  $V_{GS}$ =1V, 1.05V, and 1.1V. The current shows

**FIGURE 2.5** Metal connections: (a) metal connecting to poly and (b) metal connecting to n and p active [14]

FIGURE 2.6 Cross-section and layout views for the NMOS device [19]

significant variation as  $V_{DS}$  changes. From the I-V characteristics, *the* drain current is approximately 20  $\mu$ A for  $V_{GS}$ =1.05V. The output resistance for a 10/2 NMOS device is presented in Figure 2.10b for different values  $V_{GS}$ =1V, 1.05V, and 1.1V.

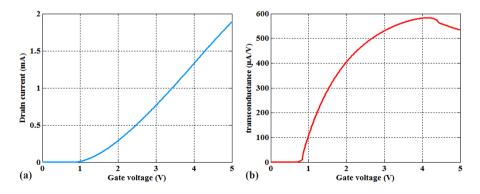

Figure 2.11a and Figure 2.11b depict the variation of drain current and transconductance against  $V_{GS}$  respectively for a MOSFET in the long-channel process. From (a), the threshold voltage is  $V_{THN}$ =1.12V, while from (b)  $V_{THN}$ =800mV.

# 2.3 PARASITICS ASSOCIATED WITH CMOS TECHNOLOGY

# 2.3.1 RC DELAY THROUGH THE N-WELL

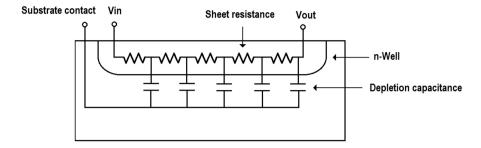

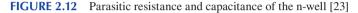

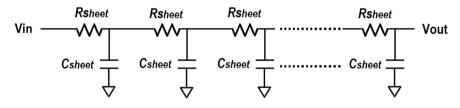

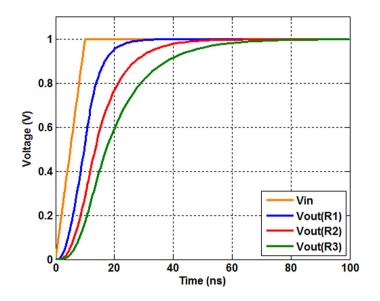

In this part, we notice that the n-well can be used as a diode and as a resistor. Parasitic resistance and capacitance related to the n-well are shown in Figure 2.12.

FIGURE 2.7 Cross-section and layout views for the PMOS device [19]

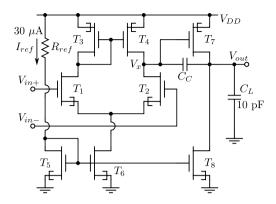

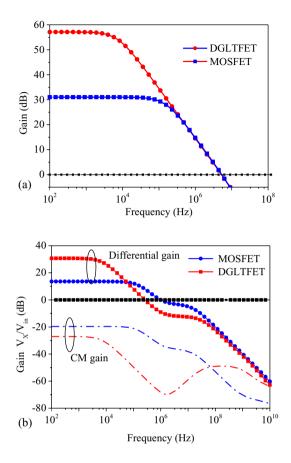

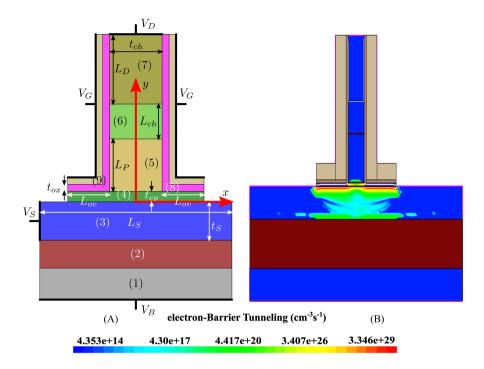

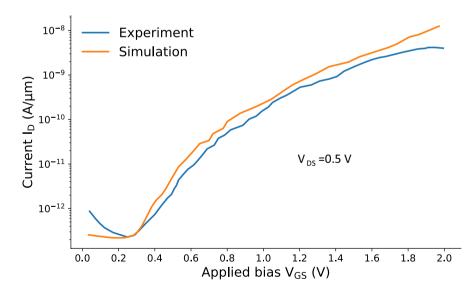

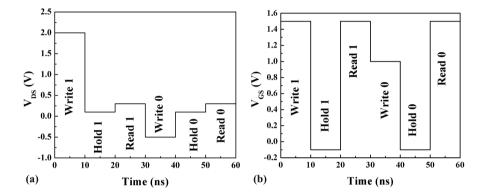

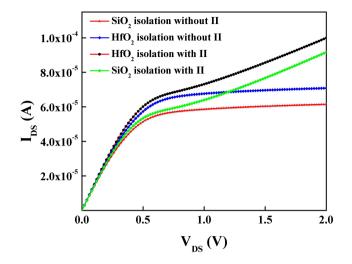

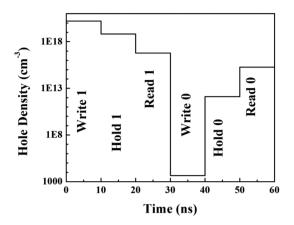

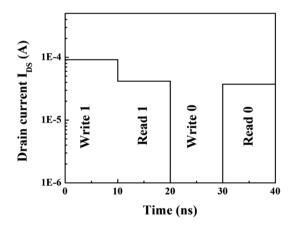

If we apply a voltage pulse to one side of the n-well resistor and measure the delay time at the 50% points of the pulses, the pulse will occur after the delay time [20–23].