# **Quantum Computing** A pathway to quantum logic design

Hafiz Md Hasan Babu

### Quantum Computing (Second Edition)

A pathway to quantum logic design

#### Hafiz Md Hasan Babu

Department of Computer Science and Engineering, University of Dhaka, Dhaka, Bangladesh

IOP Publishing, Bristol, UK

© IOP Publishing Ltd 2023

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the publisher, or as expressly permitted by law or under terms agreed with the appropriate rights organization. Multiple copying is permitted in accordance with the terms of licences issued by the Copyright Licensing Agency, the Copyright Clearance Centre and other reproduction rights organizations.

Permission to make use of IOP Publishing content other than as set out above may be sought at permissions@ioppublishing.org.

Hafiz Md Hasan Babu has asserted his right to be identified as the author of this work in accordance with sections 77 and 78 of the Copyright, Designs and Patents Act 1988.

ISBN 978-0-7503-5683-1 (ebook) ISBN 978-0-7503-5681-7 (print) ISBN 978-0-7503-5684-8 (myPrint) ISBN 978-0-7503-5682-4 (mobi)

DOI 10.1088/978-0-7503-5683-1

Version: 20230601

IOP ebooks

British Library Cataloguing-in-Publication Data: A catalogue record for this book is available from the British Library.

Published by IOP Publishing, wholly owned by The Institute of Physics, London

IOP Publishing, No.2 The Distillery, Glassfields, Avon Street, Bristol, BS2 0GR, UK

US Office: IOP Publishing, Inc., 190 North Independence Mall West, Suite 601, Philadelphia, PA 19106, USA

### Contents

**Preface to the Second Edition**

#### Acknowledgments

#### **Author biography**

#### Acronyms

#### Part I Quantum logic

#### **1 Quantum logic**

- 1.1 Overview

- 1.2 Motivations towards quantum computing

1.3 The relationship between reversible and quantum logic

- 1.4 Quantum computers

- 1.5 The working principles of quantum computers

- 1.6 The evolution of quantum computers

- 1.7 Why pursue quantum computing?

- 1.8 Summary

Critical thinking questions References

#### 2 Basic definitions of quantum logic

2.1 The quantum qubit

#### 2.2 The quantum gate

- 2.2.1 The quantum Feynman gate

- 2.2.2 The quantum Tofolli gate

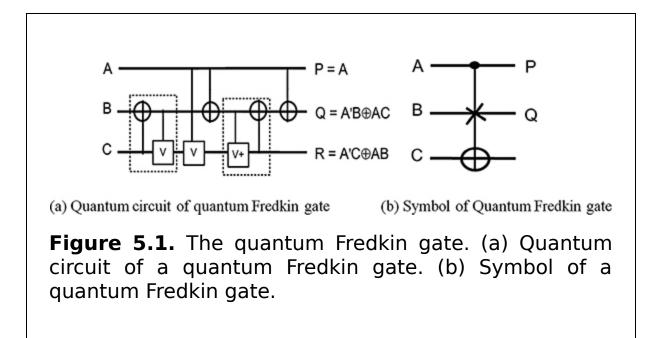

- 2.2.3 The quantum Fredkin gate

- 2.3 Garbage outputs

- 2.4 Constant inputs

- 2.5 Area

- 2.6 Power

- 2.7 Delay

- 2.8 Depth

- 2.9 Quantum cost

- 2.10 Quantum gate calculation complexity

- 2.11 Summary

Critical thinking questions

References

#### **3 The quantum qubit string comparator**

- 3.1 Characteristics of a quantum comparator

- 3.2 The quantum magnitude comparator

- 3.3 The design of a quantum comparator3.3.1 Example

- 3.4 Summary Critical thinking questions References

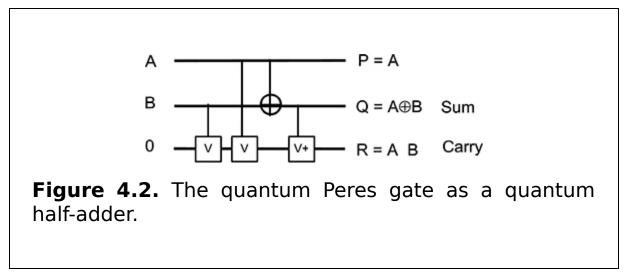

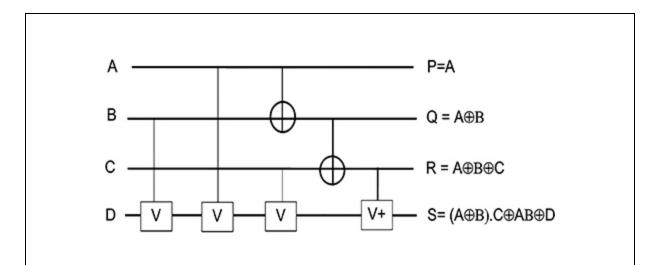

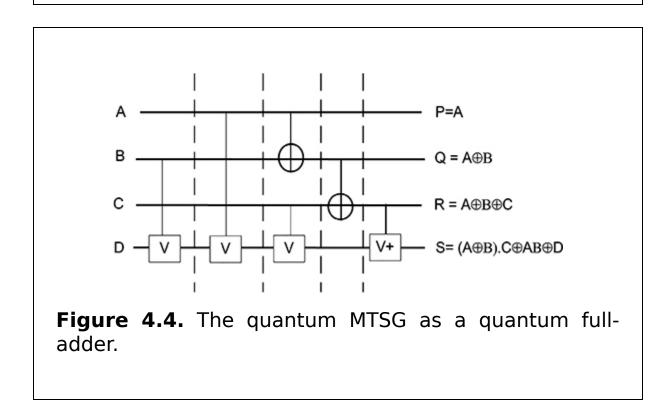

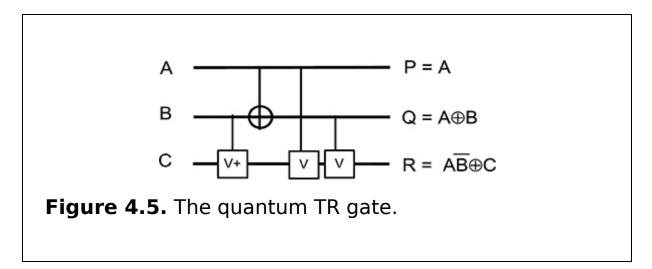

#### 4 The quantum full-adder and subtractor

#### 4.1 The quantum adder

- 4.1.1 The quantum full-adder

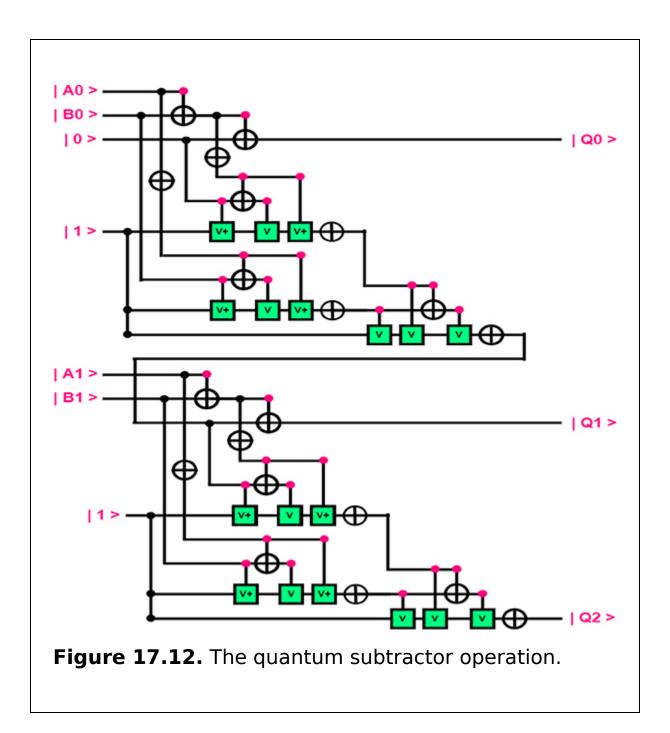

- 4.2 The quantum subtractor

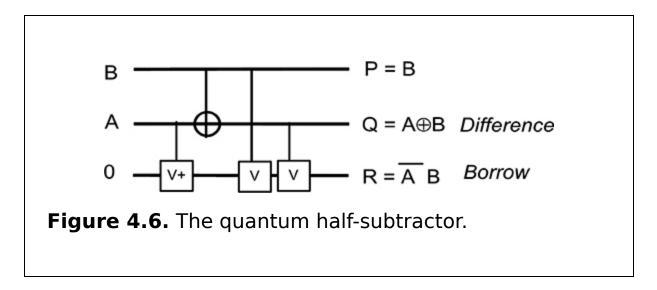

- 4.2.1 The quantum half-subtractor

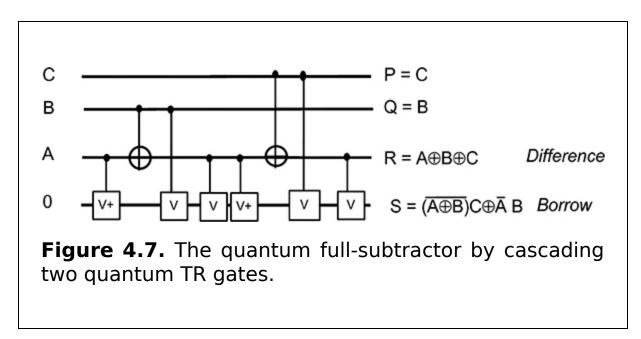

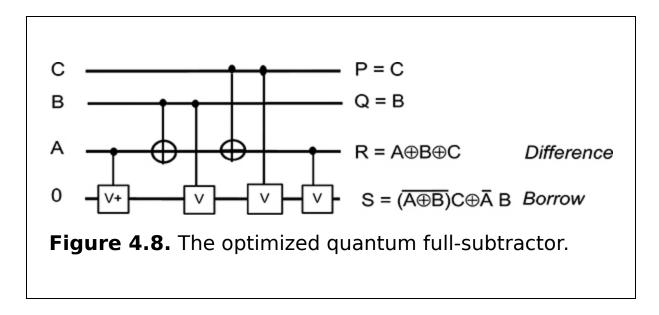

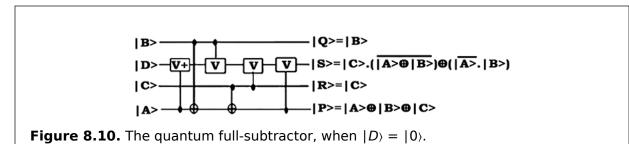

- 4.2.2 The quantum full-subtractor

- 4.3 Summary

Critical thinking questions

References

#### 5 The quantum multiplexer and demultiplexer

- 5.1 The quantum multiplexer

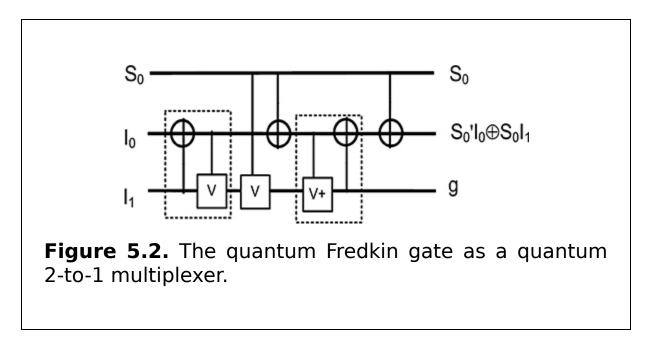

- 5.1.1 The quantum 2-to-1 multiplexer

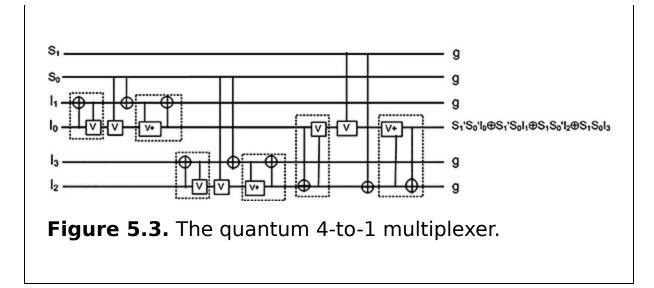

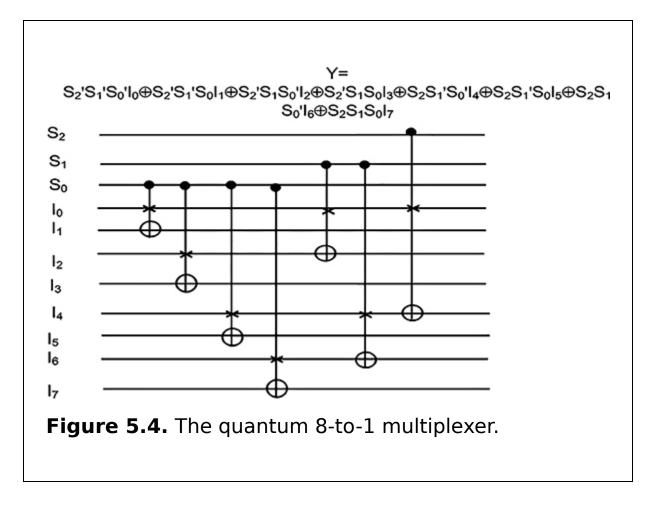

- 5.1.2 Quantum 4-to-1 multiplexer

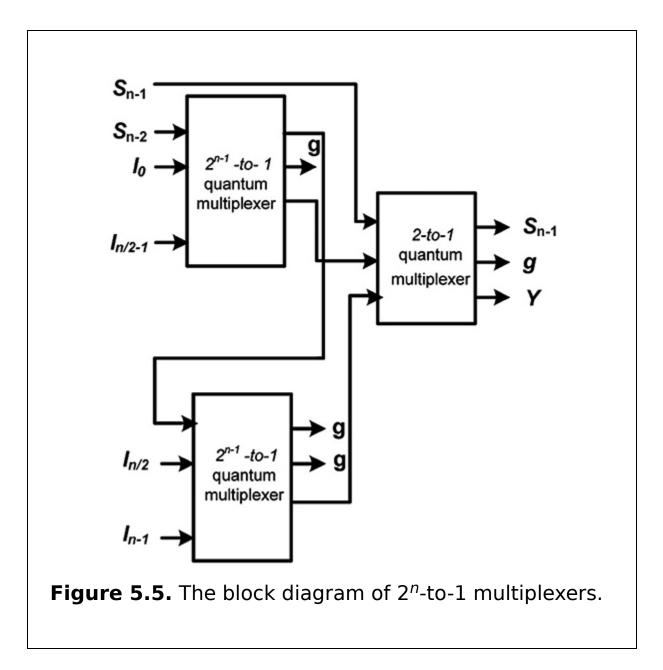

- 5.1.3 The quantum  $2^{n}$ -to-1 multiplexer

- 5.2 The quantum demultiplexer

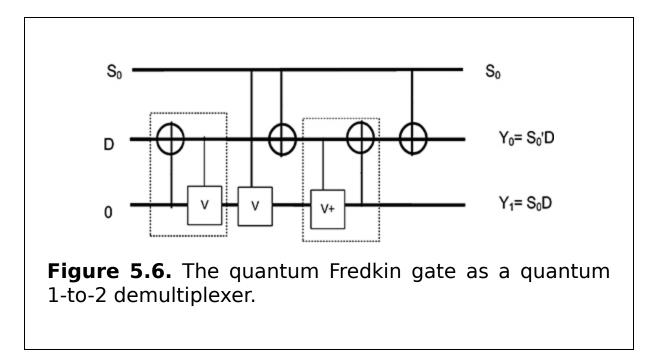

- 5.2.1 The quantum 1-to-2 demultiplexer

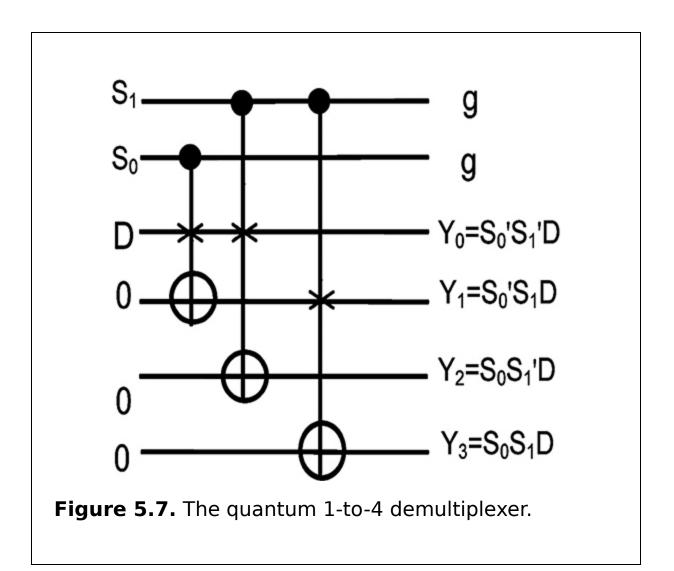

- 5.2.2 The quantum 1-to-4 demultiplexer

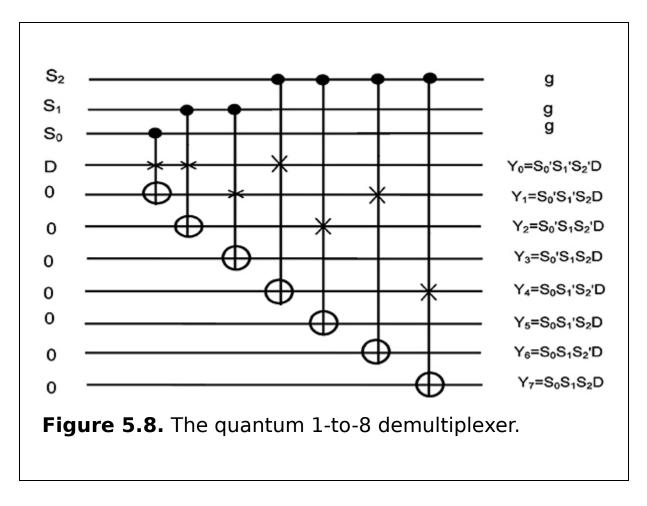

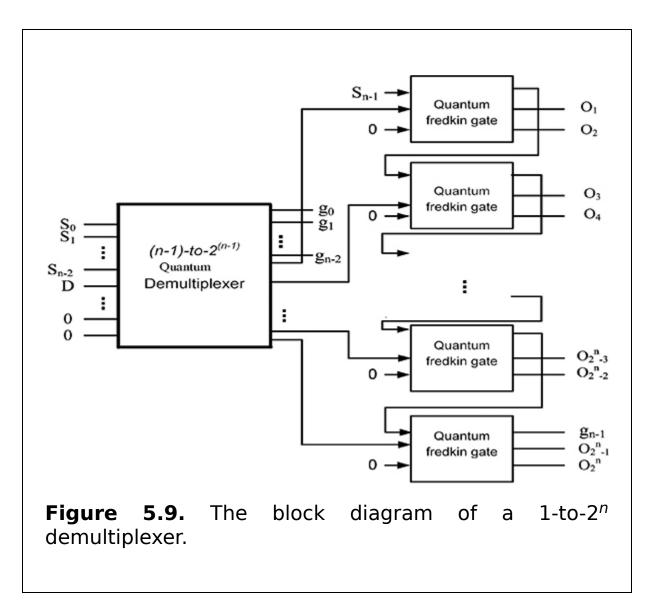

- 5.2.3 Quantum 1-to- $2^n$  demultiplexer

- 5.3 Summary

Critical thinking questions

References

#### 6 The quantum adder circuits

- 6.1 The quantum carry skip adder

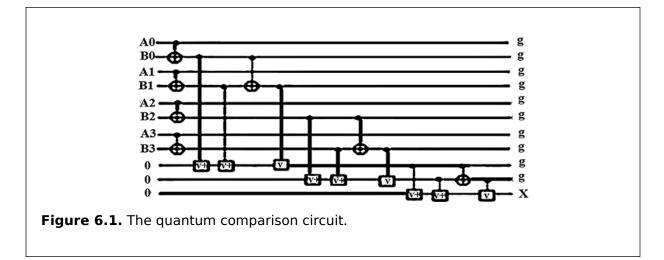

- 6.2 The quantum comparison circuit

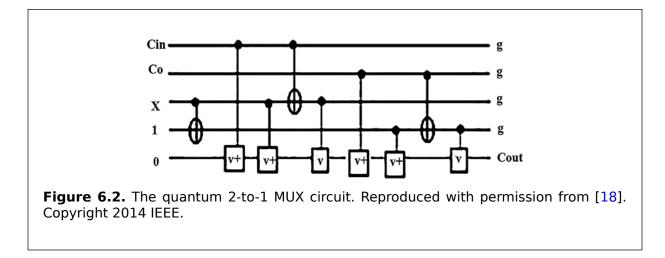

- 6.3 The quantum 2-to-1 multiplier circuit

6.4 The design of a quantum carry skip adder

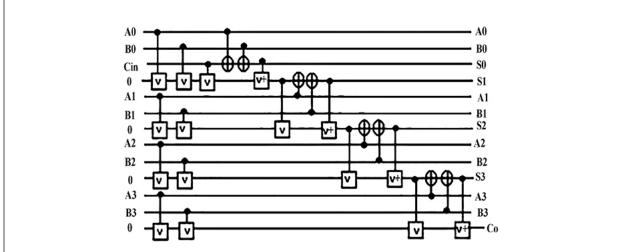

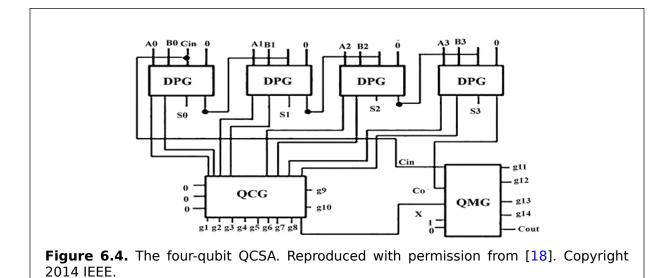

6.4.1 The four-qubit quantum carry skip adder

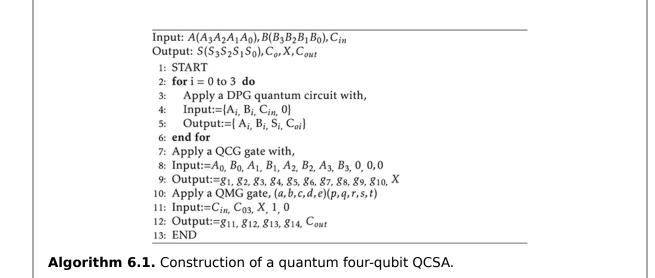

6.4.2 The *n*-qubit quantum carry skip adder

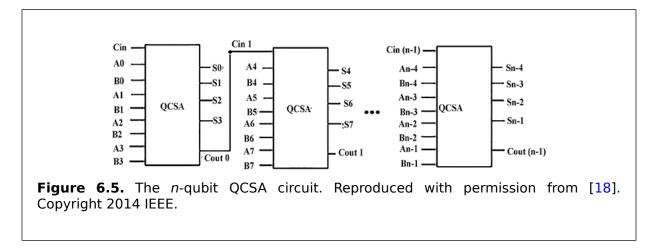

6.4.3 Calculation of the area and power of a quantum carry skip adder circuit

6.4.4 Complexity of the *n*-qubit quantum carry skip adder circuit

- 6.5 The quantum BCD adder

- 6.6 Summary

Critical thinking questions

References

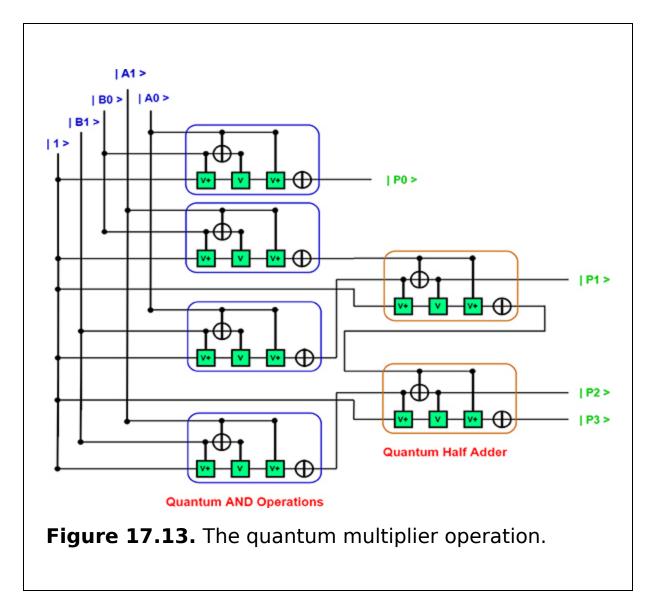

#### 7 The quantum multiplier-accumulator

- 7.1 The importance of a quantum multiplier-accumulator

- 7.2 The quantum multiplication technique

7.3 Reduction of the garbage outputs and ancillary inputs of quantum circuits

- 7.4 The design of a quantum multiplier circuit

- 7.4.1 The quantum ANDing circuit

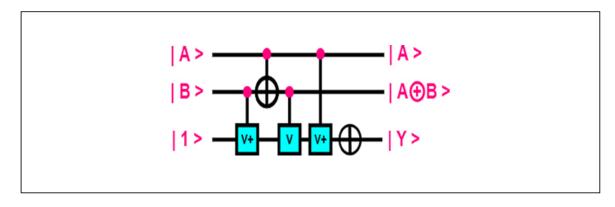

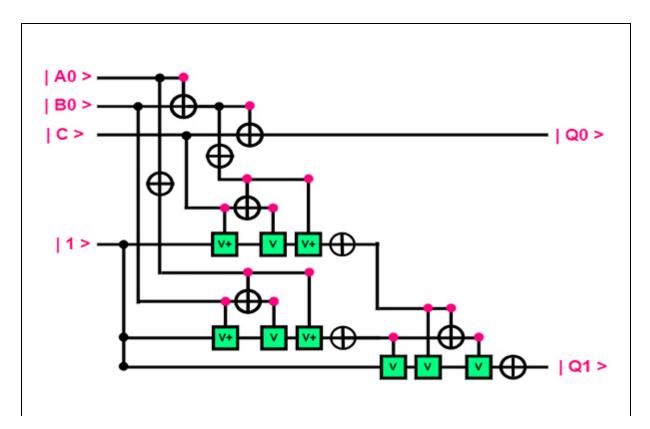

- 7.4.2 The quantum full-adder circuit

- 7.4.3 The  $n \times n$ -qubit quantum multiplier

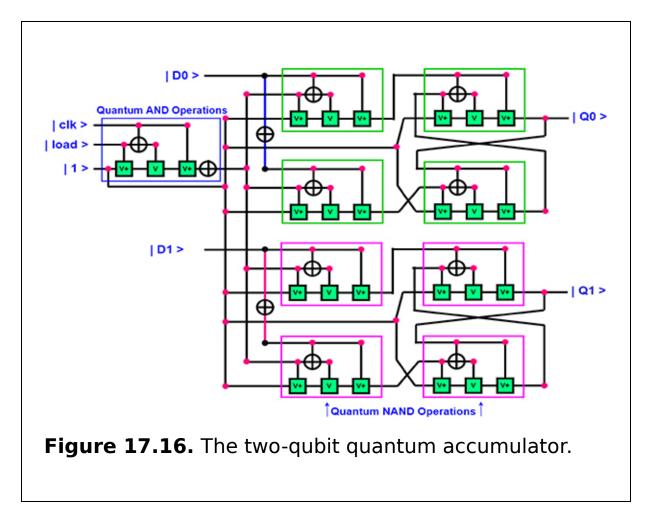

- 7.5 Accumulator

- 7.6 Summary

Critical thinking questions References

#### 8 The quantum divider

- 8.1 Division algorithms

- 8.1.1 Classical integer division algorithms

- 8.1.2 Quantum integer division algorithms

- 8.2 The importance of the quantum divider

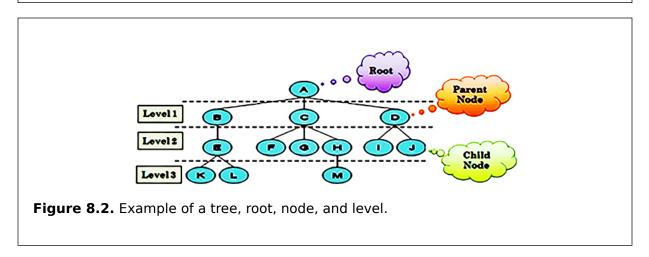

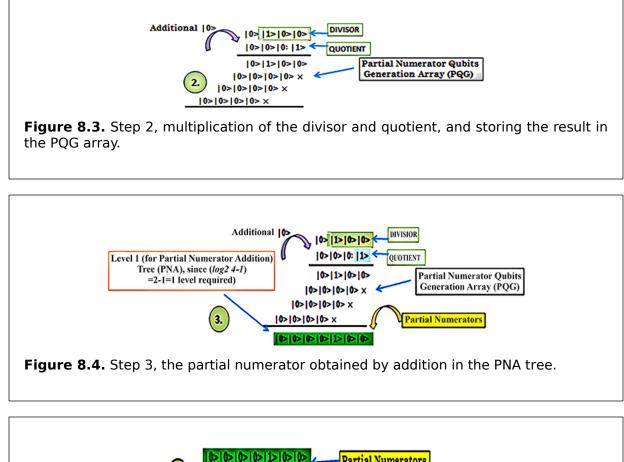

- 8.3 The tree-based quantum division technique

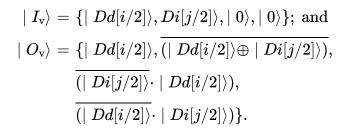

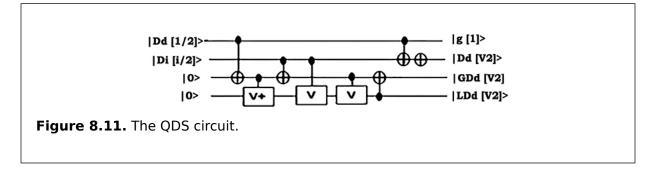

8.3.1 Definitions and properties of the division technique

8.3.2 The algorithm of the division technique

- 8.4 The design of a quantum divider circuit

- 8.4.1 A technique to minimize the number of ancillary inputs in the quantum circuit realization

8.4.2 The components of the quantum divider circuit

8.5 Summary

Critical thinking questions

References

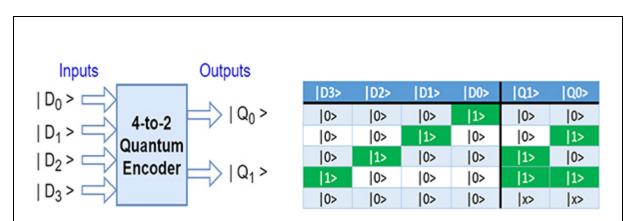

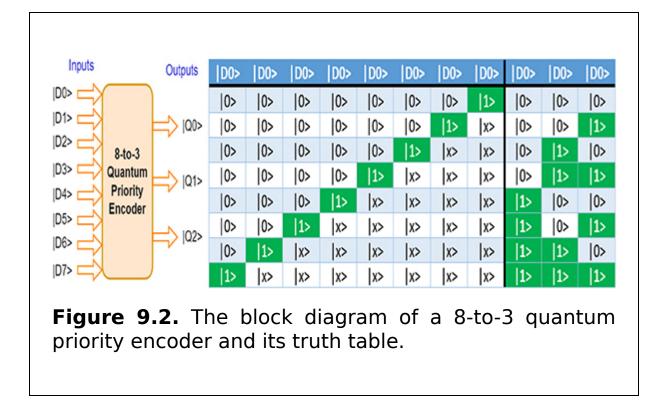

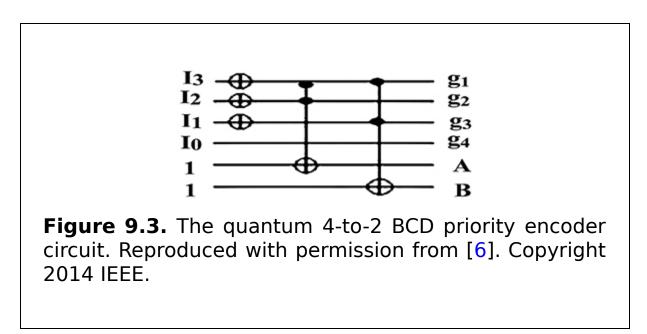

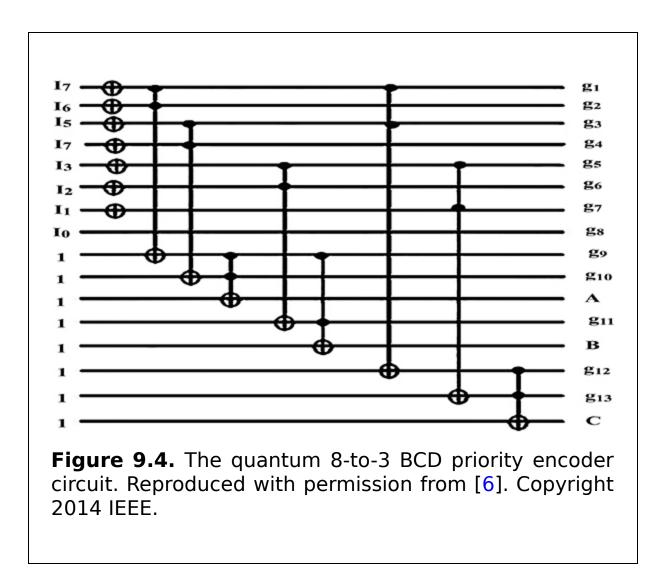

#### 9 The quantum BCD priority encoder

- 9.1 The properties of a quantum encoder

- 9.2 The design of a quantum BCD priority encoder circuit9.2.1 The quantum BCD priority encoder circuit

- 9.2.2 Analysis of the properties of the encoder circuit

- 9.3 Summary

Critical thinking questions

References

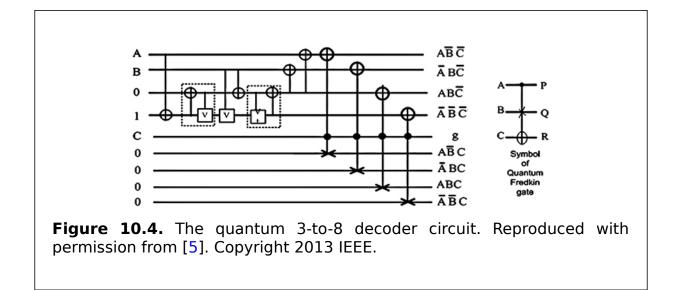

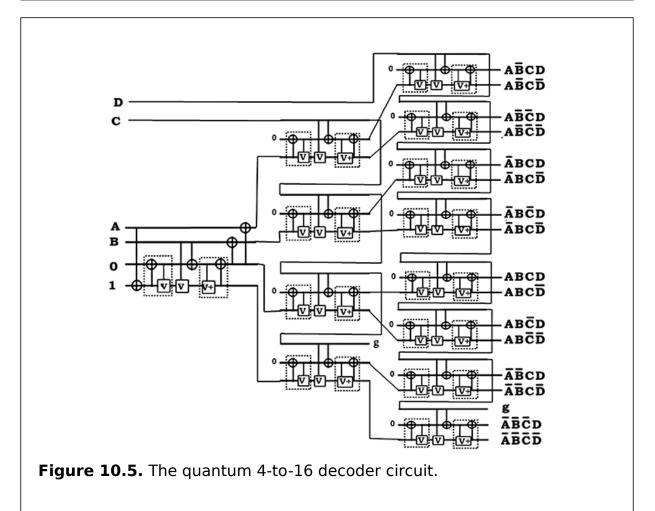

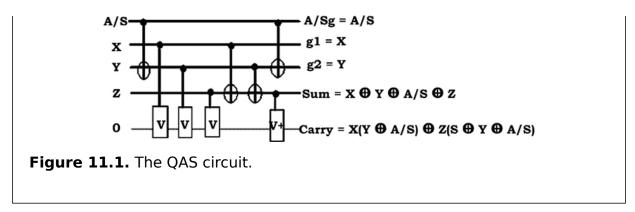

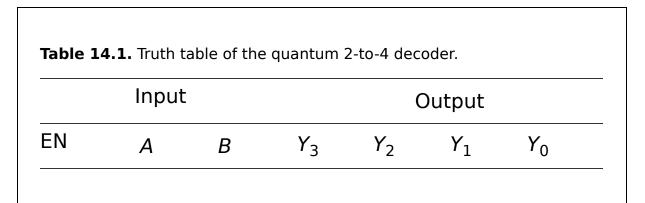

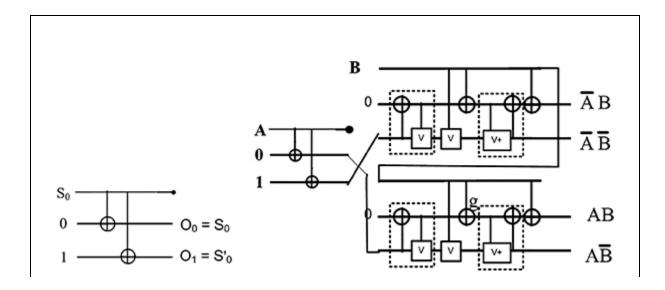

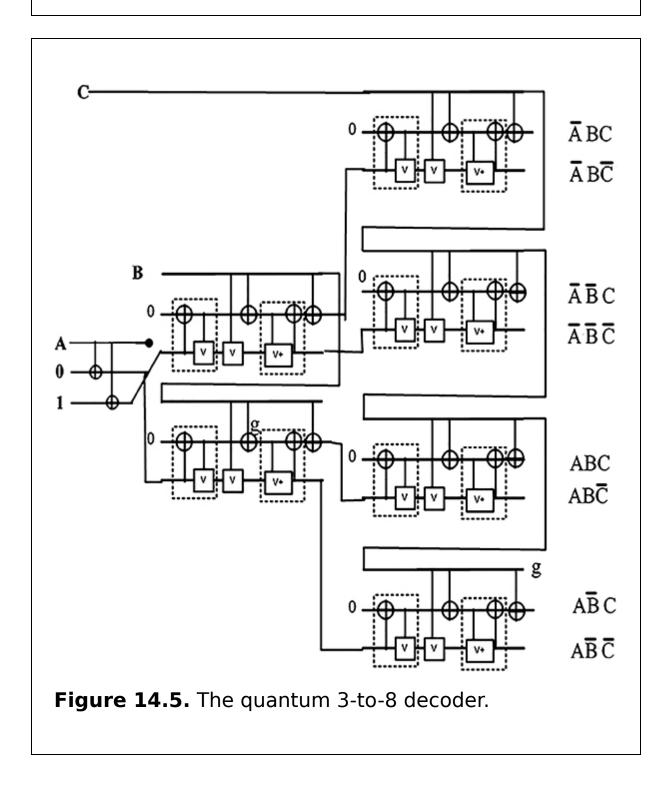

#### **10** The quantum decoder

10.1 The characteristics of a quantum decoder

10.2 The design of a quantum decoder

- 10.2.1 The quantum decoder circuit

- 10.2.2 Analysis of the properties of the circuits

- 10.3 Summary Critical thinking questions References

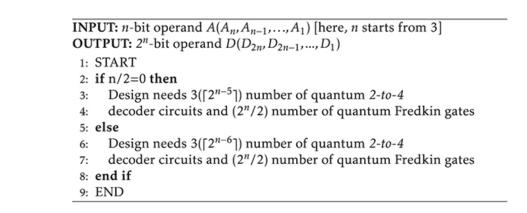

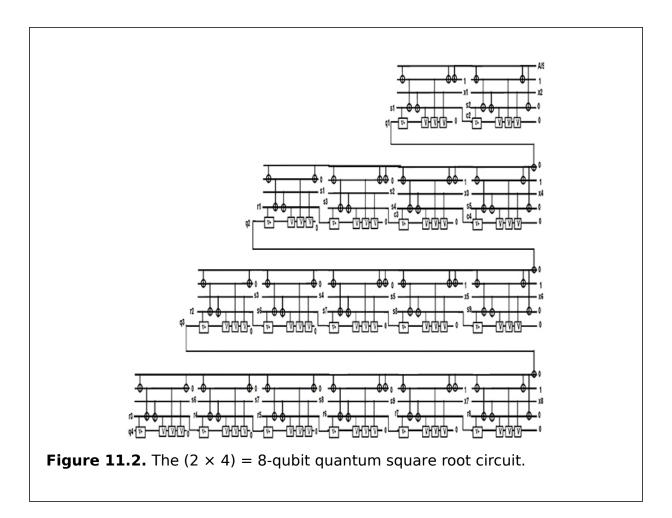

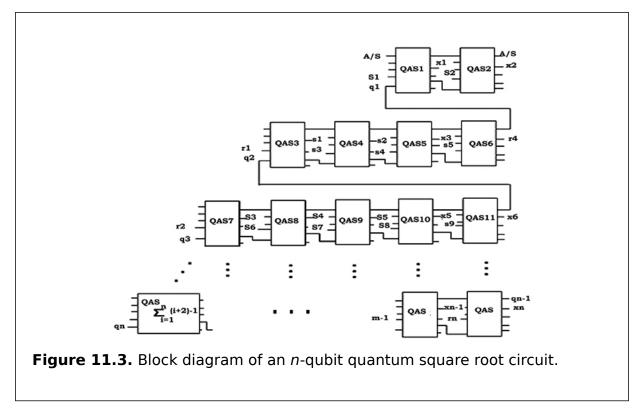

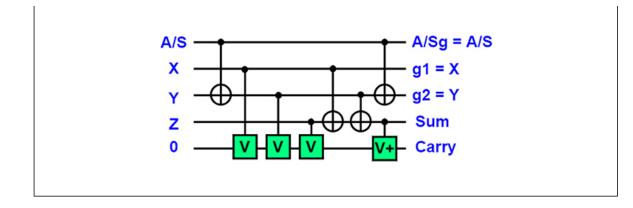

#### **11** The quantum square root circuit

- 11.1 The properties of a quantum square root function

- 11.2 The design of a quantum square root circuit

- 11.2.1 The quantum adder/subtractor circuit

- 11.2.2 The quantum square root circuit

11.2.3 Analysis of the properties of the quantum circuit

11.3 Summary

Critical thinking questions

References

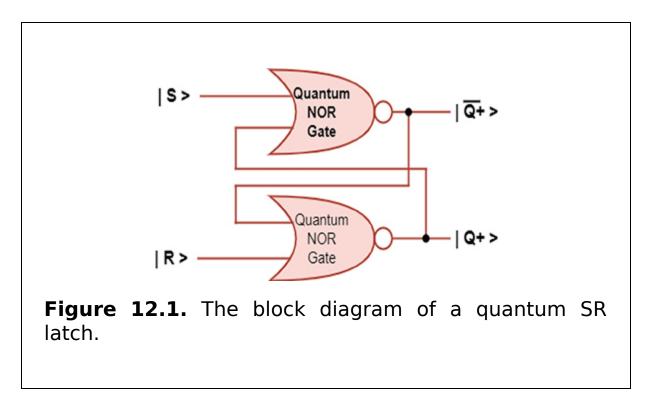

#### **12 Quantum latches and counter circuits**

- 12.1 The properties of quantum latches

- 12.2 The design of quantum latches

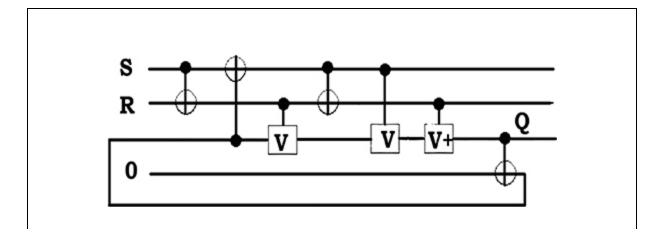

- 12.2.1 The quantum SR latch

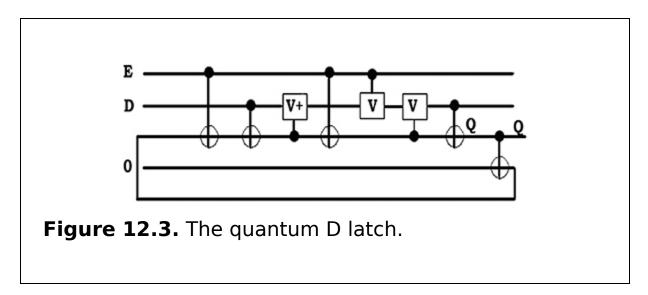

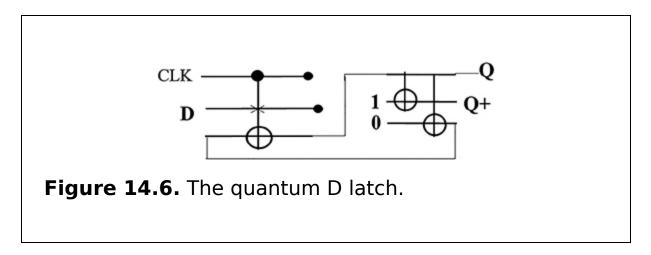

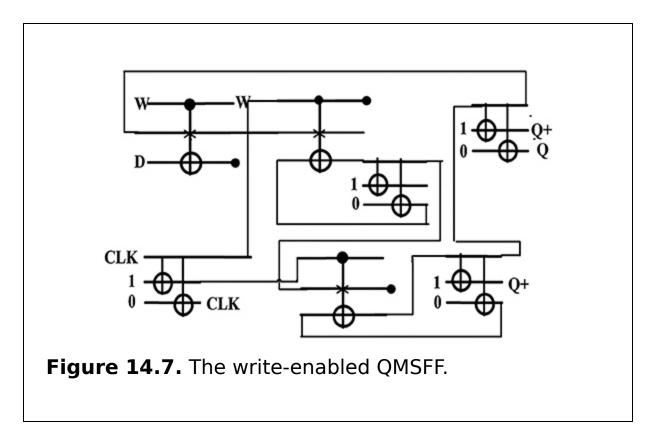

- 12.2.2 The quantum D latch

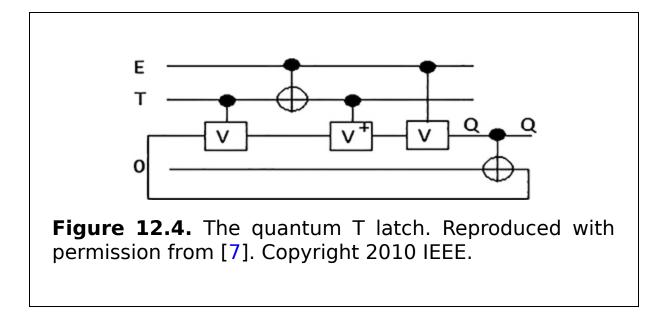

- 12.2.3 The quantum T latch

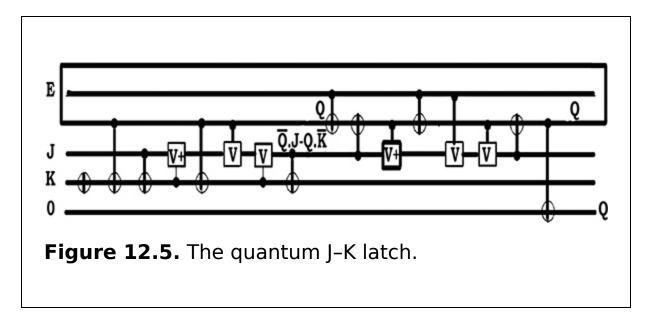

- 12.2.4 The quantum J-K latch

- 12.3 The properties of quantum counter circuits

12.4 The design of quantum counters

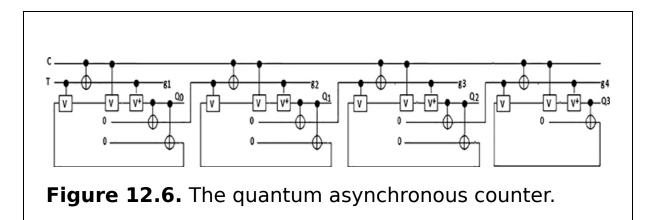

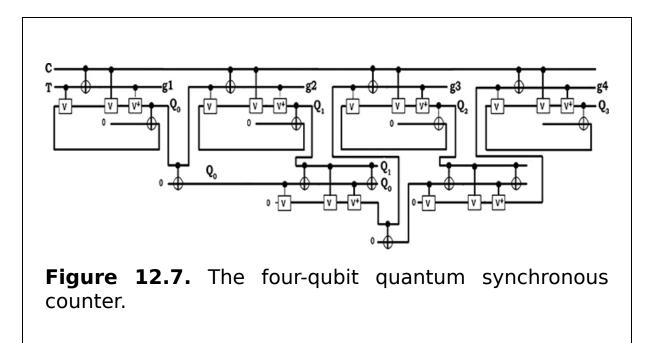

12.4.1 The quantum asynchronous counter

12.4.2 The quantum synchronous counter

12.5 Summary Critical thinking questions References

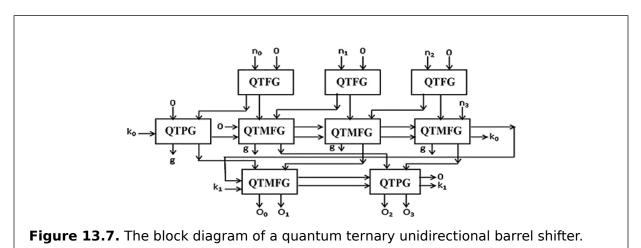

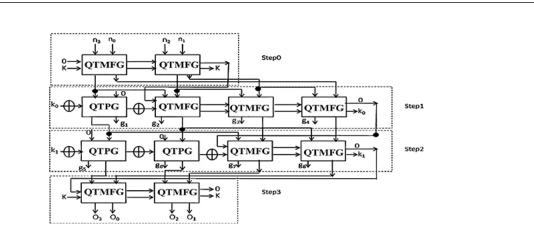

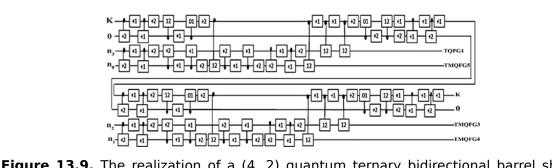

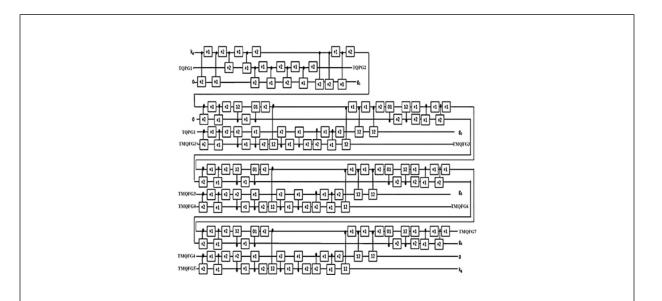

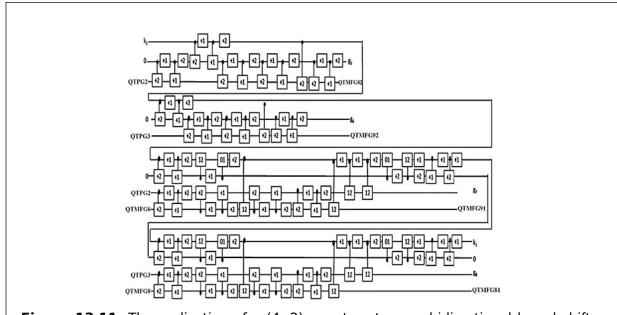

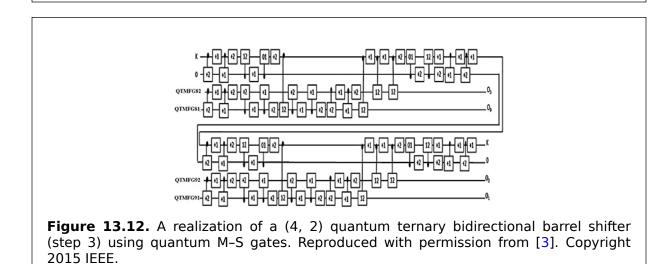

#### **13** The quantum controlled ternary barrel shifter

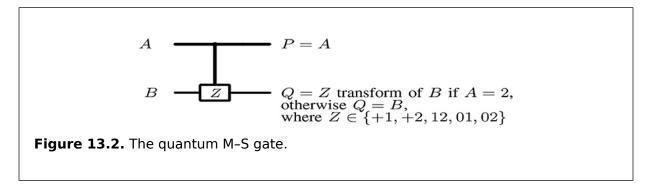

13.1 Ternary quantum gates

13.1.1 The quantum ternary Peres gate

- 13.1.2 The quantum ternary modified Fredkin gate

- 13.2 The properties of ternary quantum circuits

- 13.3 The quantum barrel shifter

- 13.3.1 Logical right shift

- 13.3.2 Arithmetic right shift

- 13.3.3 Right rotation

- 13.3.4 Logical left shift

- 13.3.5 Arithmetic left shift

- 13.3.6 Left rotation

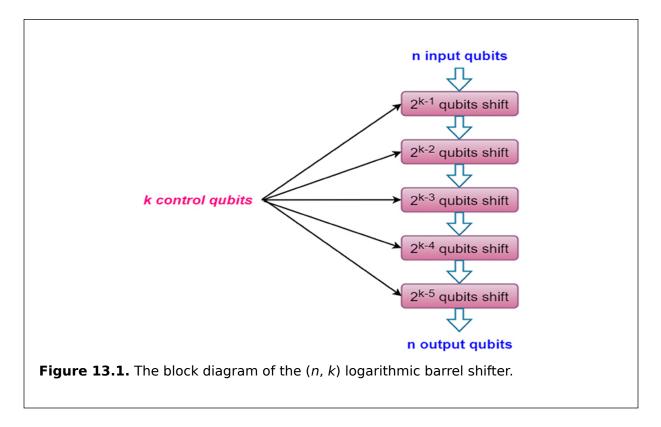

- 13.4 The design of a quantum ternary barrel shifter

- 13.4.1 The optimized quantum ternary barrel shifter

- 13.4.2 The properties of the designed circuit

- 13.5 Summary

Critical thinking questions

References

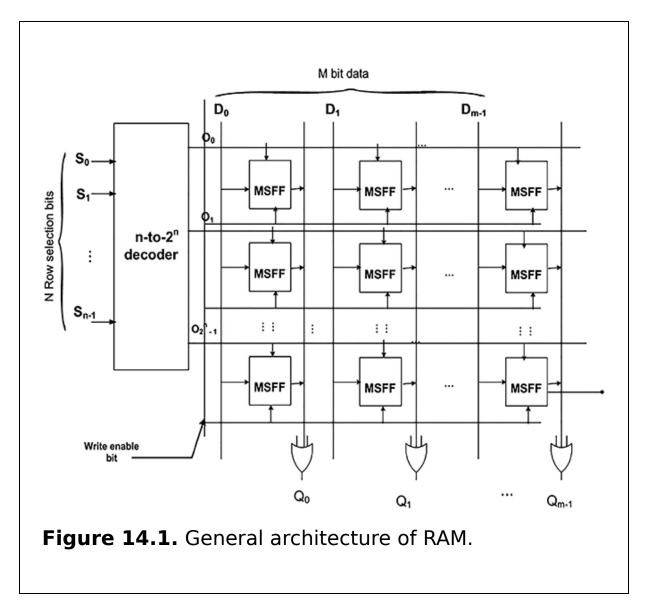

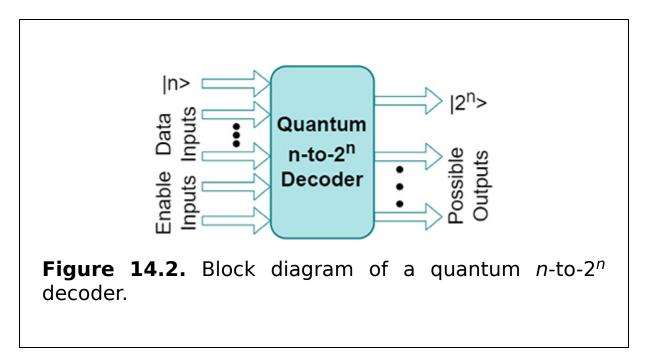

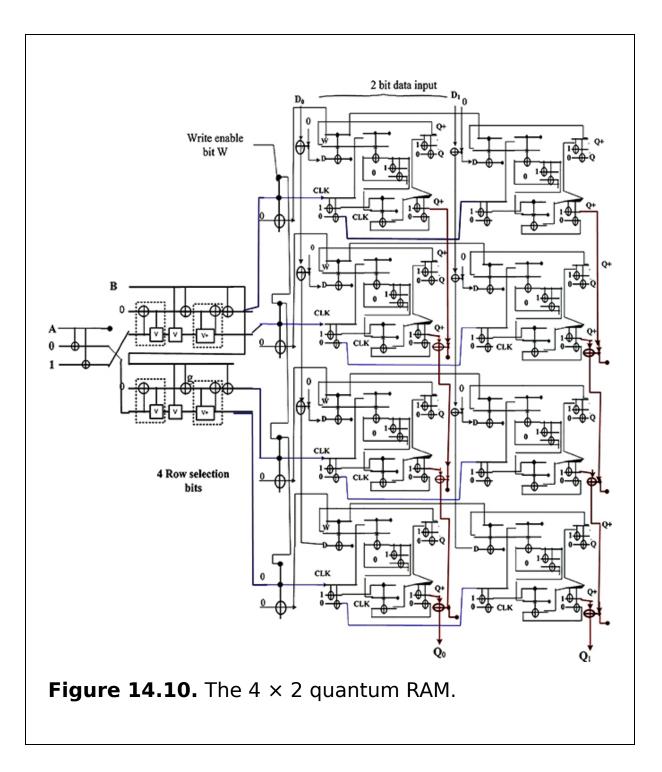

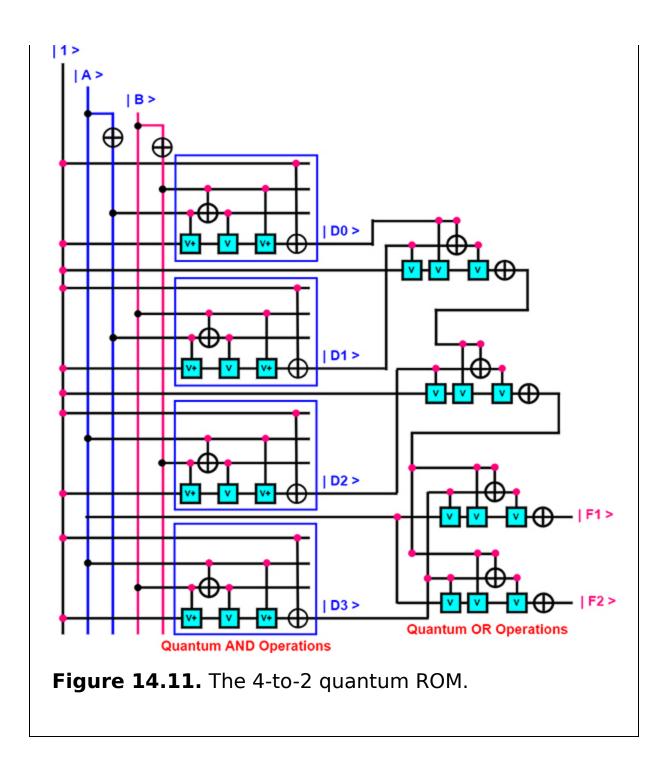

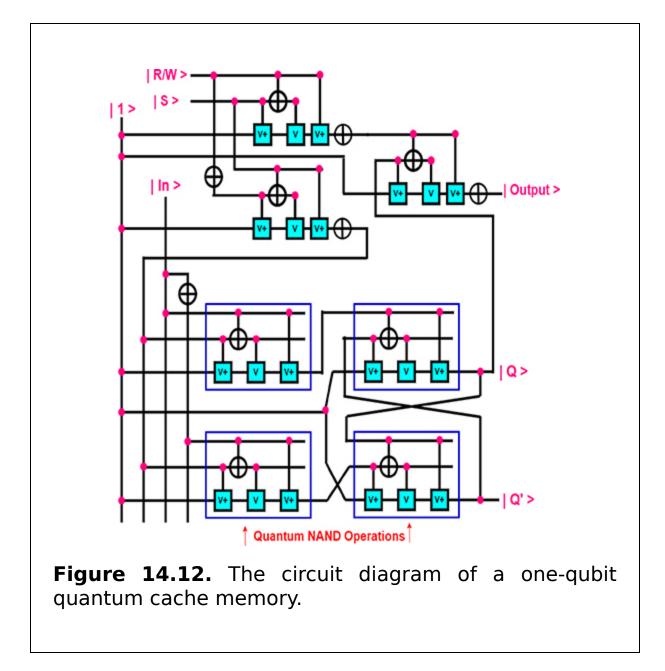

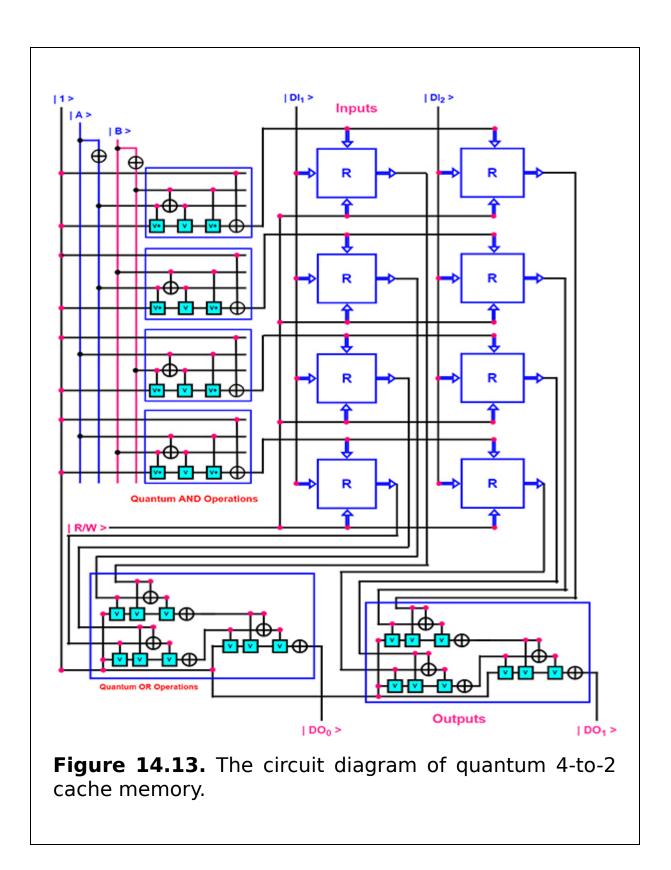

## 14 Quantum RAM, quantum ROM, and quantum cache memory

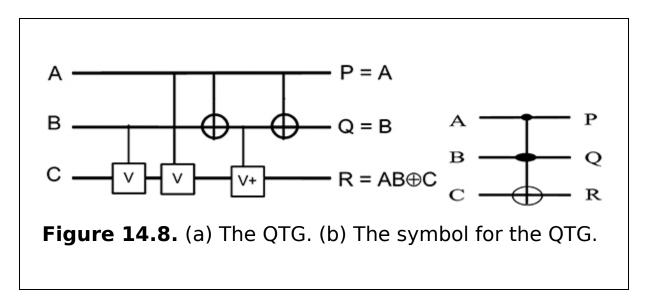

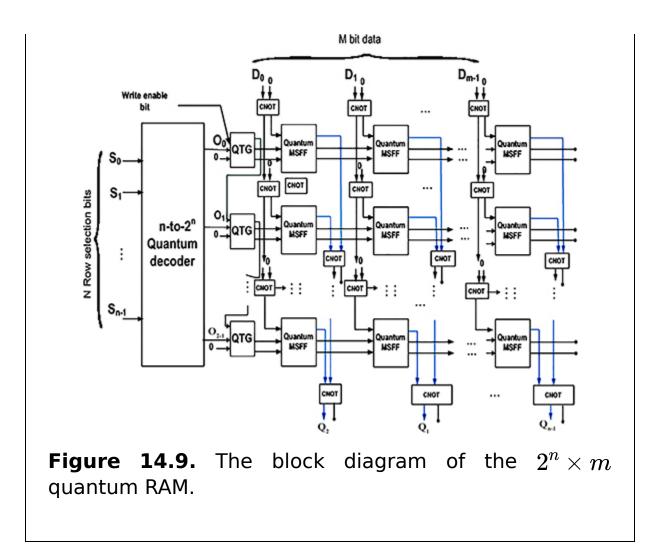

- 14.1 The quantum n-to- $2^n$  decoder

- 14.2 The quantum memory unit

- 14.3 The construction procedure of QRAM

- 14.4 Quantum ROM

- 14.5 Quantum cache memory

- 14.6 SummaryCritical thinking questionsReferences

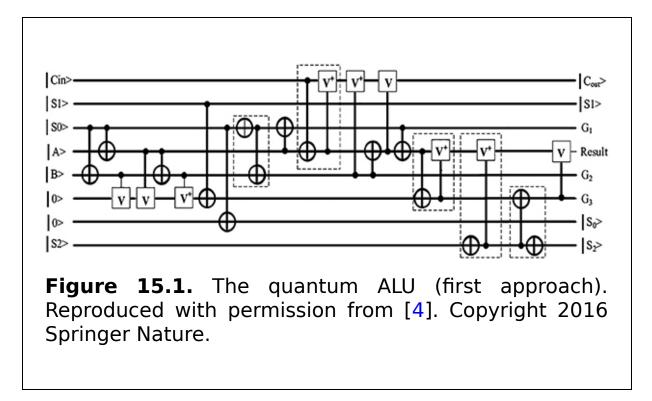

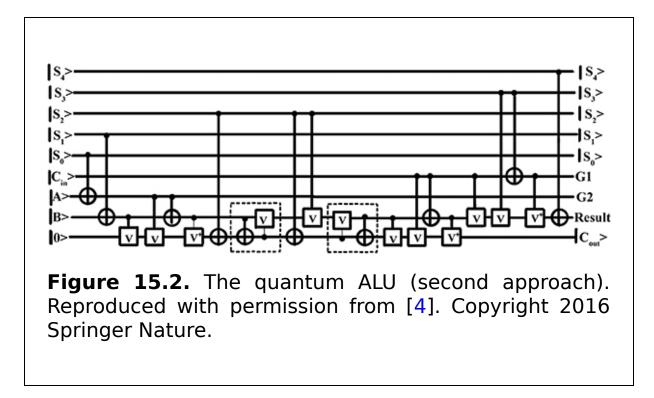

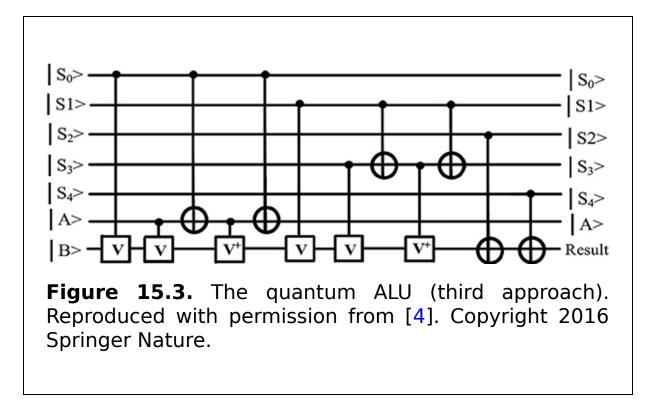

#### **15** The quantum arithmetic logic unit

- 15.1 The design of a quantum ALU

- 15.1.1 The first approach

- 15.1.2 The second approach

- 15.1.3 The third approach

- 15.2 Summary

Critical thinking questions

References

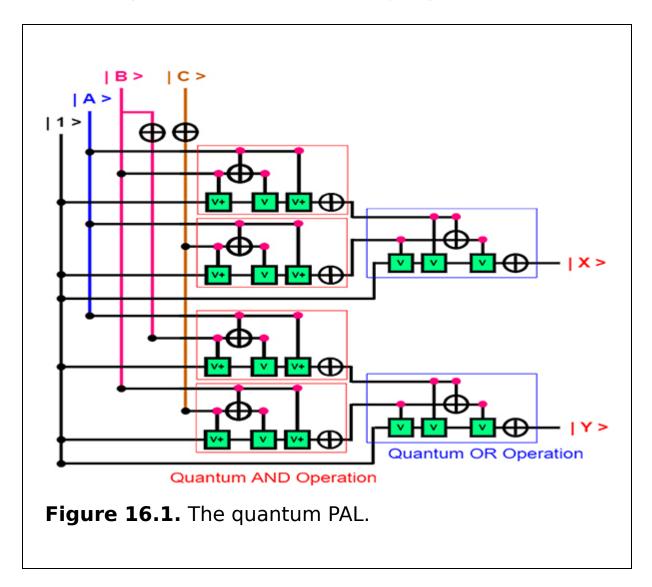

#### **16 Quantum programmable logic devices**

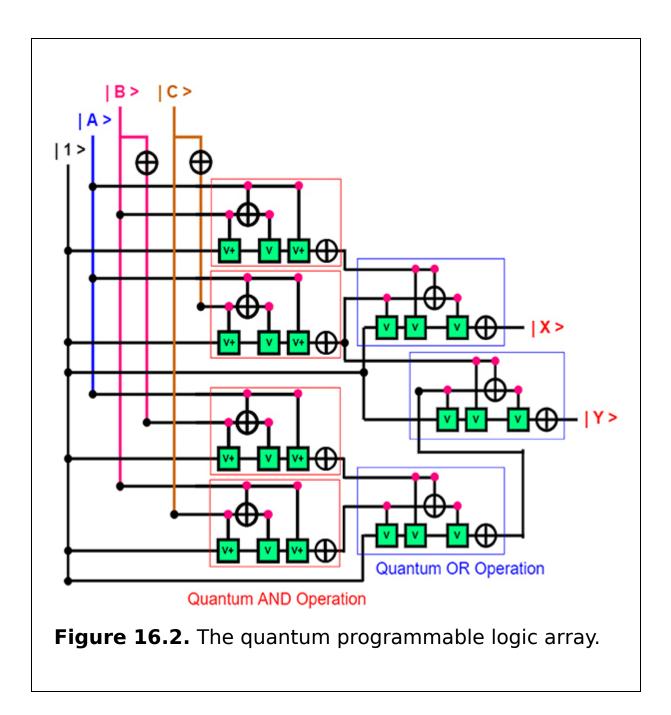

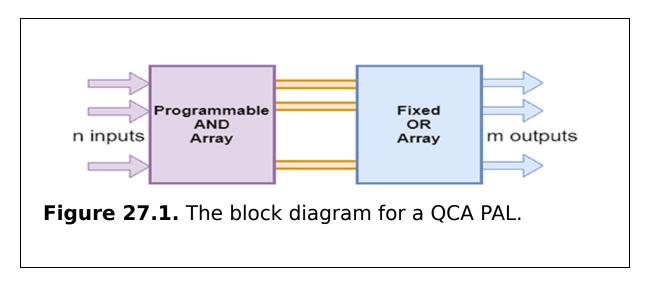

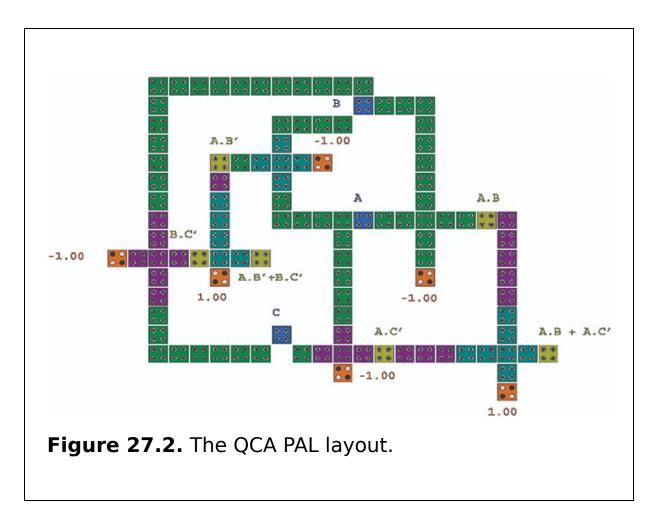

16.1 The quantum programmable array logic

16.1.1 The design procedure and working principles of quantum PAL

16.1.2 The importance and applications of quantum PAL

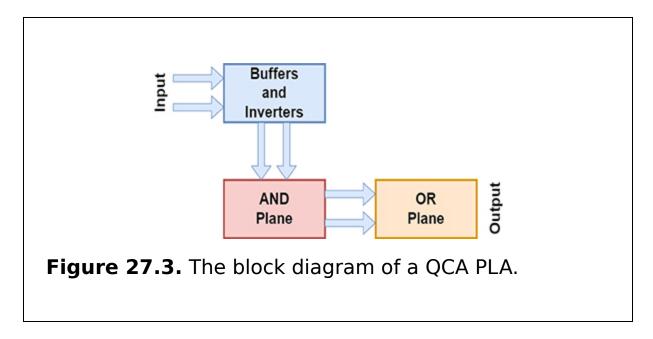

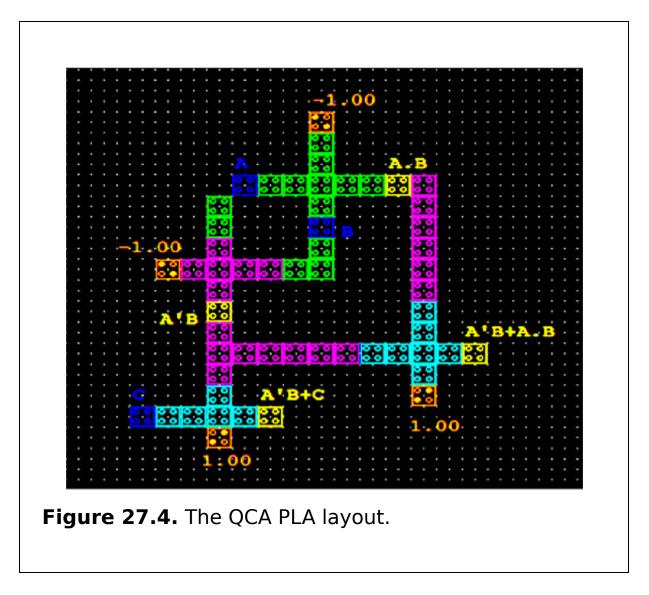

16.2 The quantum programmable logic array

16.2.1 The design procedure and working principles of quantum PLAs

16.2.2 The importance and applications of quantum PLAs

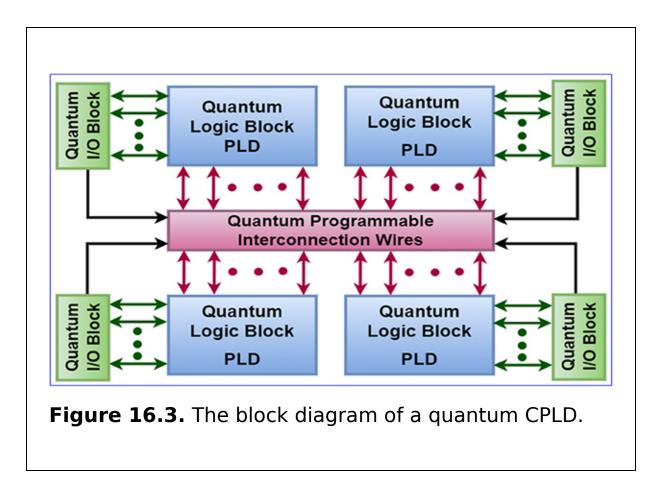

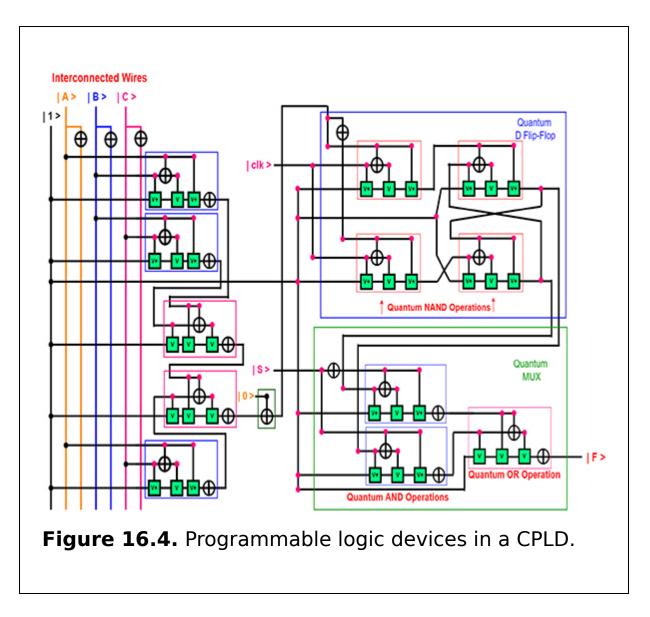

16.3 The quantum complex programmable logic device

16.3.1 The design procedure and working principles of quantum CPLDs

16.3.2 The importance and applications of quantum CPLD

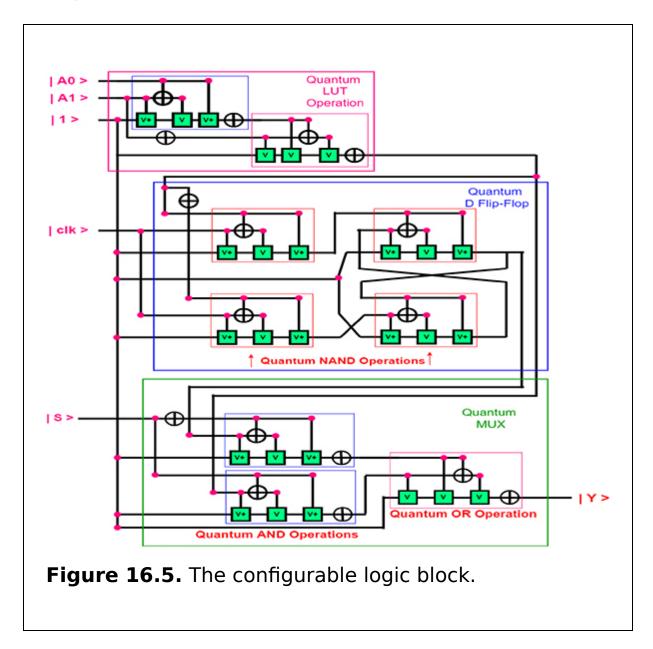

16.4 The quantum field-programmable gate array

16.4.1 The design procedure and working principles of quantum FPGAs

16.4.2 The importance and applications of FPGAs

16.5 Summary Critical thinking questions

References

- **17** The quantum processor circuit

- 17.1 Introduction

- 17.2 Basic definitions

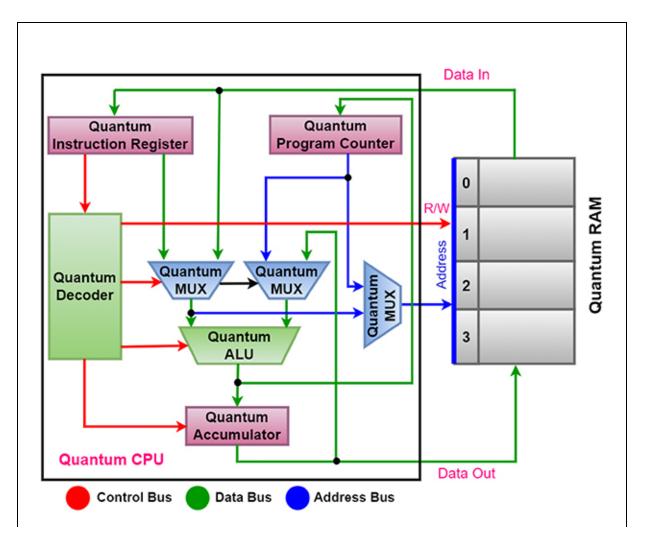

- 17.3 The block diagram of a quantum processor

- 17.4 The basic components of a quantum processor

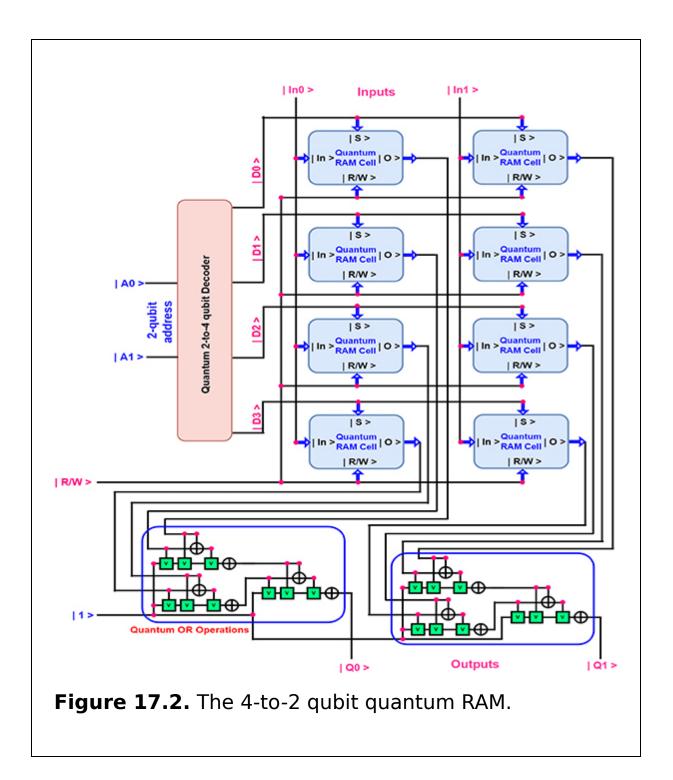

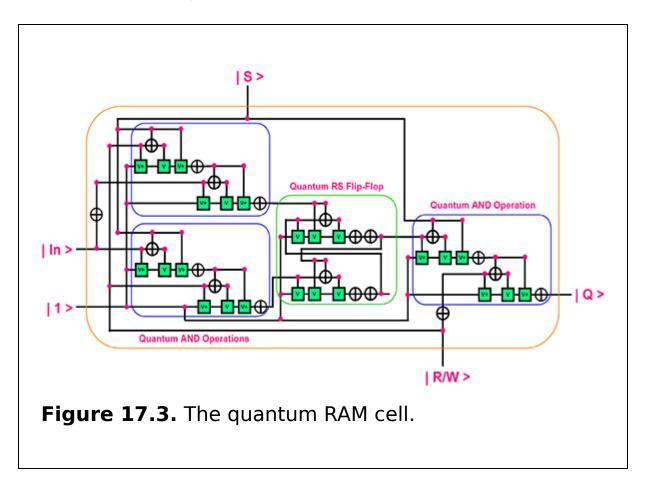

- 17.4.1 The quantum RAM

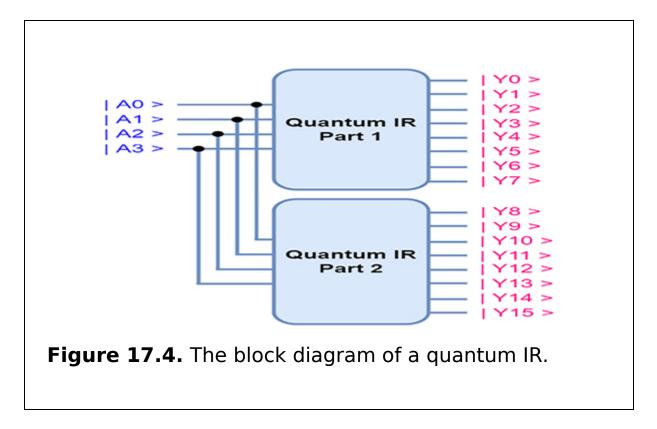

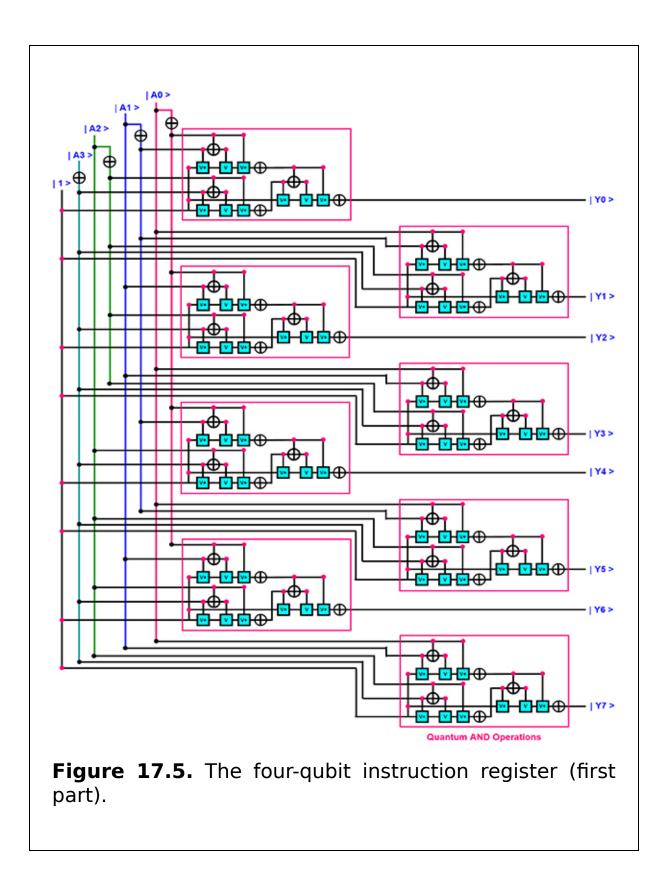

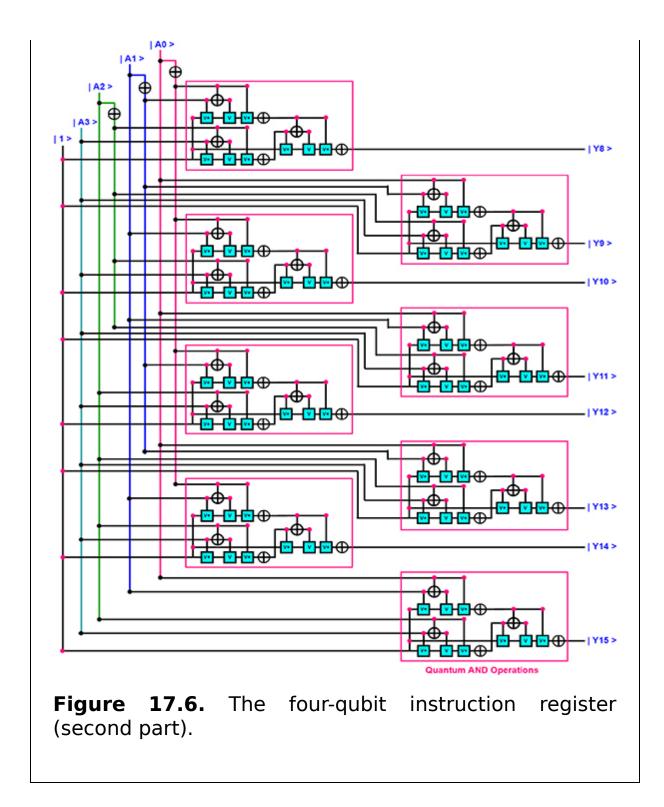

- 17.4.2 The quantum instruction register

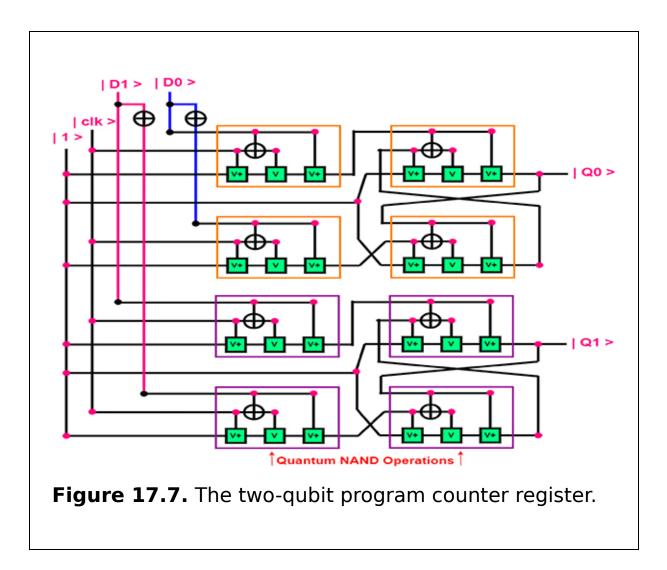

- 17.4.3 The quantum program counter

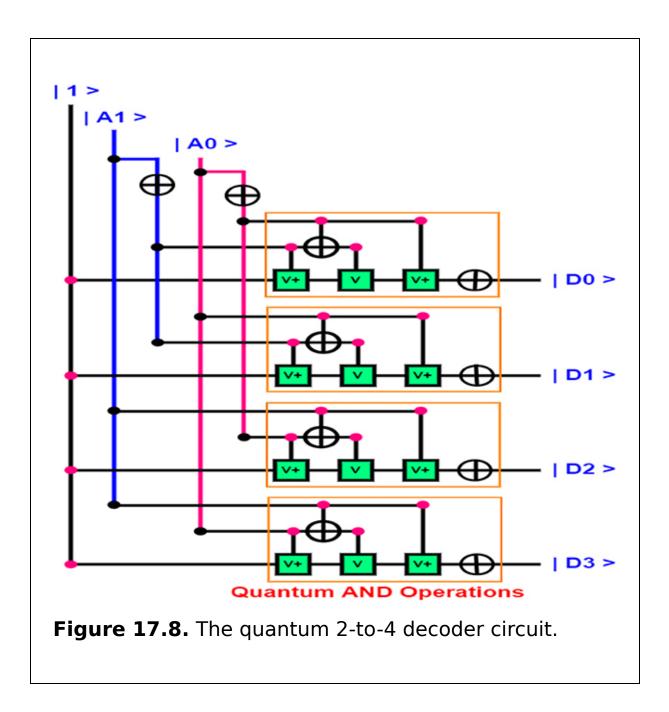

- 17.4.4 The quantum decoder

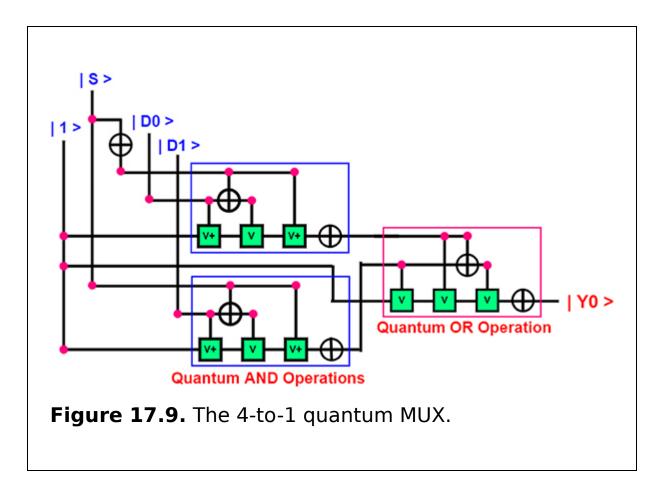

- 17.4.5 The quantum multiplexer

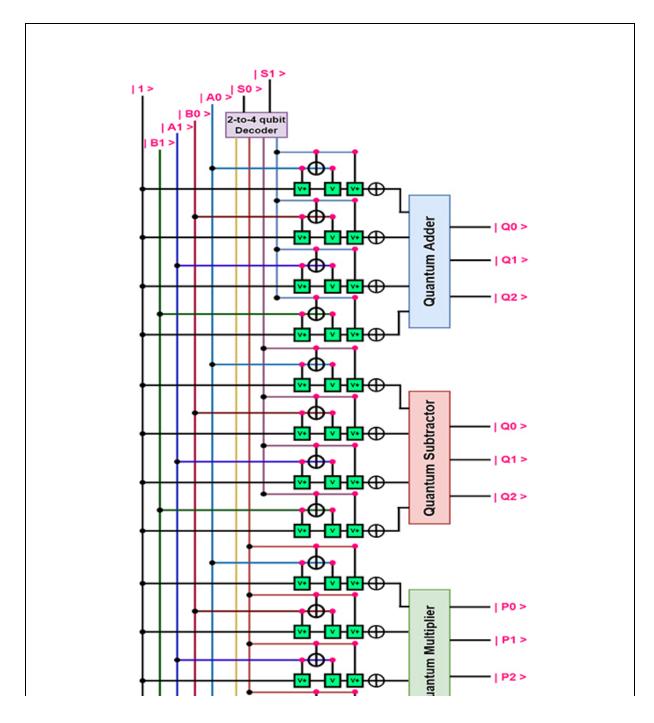

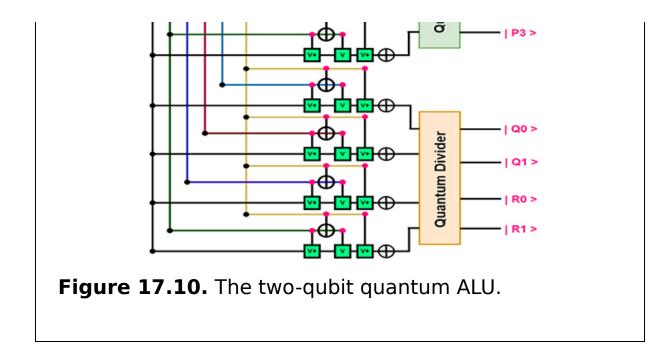

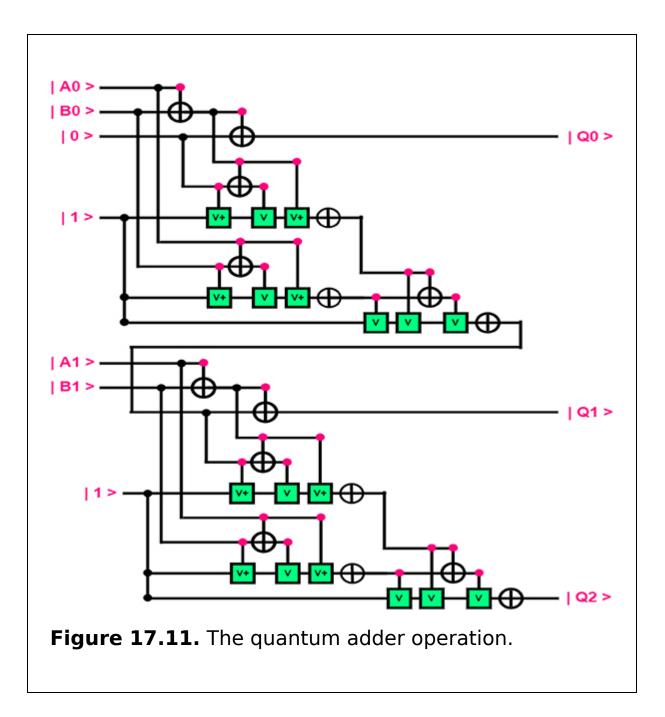

- 17.4.6 The quantum arithmetic logic unit

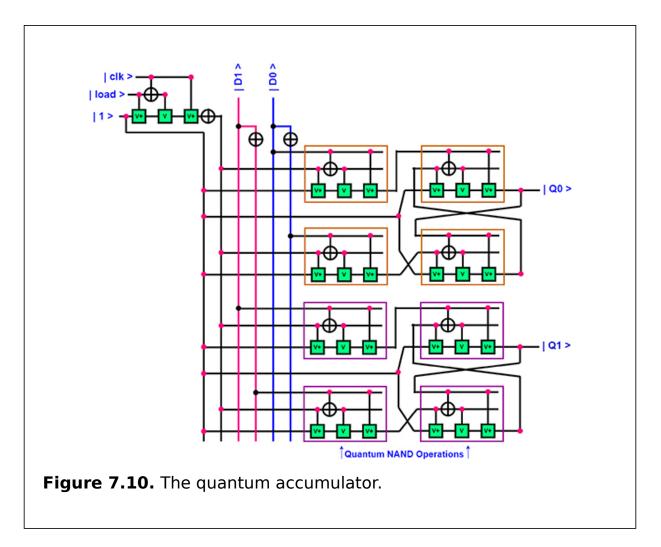

- 17.4.7 The quantum accumulator

- 17.5 Applications

- 17.6 Summary Critical thinking questions References

#### **18** Applications of quantum computing technology

- 18.1 Optimization

- 18.1.1 The Roswell Park Cancer Institute

- 18.1.2 Volkswagen group

- 18.1.3 Recruit Communications

- 18.2 Machine learning

- 18.2.1 QxBranch

- 18.2.2 Los Alamos National Laboratory

- 18.2.3 NASA

- 18.3 Biomedical simulations

- 18.4 Financial services

- 18.5 Computational chemistry

- 18.6 Logistics and scheduling

- 18.7 Cyber security

- 18.8 Circuit, software, and system fault simulation

- 18.9 Weather forecasting

- 18.10 Summary

Critical thinking questions

References

#### Part II Quantum fault tolerance

#### **19 Quantum fault-tolerant circuits**

- 19.1 The need for quantum fault-tolerant circuits

- 19.2 The fault-tolerant quantum adder

- 19.2.1 The fault-tolerant full-adder

- 19.3 The fault-tolerant multiplier

- 19.3.1 The fault-tolerant signed multiplier

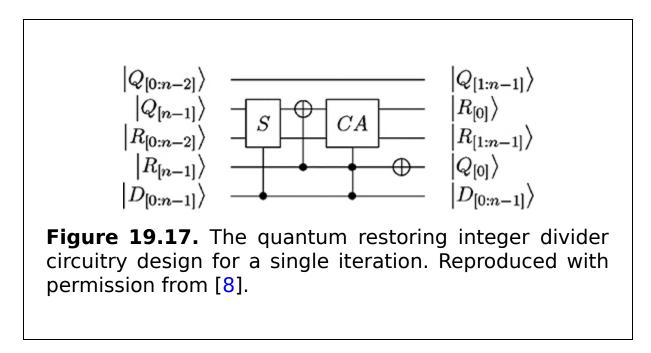

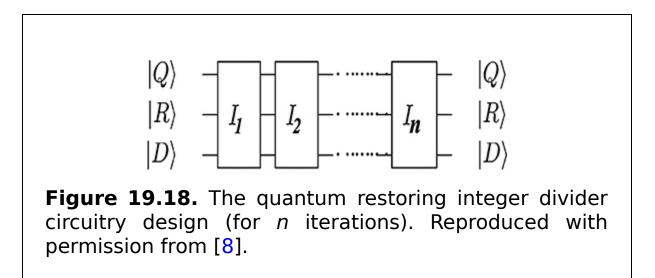

- 19.4 The quantum fault-tolerant integer divider

- 19.4.1 The restoring division algorithm

- 19.4.2 The subtractor module

- 19.4.3 The conditional addition operation module

- 19.4.4 Quantum restoring integer division circuitry

- 19.5 Summary

Critical thinking questions

References

#### Part III Quantum-dot cellular automata

#### 20 Quantum-dot cellular automata

- 20.1 Fundamentals of QCA circuits

- 20.1.1 Area

- 20.1.2 Delay

- 20.1.3 Kink energy

- 20.1.4 Power

- 20.1.5 Overall cost

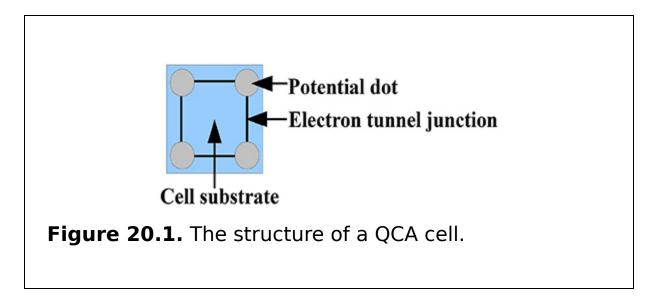

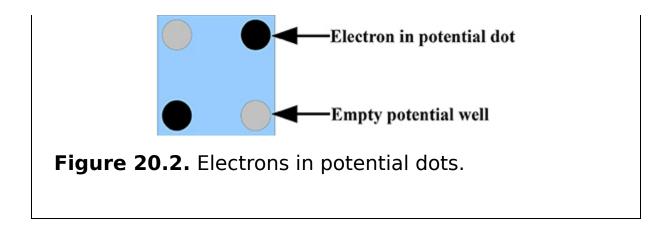

- 20.2 The QCA cell

- 20.3 Information and data propagation

- 20.4 Basic QCA elements and gates

- 20.4.1 The QCA majority voter

- 20.4.2 The QCA AND gate

- 20.4.3 The QCA OR gate

- 20.4.4 The QCA NOT gate

- 20.4.5 The QCA wire

- 20.5 The QCA clock

- 20.5.1 Special cell arrangements and symmetric cells

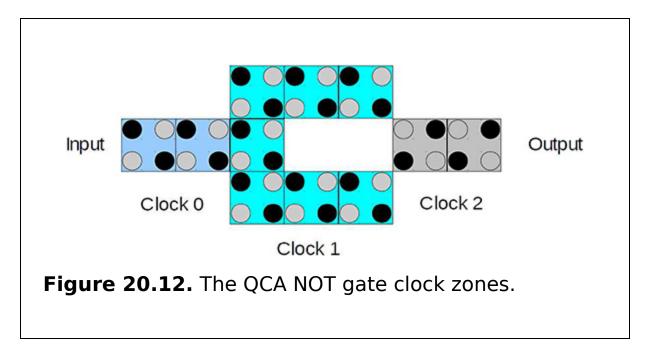

- 20.5.2 The NOT gate clock zones

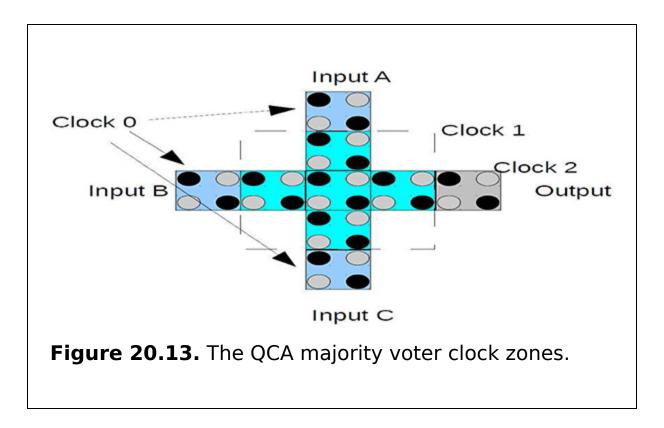

- 20.5.3 The majority voter clock zones

- 20.6 Summary

Critical thinking questions

References

#### 21 The QCA adder and subtractor

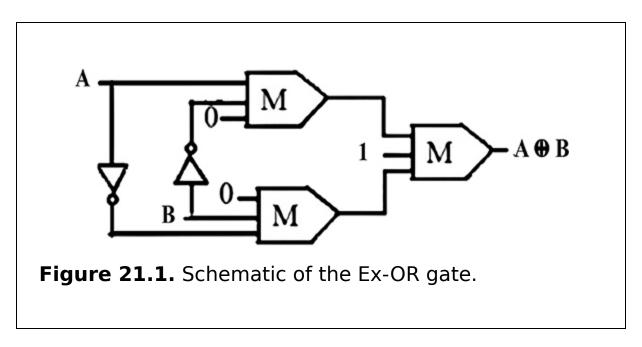

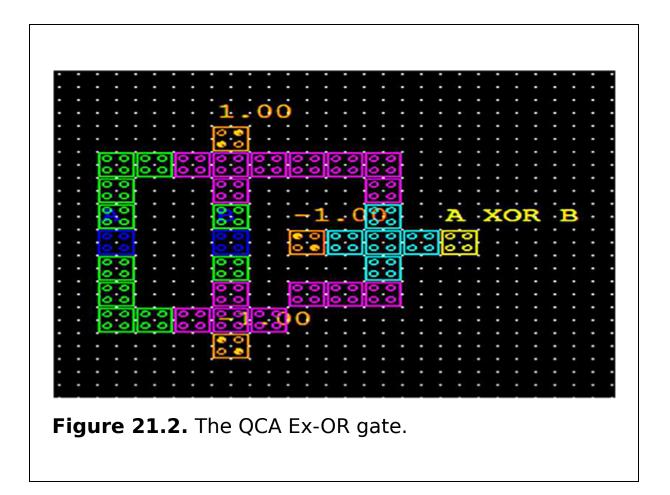

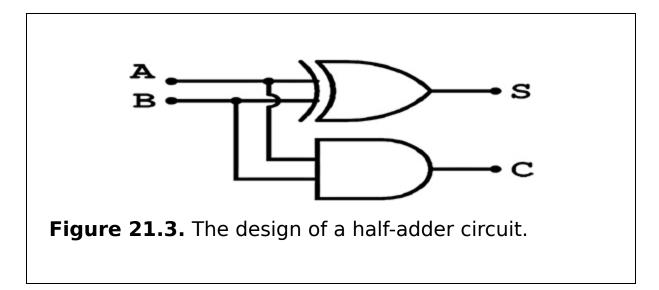

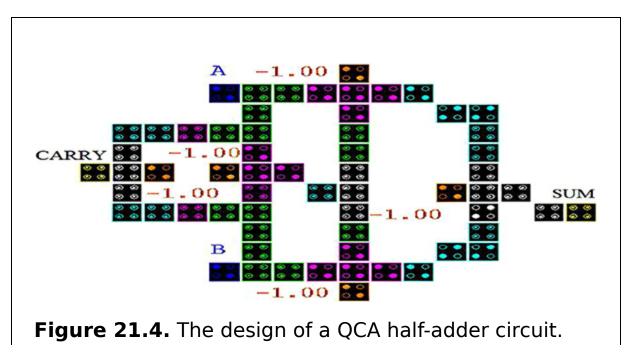

- 21.1 The Ex-OR gate

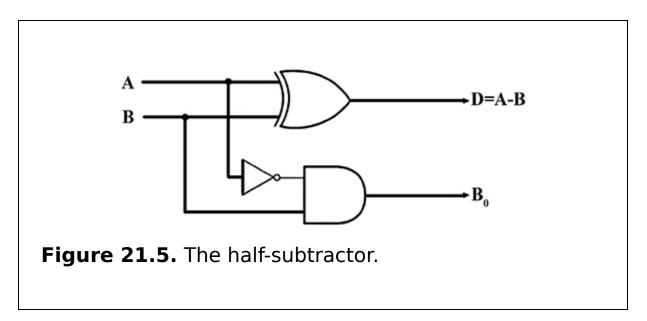

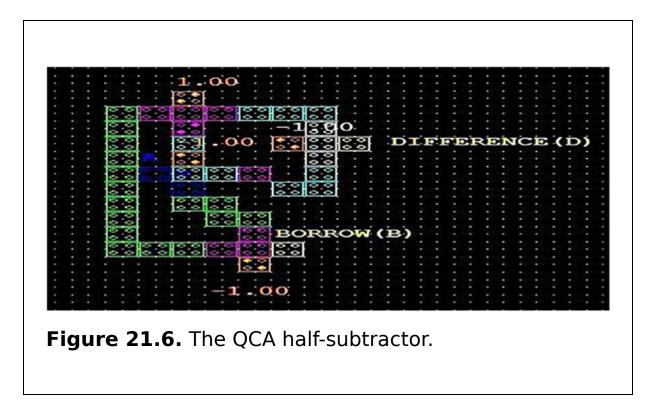

- 21.2 The QCA half-adder and -subtractor

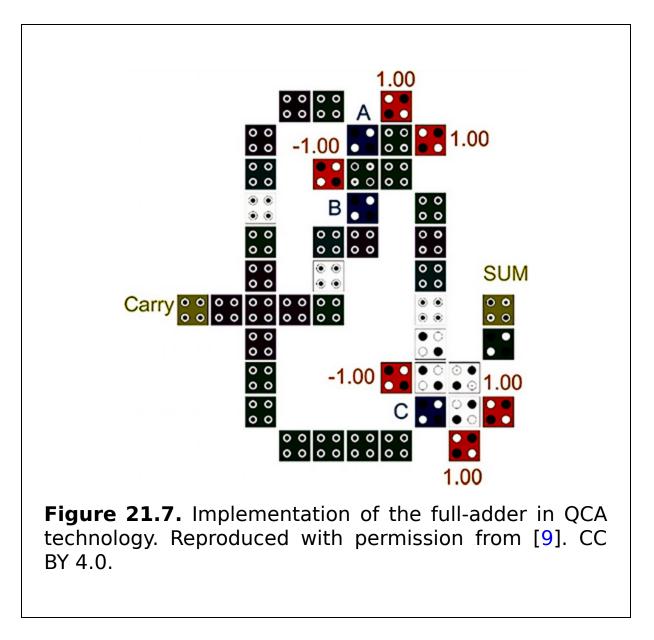

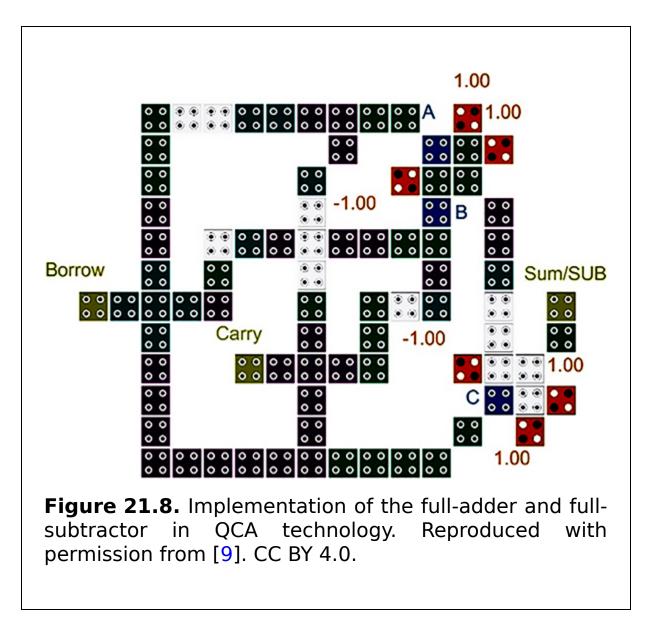

- 21.3 The QCA full-adder and full-subtractor

21.3.1 Implementation of the full-adder and fullsubtractor

21.4 Summary

Critical thinking questions

References

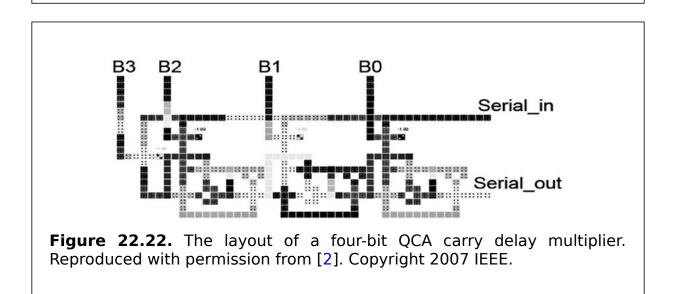

#### 22 The QCA multiplier and divider

- 22.1 The QCA multiplier

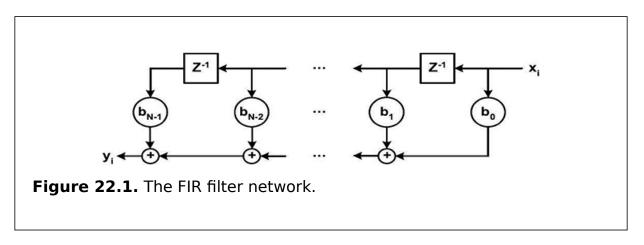

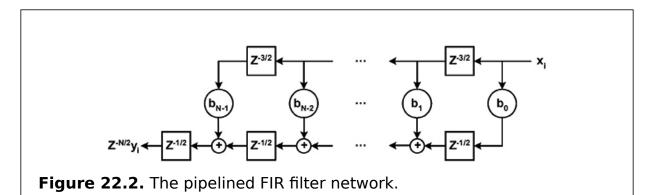

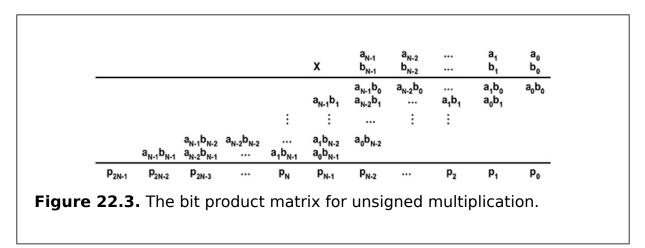

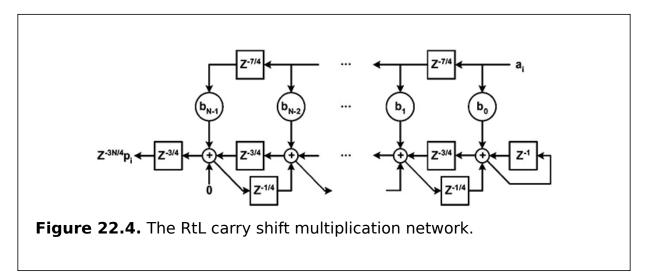

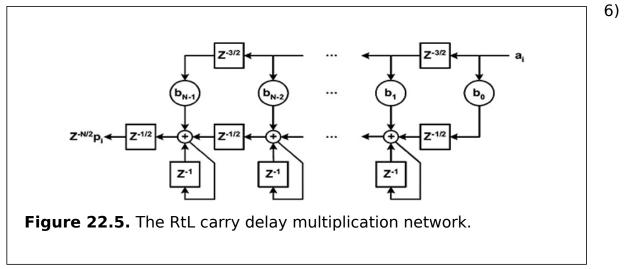

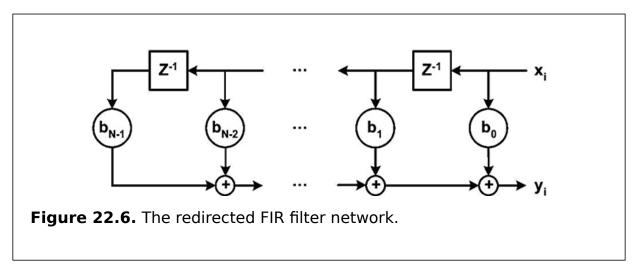

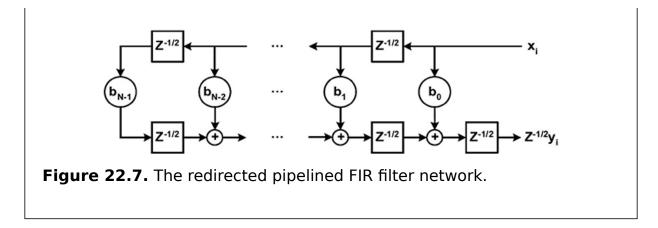

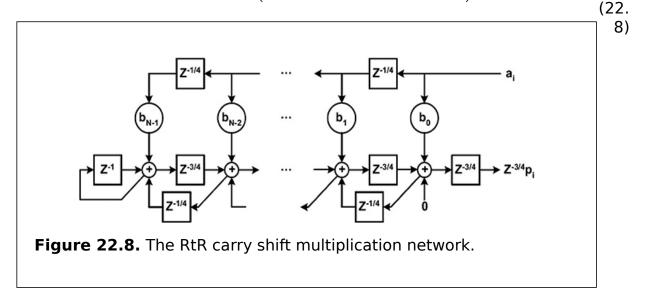

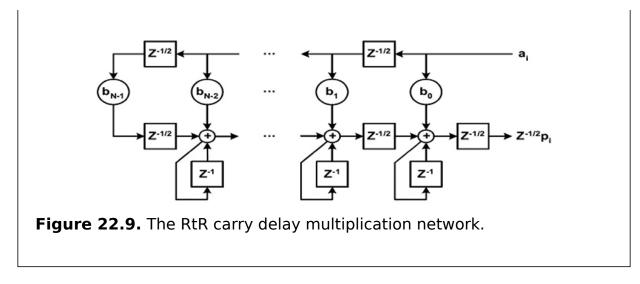

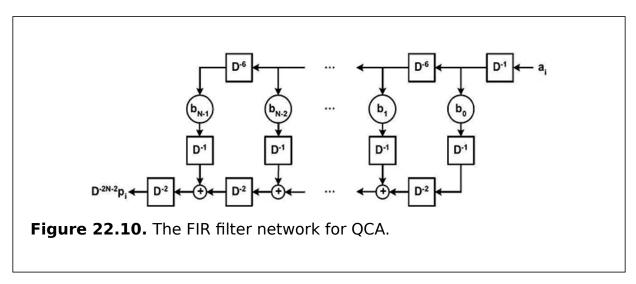

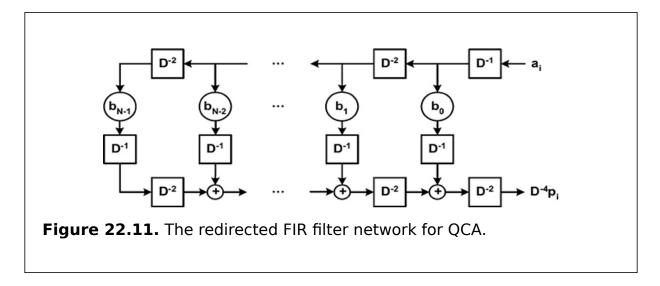

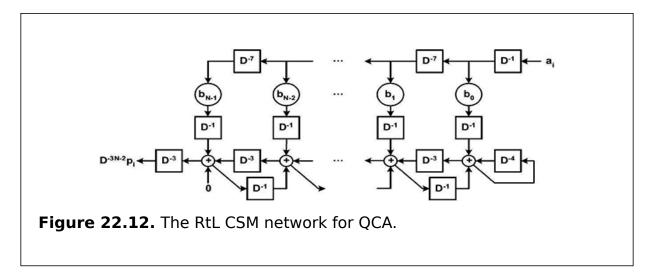

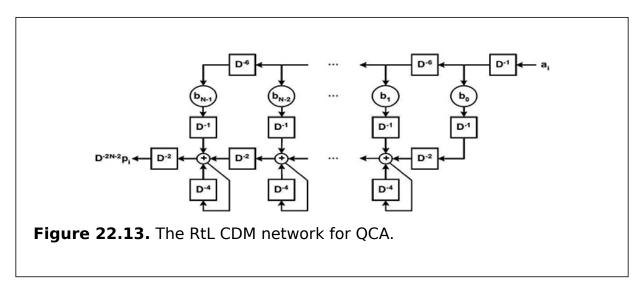

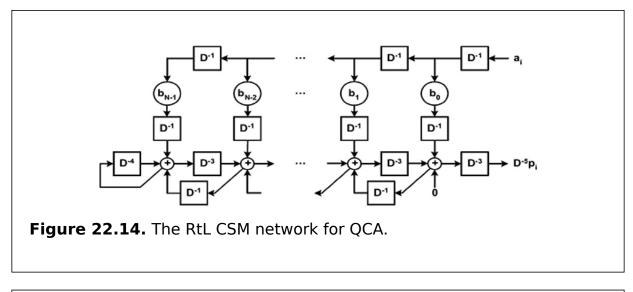

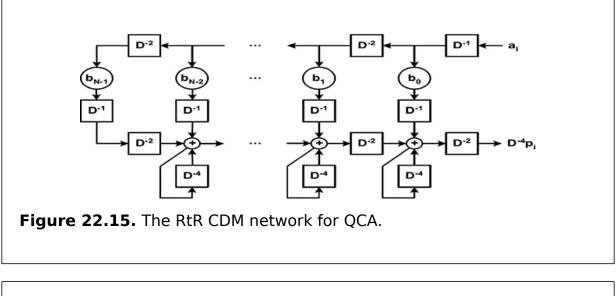

- 22.1.1 Multiplication networks

- 22.1.2 QCA multiplication networks

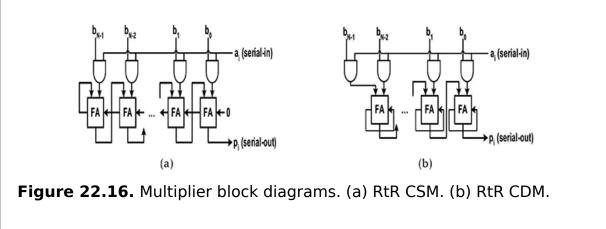

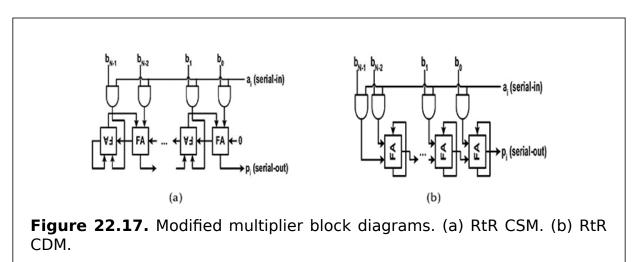

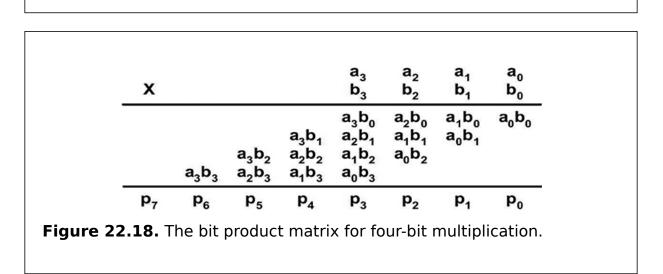

- 22.1.3 Multiplier design

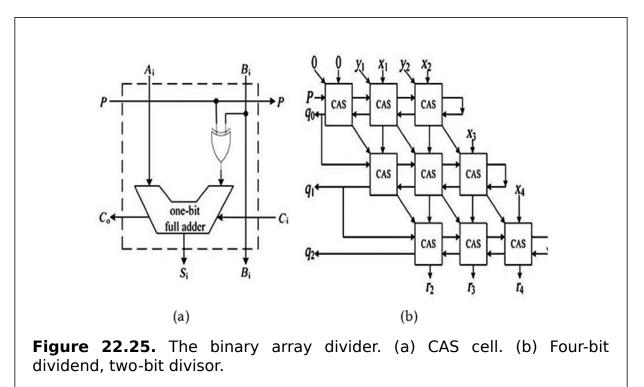

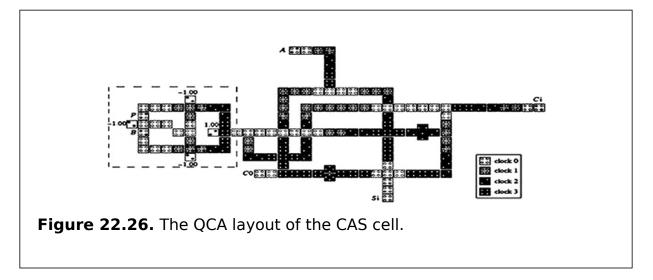

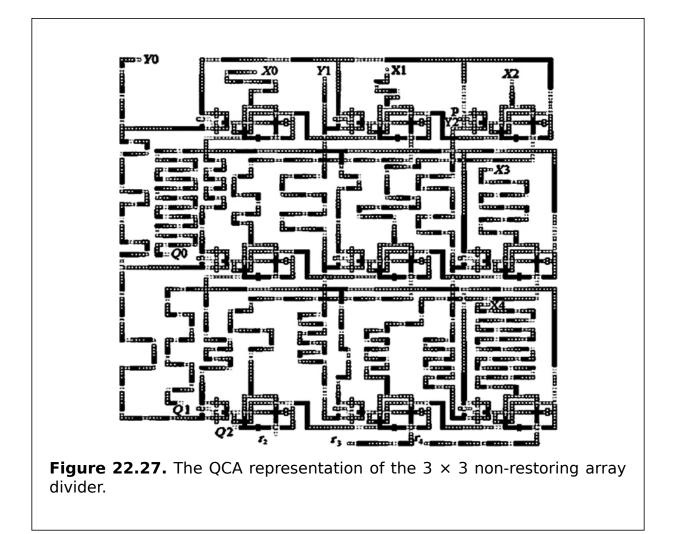

- 22.2 The QCA divider

- 22.2.1 The non-restoring binary divider

- 22.2.2 Divider implementation

- 22.3 Summary Critical thinking questions References

#### **23 QCA asynchronous and synchronous counters**

- 23.1 The asynchronous counter

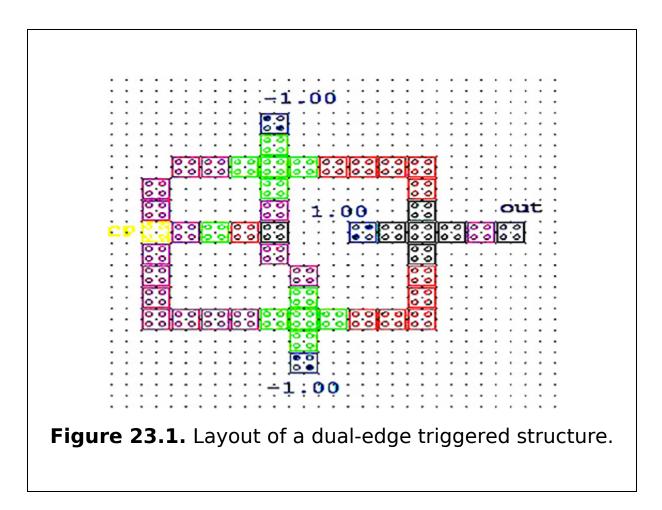

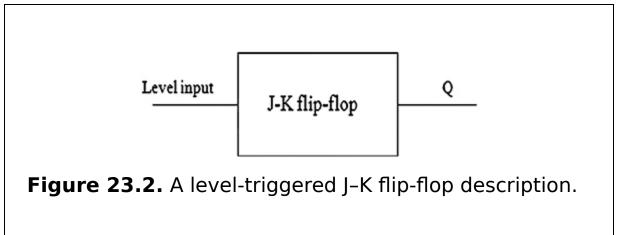

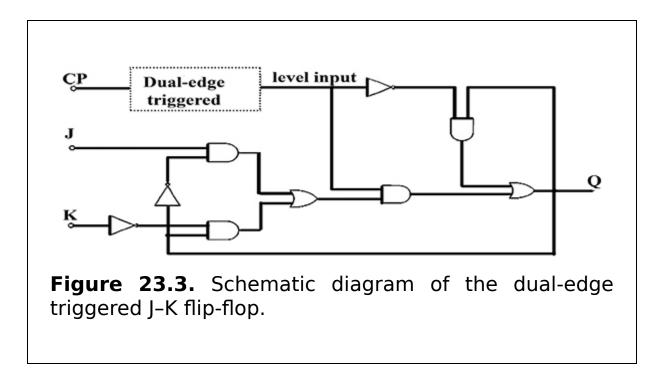

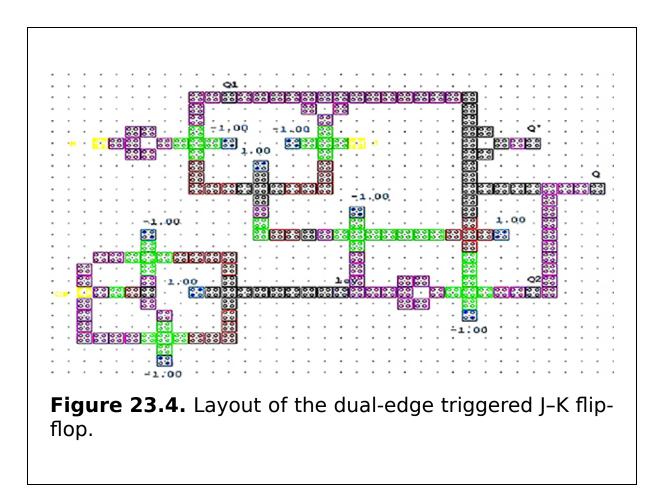

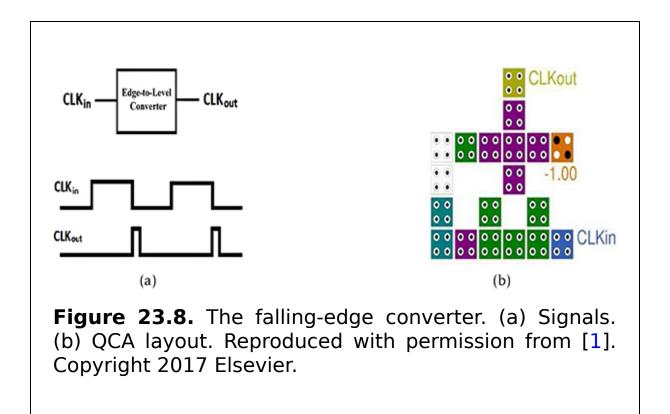

- 23.1.1 The dual-edge triggered J-K flip-flop

- 23.1.2 The design of dual-edge triggered J–K flipflop

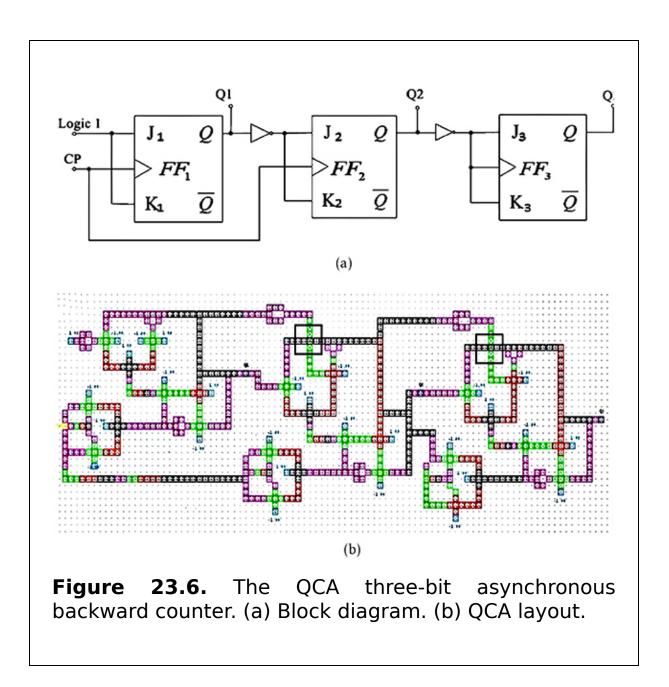

- 23.1.3 The asynchronous backward counter

- 23.2 The synchronous counter

- 23.2.1 QCA synchronous counters

- 23.3 Summary

- Critical thinking questions References

- 24 The QCA decoder and encoder

- 24.1 The QCA decoder

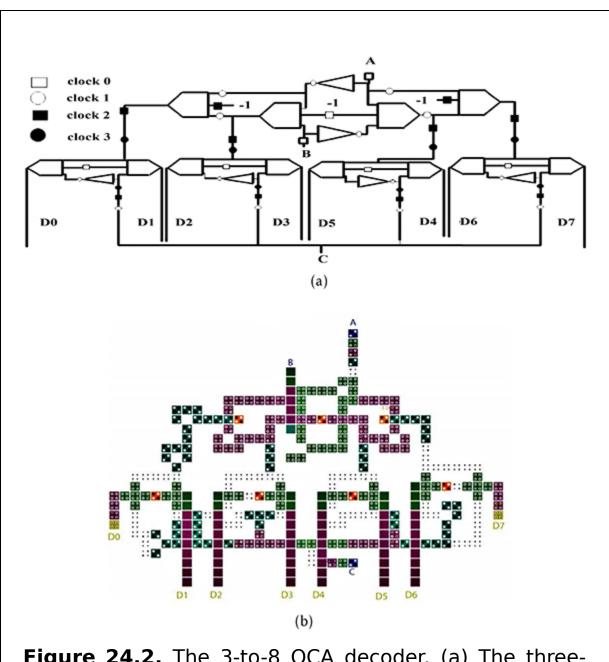

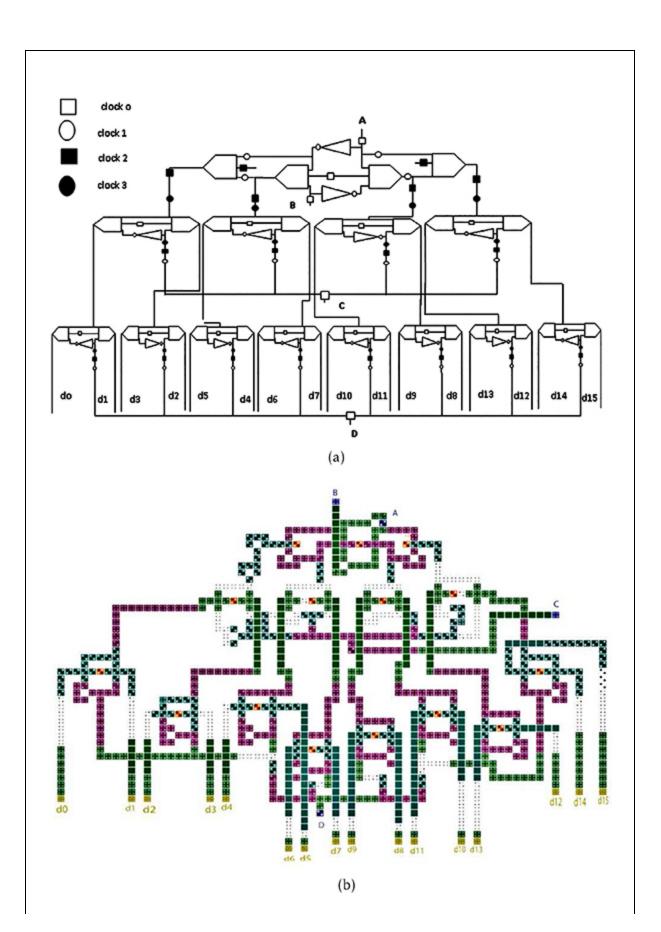

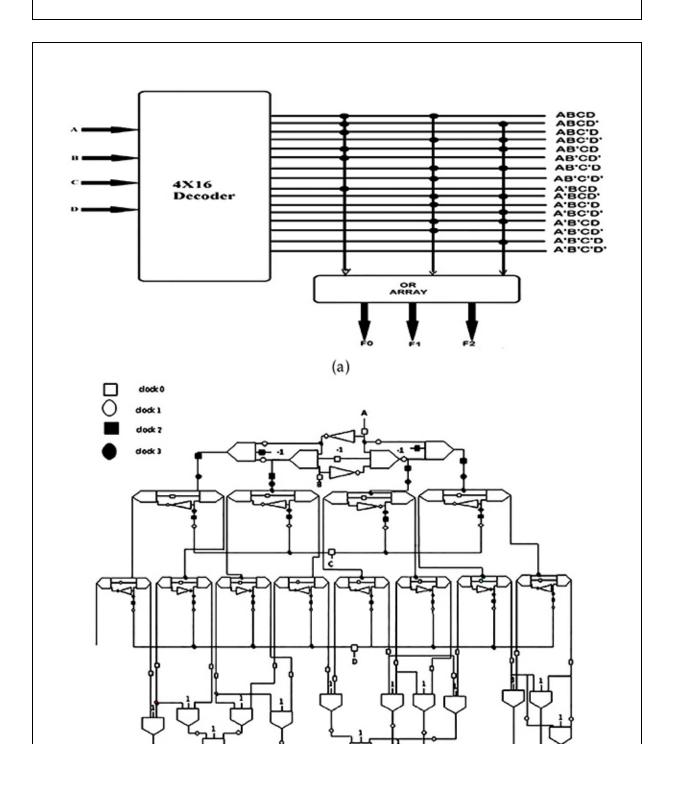

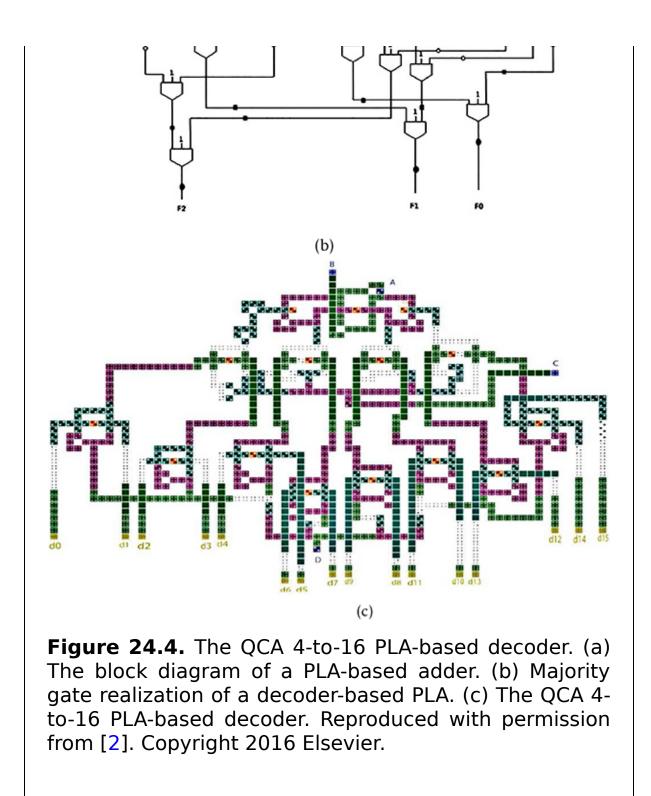

- 24.1.1 The QCA 2-to-4 decoder

- 24.1.2 The QCA 3-to-8 decoder

- 24.2 The QCA encoder

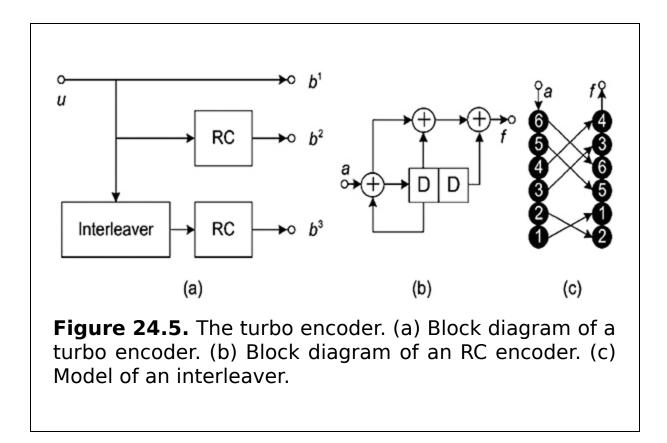

- 24.2.1 The QCA turbo encoder design

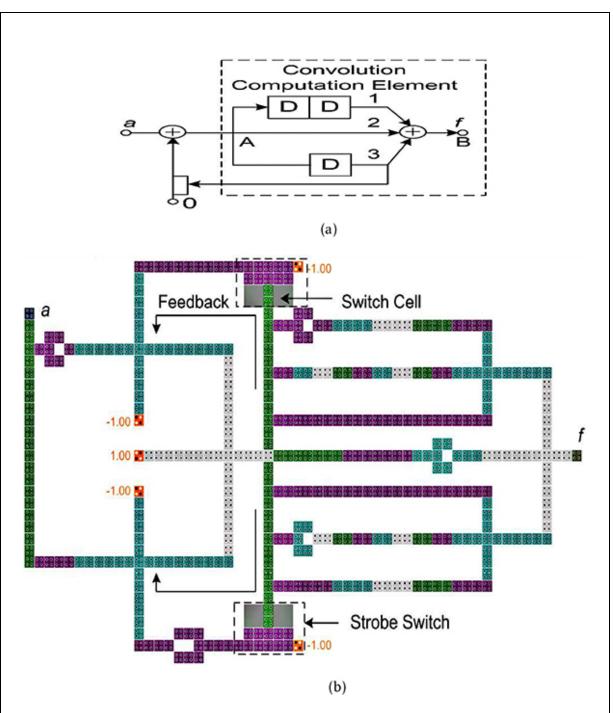

- 24.2.2 The RC encoder with single-feedback

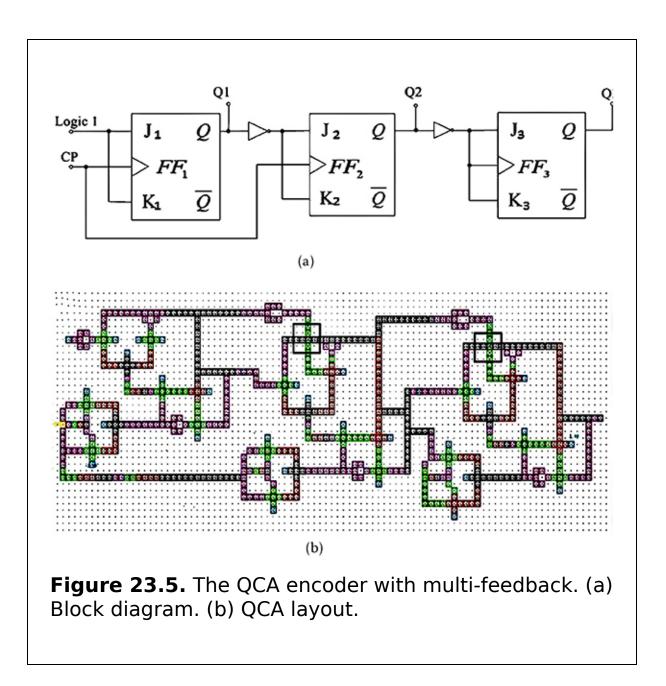

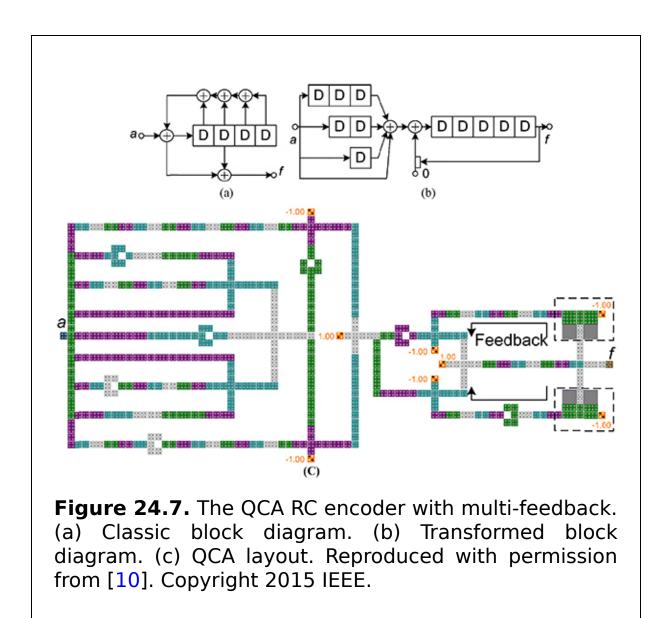

- 24.2.3 The RC encoder with multi-feedback

- 24.3 Summary

Critical thinking questions

References

#### 25 The QCA multiplexer and demultiplexer

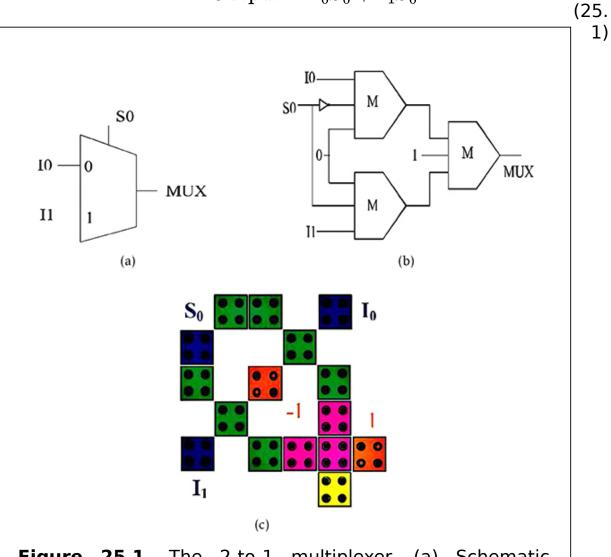

- 25.1 The QCA 2-to-1 multiplexer

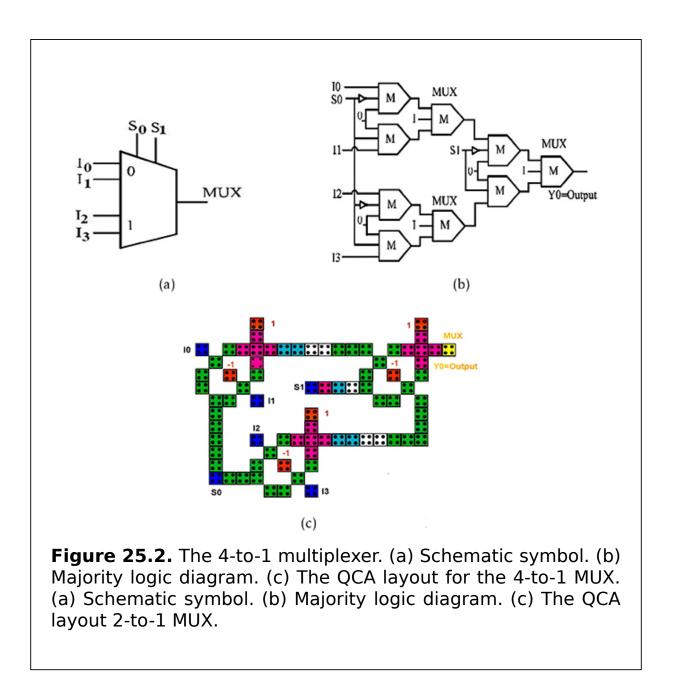

- 25.2 The QCA 4-to-1 multiplexer

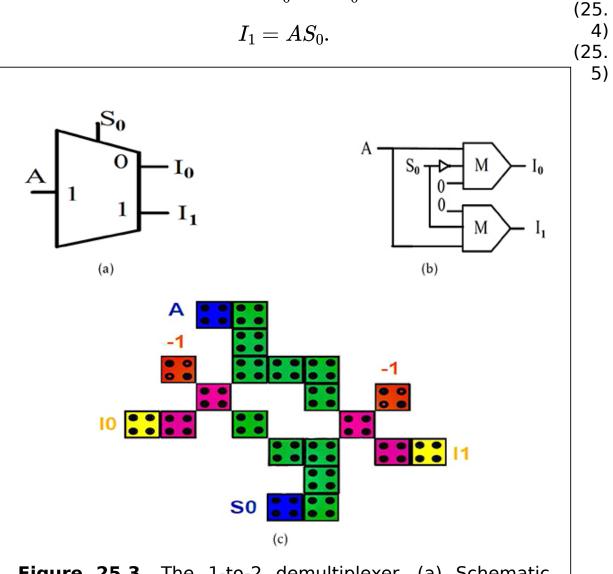

- 25.3 The QCA 1-to-2 demultiplexer

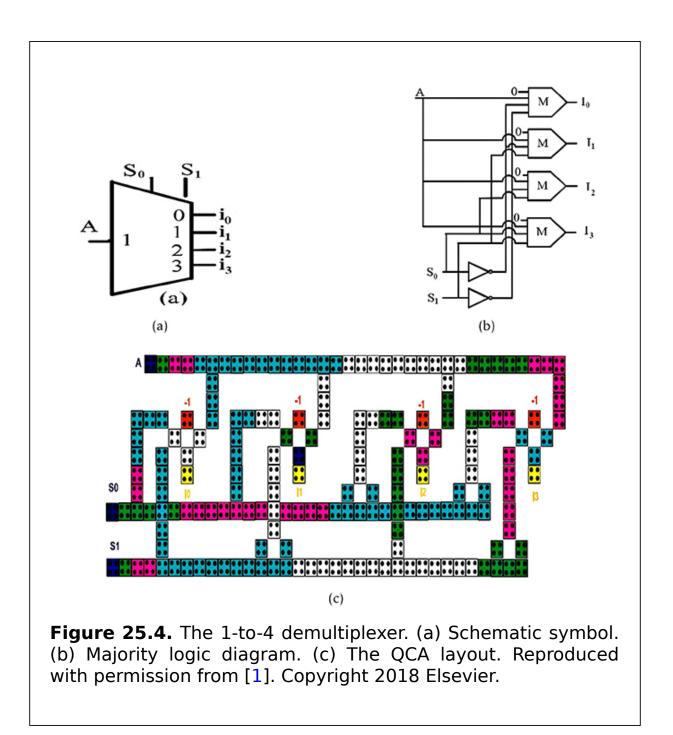

- 25.4 The QCA 1-to-4 demultiplexer

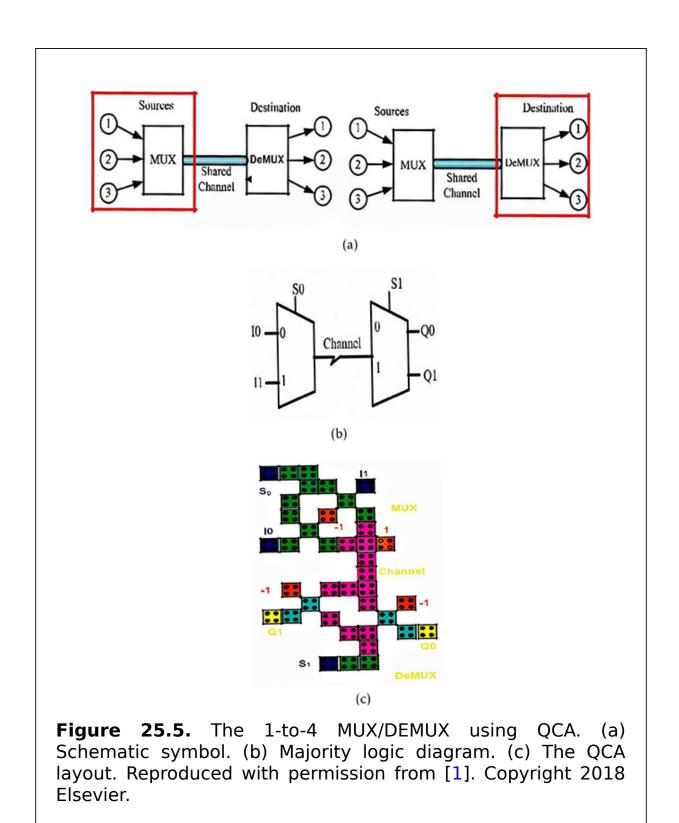

- 25.5 Multiplexing/demultiplexing using QCA

25.5.1 The effect of the selector line  $(S_0, S_1)$  on the 2-to-1 MUX/1-to-2 DEMUX

- 25.6 Summary Critical thinking questions References

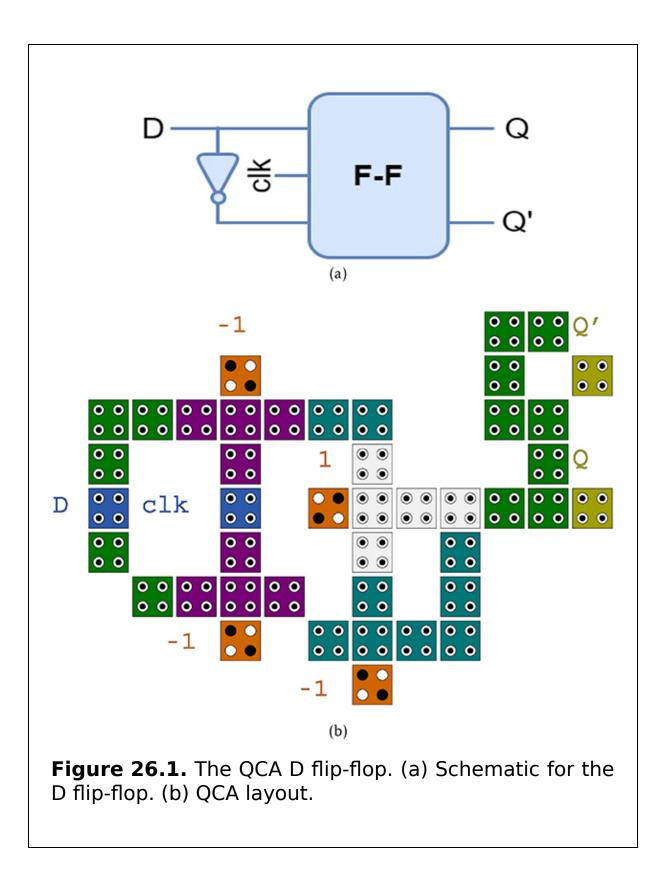

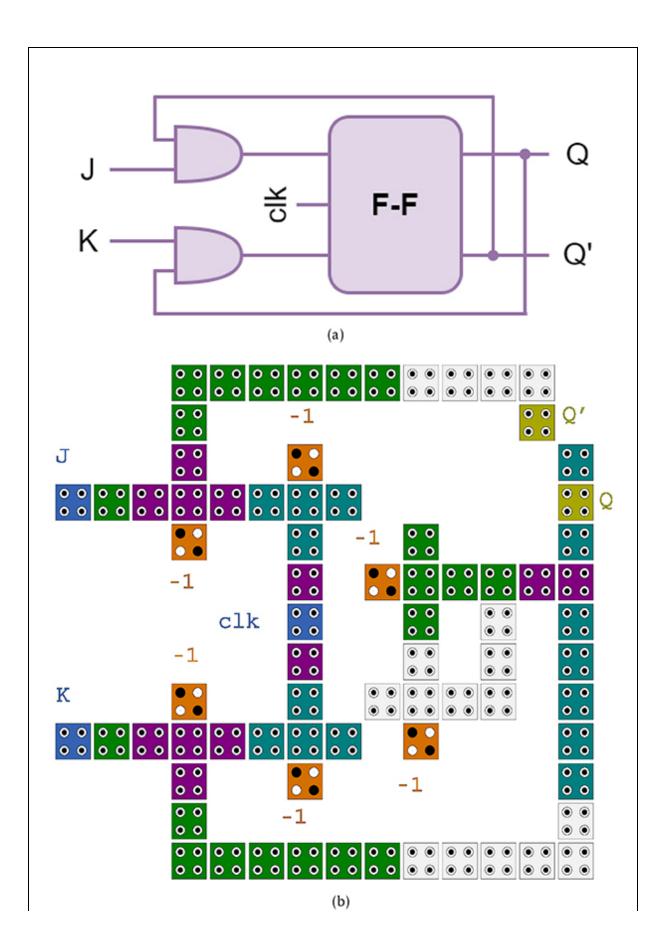

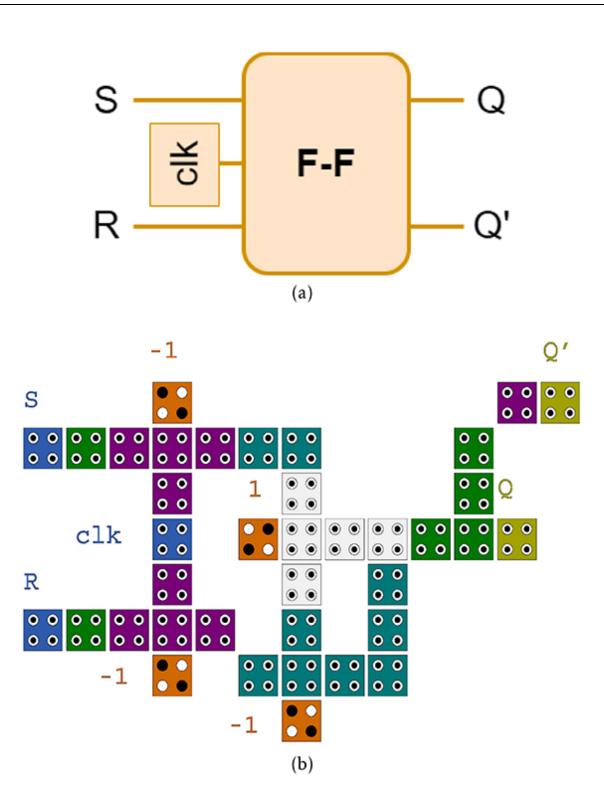

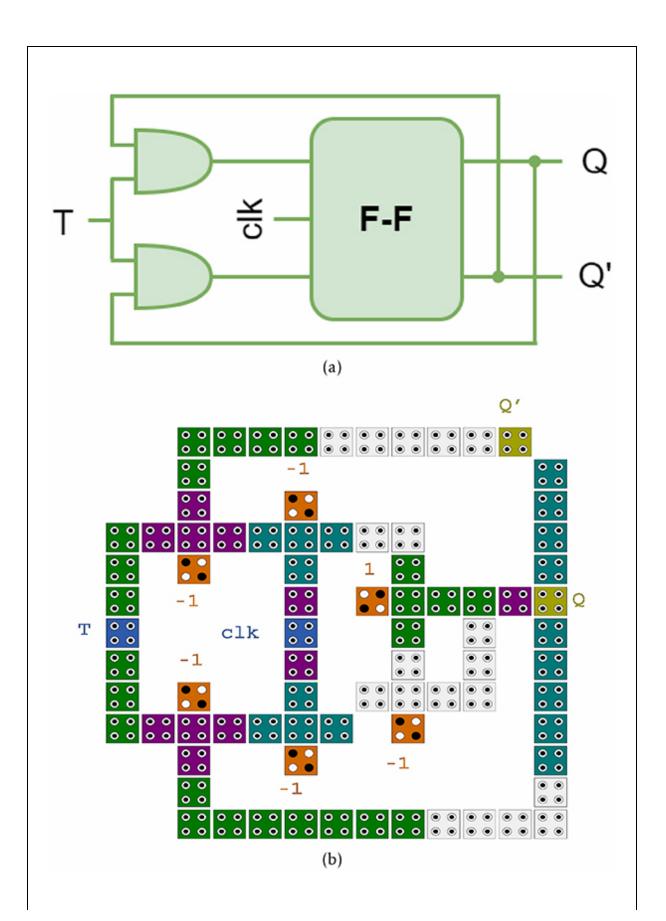

- 26 QCA flip-flops

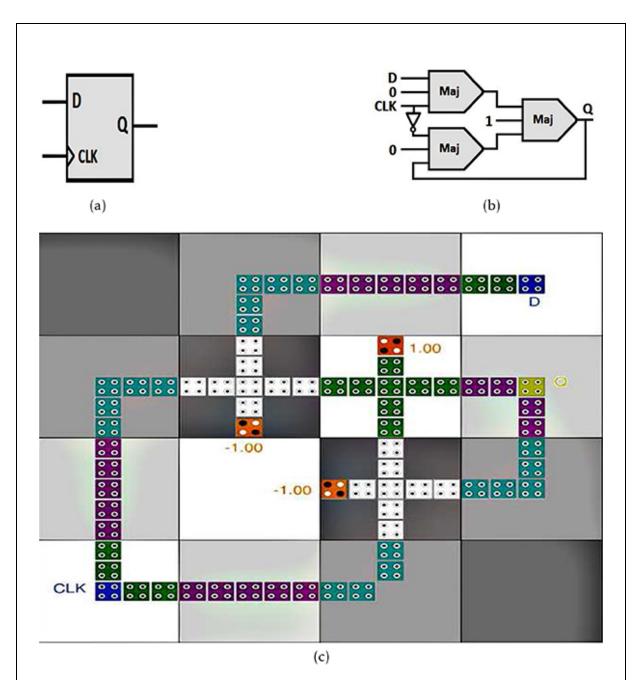

- 26.1 QCA D flip-flops

- 26.2 QCA J-K flip-flops

- 26.3 QCA SR flip-flops

- 26.4 QCA T flip-flops

- 26.5 Applications

- 26.6 Summary Critical thinking questions References

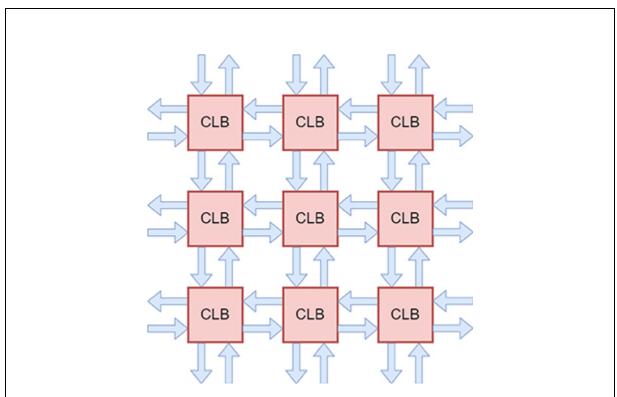

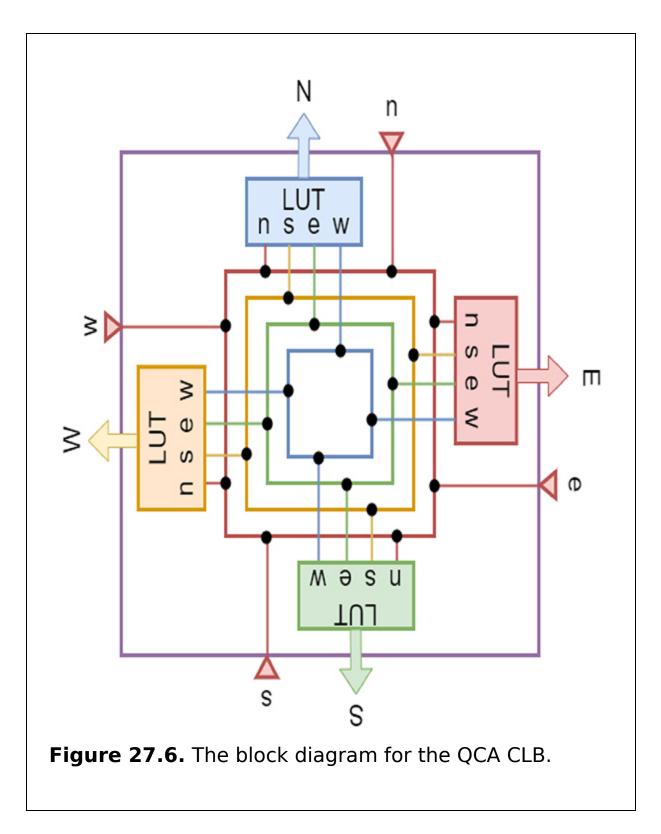

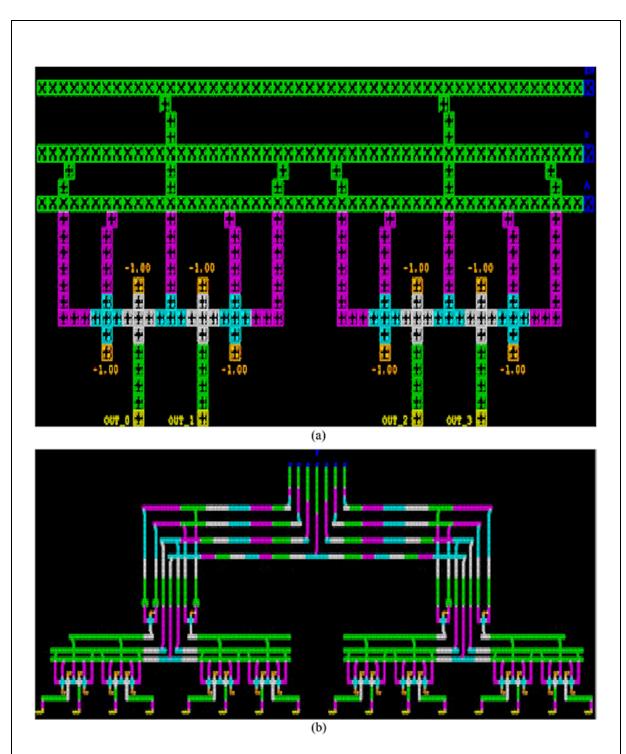

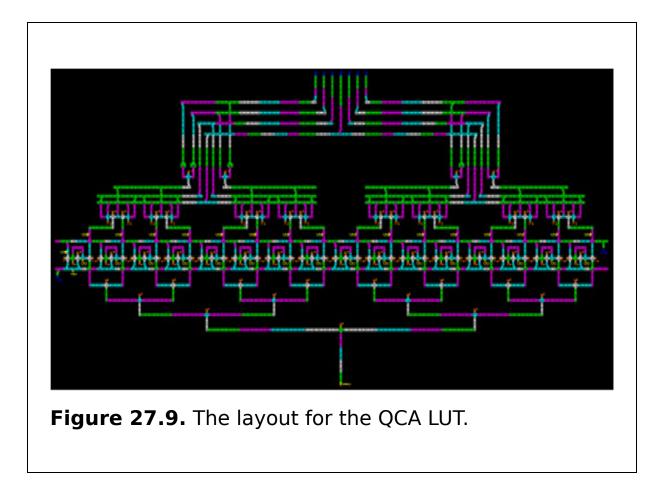

#### 27 QCA programmable logic devices

- 27.1 The QCA programmable array logic

- 27.2 The QCA programmable logic array

- 27.3 The QCA field-programmable gate array

- 27.4 The importance and applications of QCA programmable logic devices

- 27.5 Summary

Critical thinking questions

References

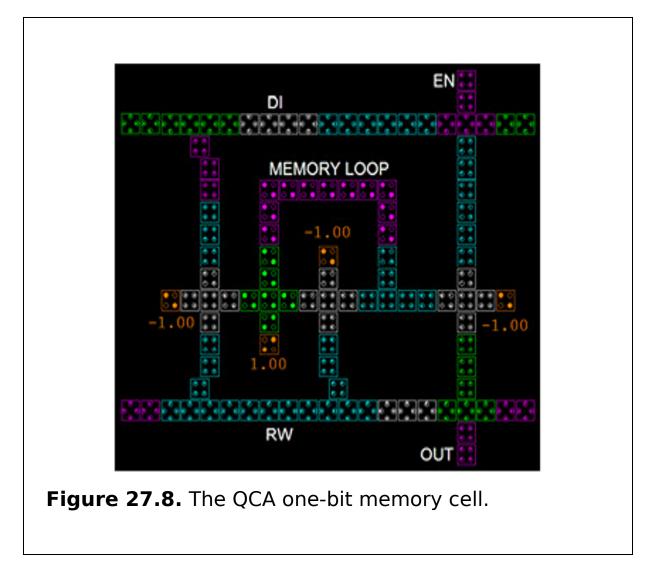

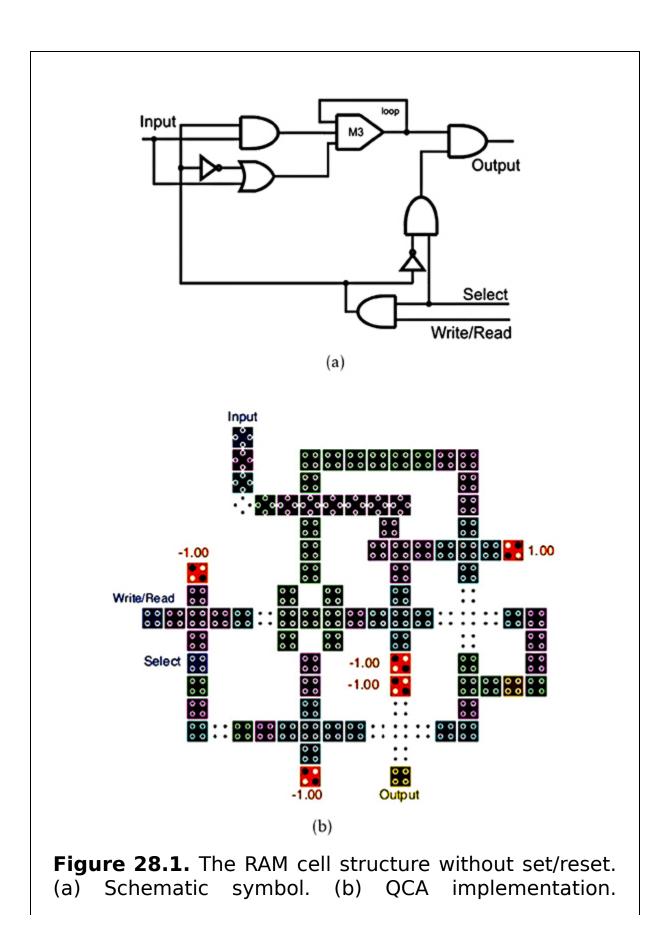

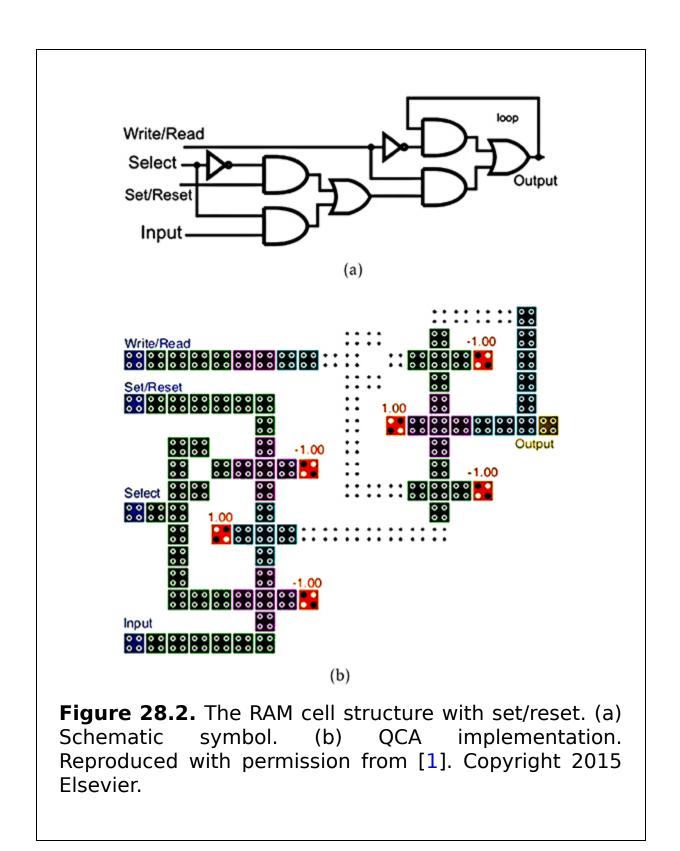

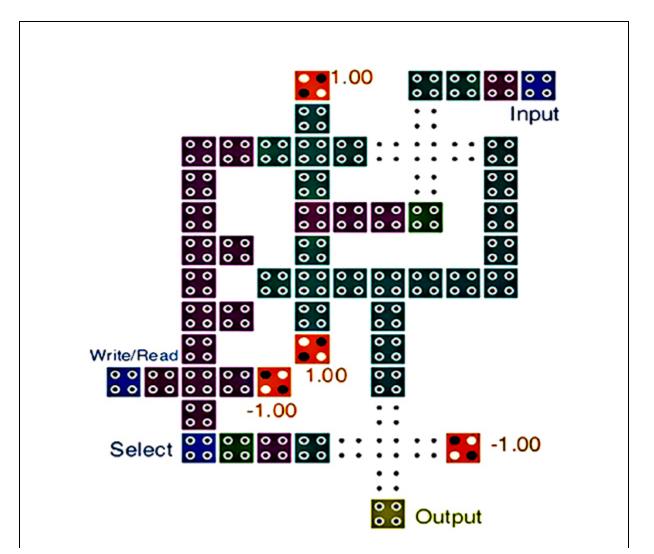

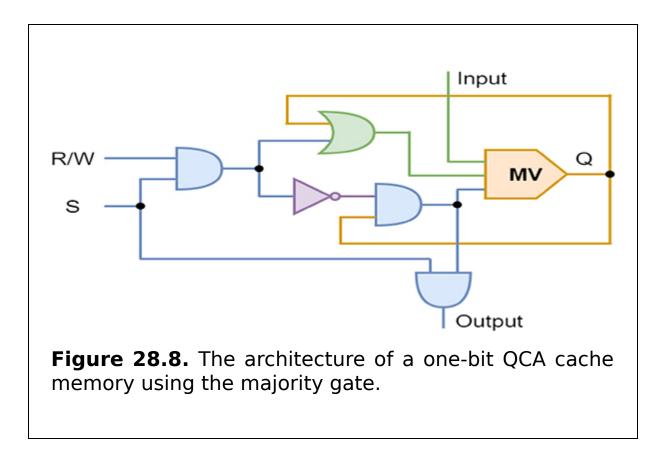

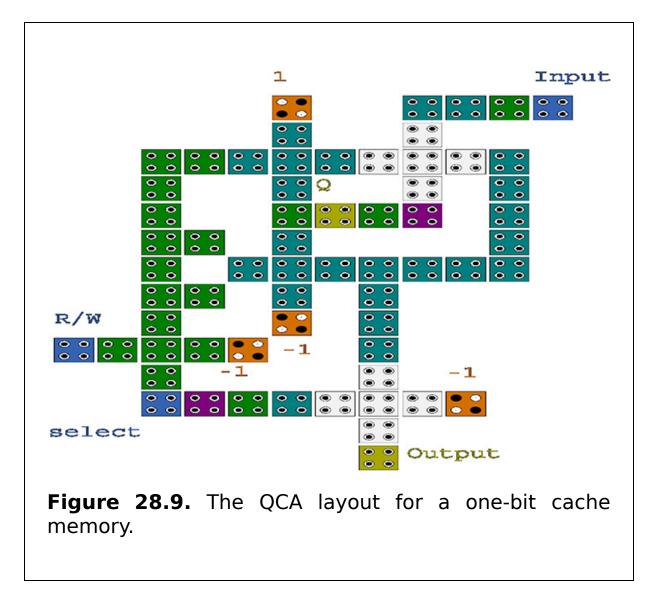

#### 28 QCA RAM, ROM, and cache memory

- 28.1 The RAM cell

- 28.2 The QCA ROM

- 28.3 The QCA cache memory

- 28.4 Summary Critical thinking questions References

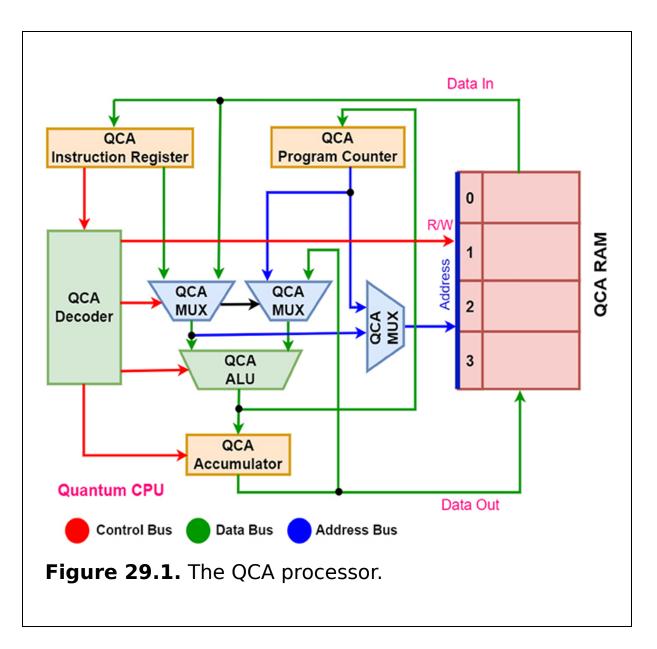

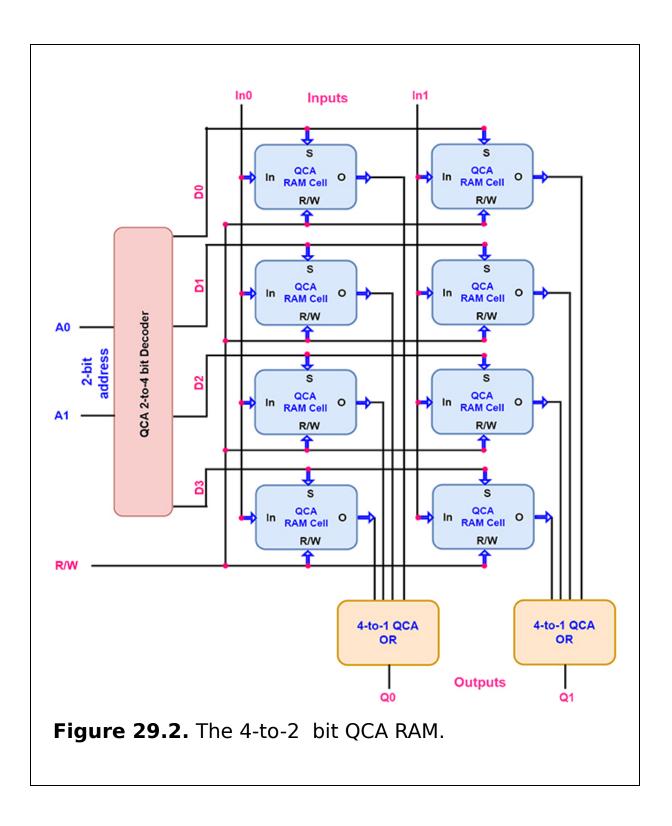

#### 29 The QCA processor circuit

- 29.1 Introduction

- 29.2 Basic definitions

- 29.3 The block diagram of a QCA processor

- 29.4 The basic components of a QCA processor

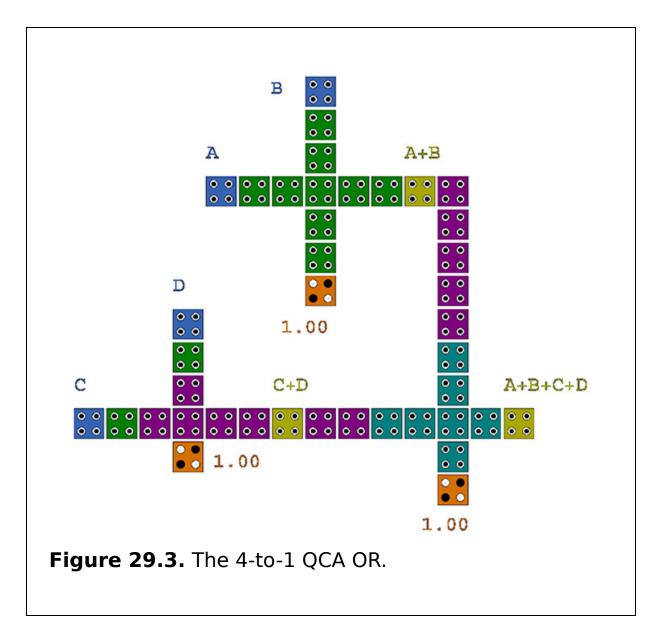

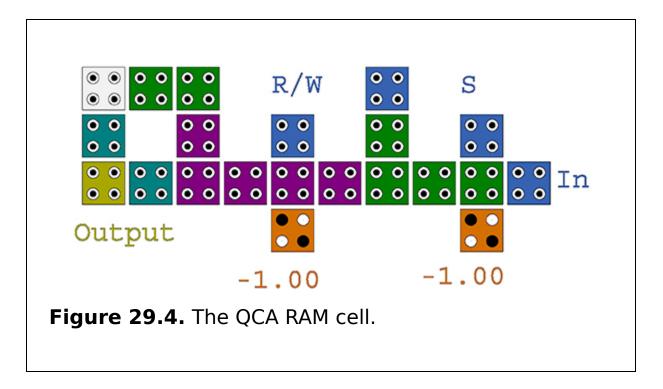

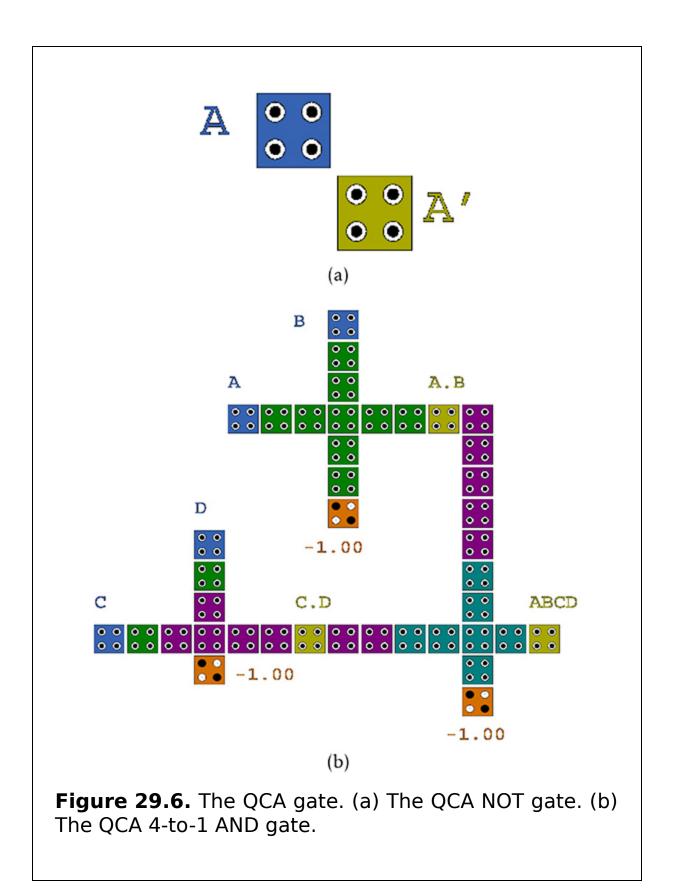

- 29.4.1 The QCA RAM

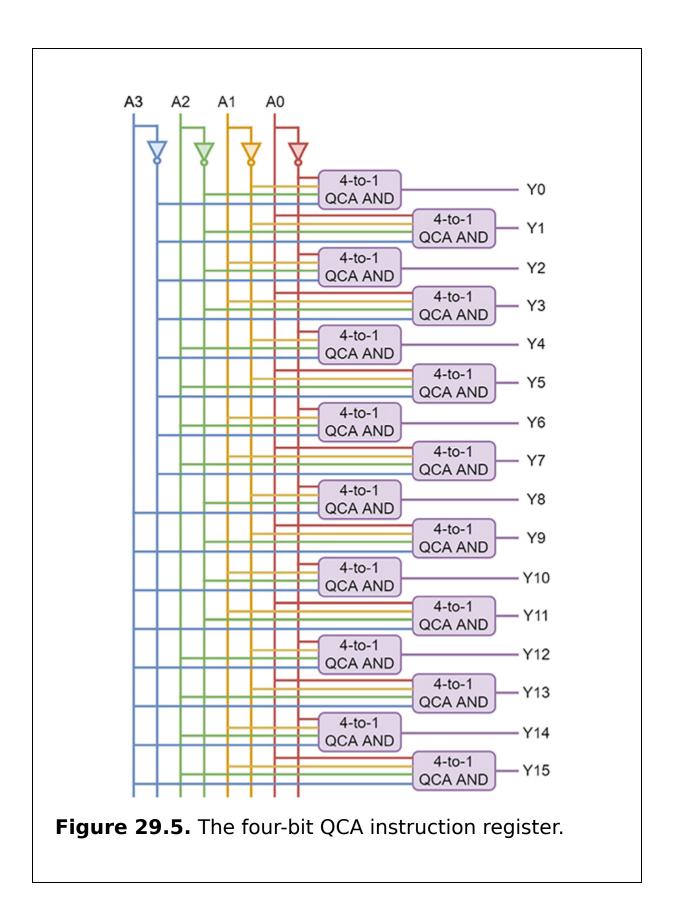

- 29.4.2 The QCA instruction register

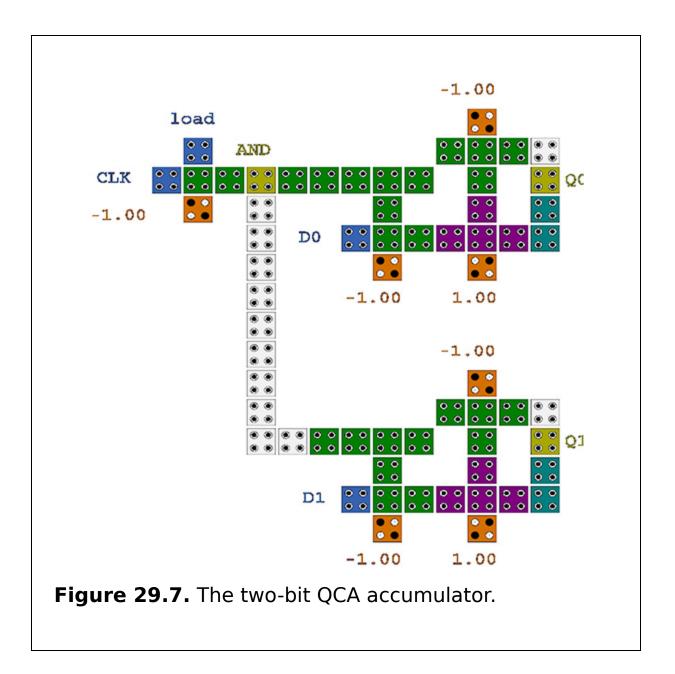

- 29.4.3 The QCA accumulator

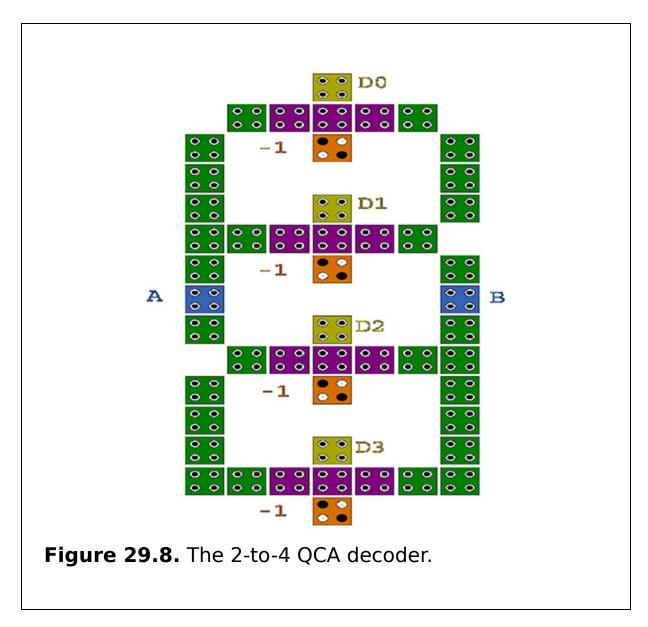

- 29.4.4 The QCA decoder

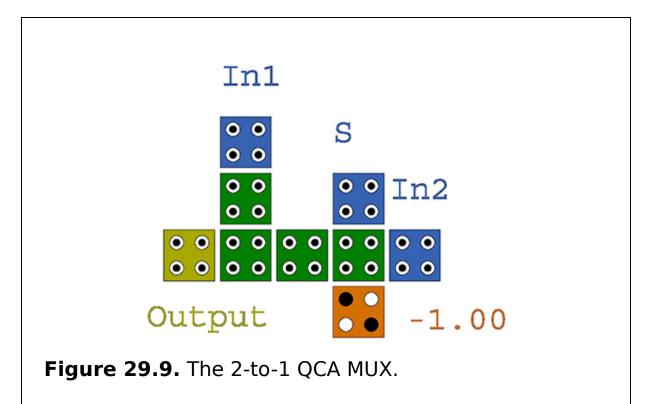

- 29.4.5 The QCA multiplexer

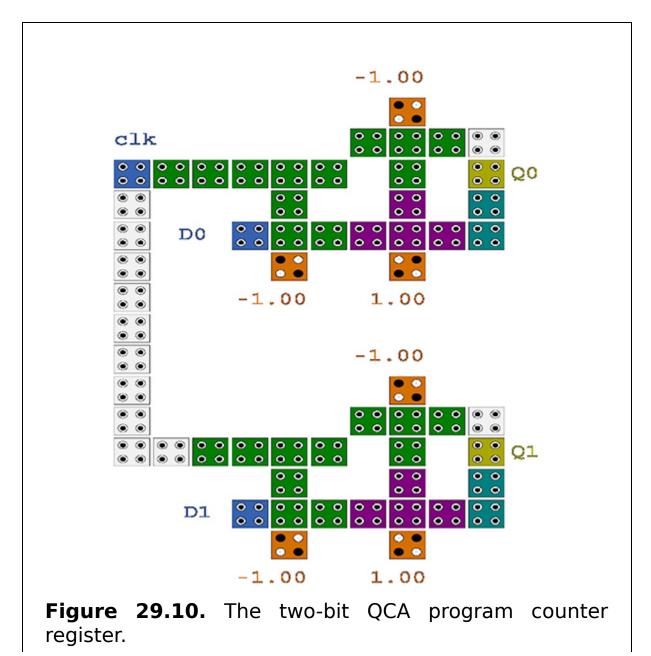

- 29.4.6 The QCA program counter

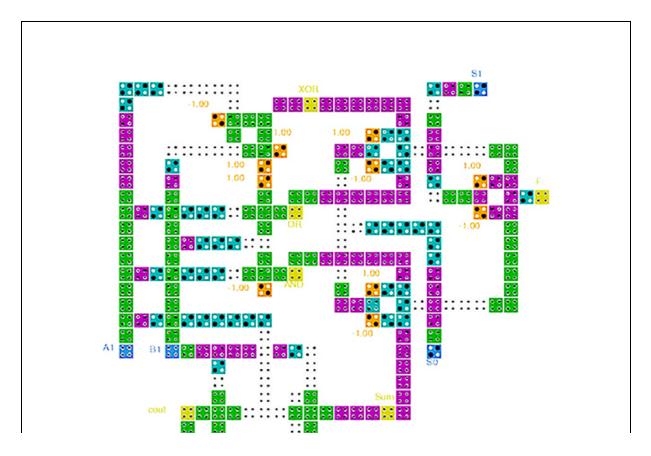

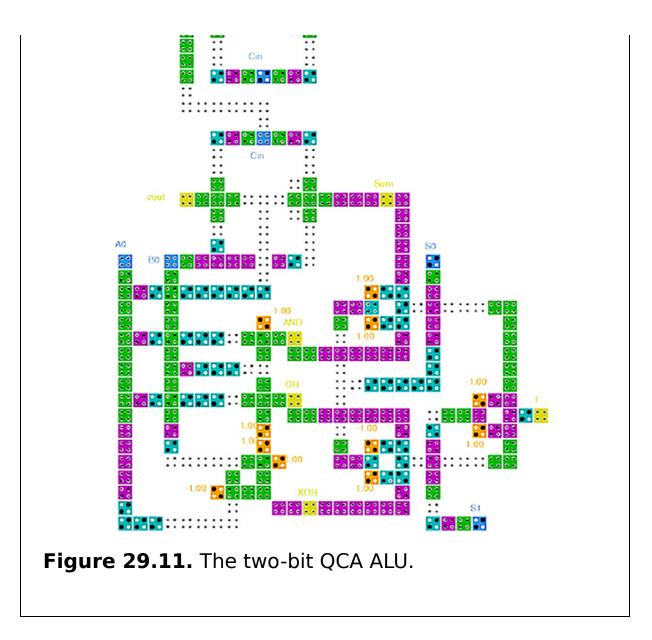

- 29.4.7 The QCA ALU

- 29.5 Summary

Critical thinking questions References

#### **30** Applications of QCA technology

- 30.1 High performance

- 30.2 Small size

- 30.3 Low power consumption

- 30.4 Encryption and authentication

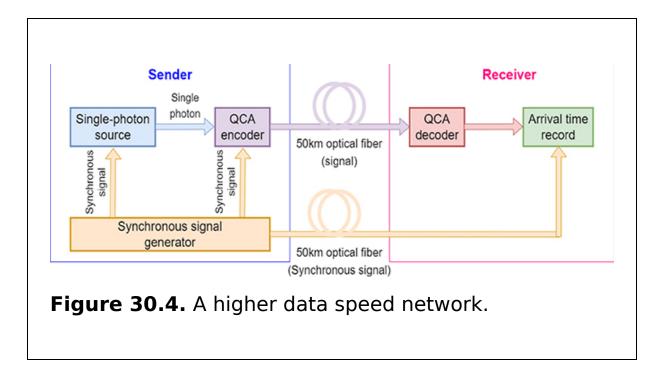

- 30.5 Higher data speed

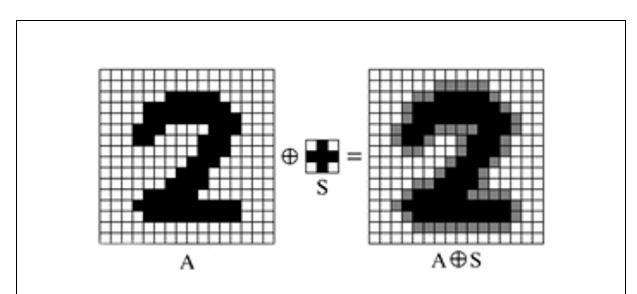

- 30.6 Image processing

- 30.7 Summary

Critical thinking questions References

#### Part IV QCA fault tolerance

#### **31 QCA fault-tolerant circuits**

- 31.1 The necessity of QCA fault-tolerant circuits

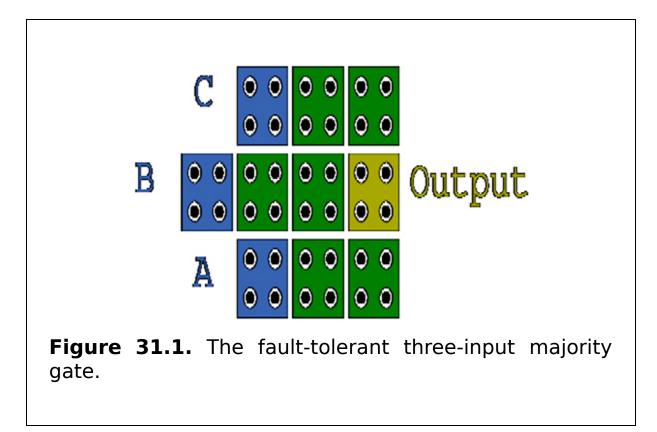

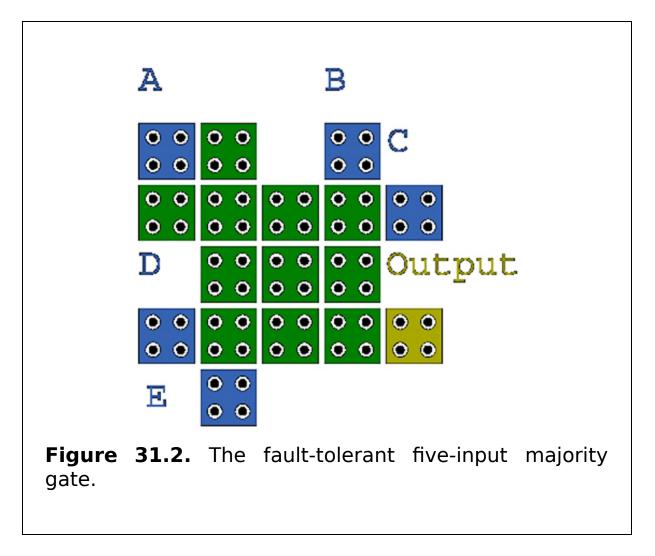

- 31.2 The fault-tolerant QCA majority gate

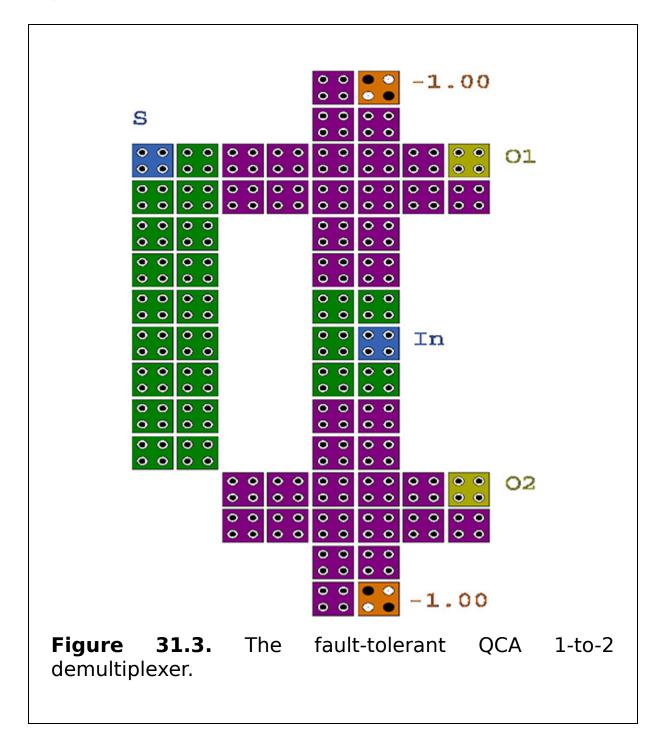

- 31.3 The fault-tolerant QCA 1-to-2 demultiplexer

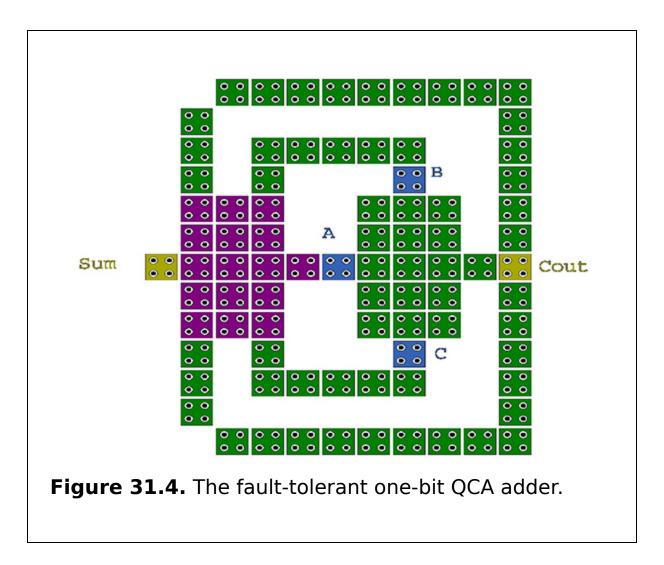

- 31.4 The fault-tolerant QCA full-adder

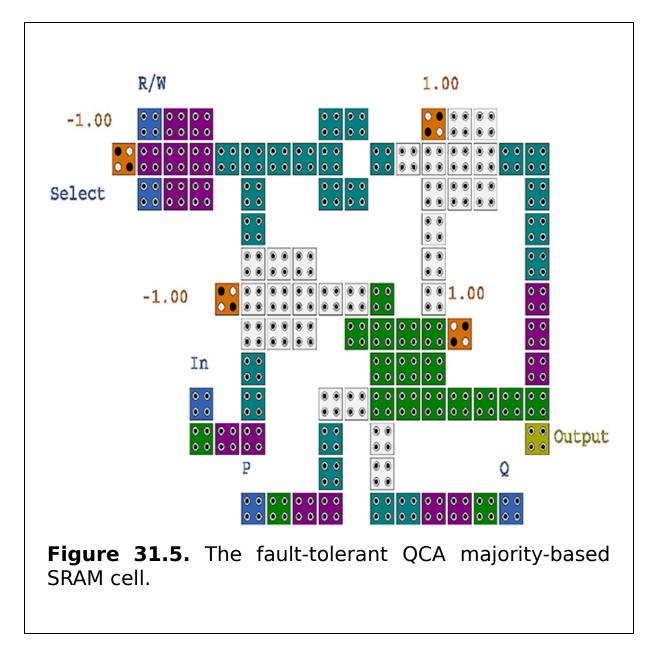

- 31.5 The fault-tolerant QCA SRAM cell

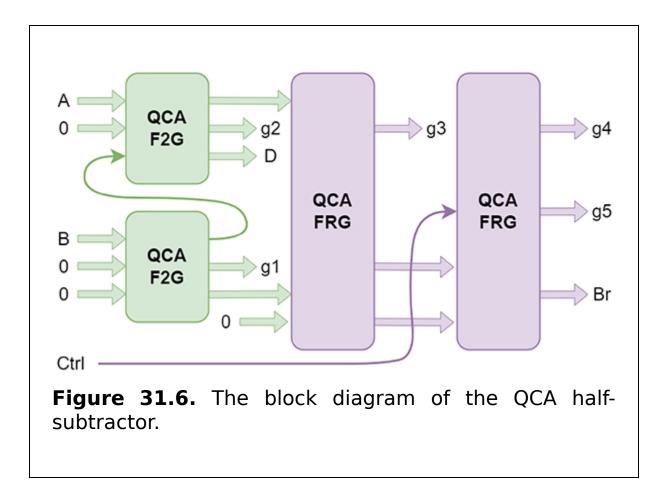

- 31.6 The fault-tolerant QCA subtractor

- 31.7 The fault-tolerant QCA multiplier

- 31.8 Summary

Critical thinking questions

References

To my respected, wonderful parents and also to my beloved wife, daughter, and son who made it possible for me to write this book

### Preface to the Second Edition

The rise of nanotechnology has led to an increasing role for quantum computing in the development of smaller and enerav-efficient computers. leveraging Βv the more principles of quantum mechanics, certain computations can be performed at significantly higher speeds. Quantum computing represents one of the most promising nanotechnologies for creating modern and compact computer systems. Unlike traditional computers that rely on binarv loaic. quantum computers operate on а different concept. They exploit quantum fundamentallv simultaneously evaluate entanglement to multiple probabilities. The processing and memory unit of a quantum computer system is becoming small like an atom and the switching techniques have reached the peak of their development. Consequently, a completely fresh mindset is needed for constructing computing machines. Recently, advancements in mathematics, materials science, and computer engineering have brought guantum computing from the realm of theory into practical implementation.

This quantum computing book covers basic themes of quantum computing in the first part, fault-tolerant quantum computing in the second part, quantum-dot cellular automata (QCA) in the third part and QCA fault-tolerant circuits in the fourth part. Each part has a critical thinking question section for the readers.

The book covers the design aspects of quantum computing, specifically focusing on the design of various quantum circuits. These circuits include important components such as adder, multiplier, divider, encoder, decoder, barrel shifter, comparator, and arithmetic logic unit (ALU) as well as the processor itself. These quantum circuits

serve as the essential building blocks of a functioning quantum computer. By studying the content of this book, readers will gain a comprehensive understanding of guantum computing, ranging from basic concepts to advanced topics. This knowledge will empower them to create new and innovative quantum circuits. Additionally, the book explores the significance of quantum error correction, which has greatly enhanced the potential of quantum computing technology in the long run. With the implementation of quantum error correction, the encoded quantum information can be safeguarded against errors resulting from uncontrolled interactions with the environment or imperfect execution of guantum logical operations.

This book also covers the area of fault-tolerant quantum computing, focusing on the designs of various fault-tolerant quantum circuits, including adder, multiplier, and divider. Achieving fault tolerance in quantum circuits is a highly intricate task. It involves the development of circuits that can effectively protect qubits from quantum errors resulting from insufficient control over environmental interactions. By studying this section, readers will get a greater level of knowledge of fault-tolerant quantum circuits and acquire the knowledge necessary to design their own fault-tolerant circuits. QCA (Quantum-dot Cellular Automata) represents a computational paradigm that encodes novel binarv information through charge configurations within individual cells, departing from the conventional approach of using current switches. In QCA, computation is achieved solely through Coulombic interactions, eliminating the need for current flow. This revolutionary paradigm offers a potential solution for transistor-less computation at the nanoscale. By studying this book, the readers will achieve a deep knowledge of QCA and the design processes involved in various quantum circuits using QCA design creating software. Additionally, they will become familiar with the

costs associated with QCA circuits, including cell area, delay, kink energy, and power consumption.

In the last part, the QCA fault-tolerant circuits are discussed. The necessity of QCA fault-tolerant circuits, fault-tolerant QCA majority gate, fault-tolerant QCA 1-to-2 demultiplexer, fault-tolerant QCA full-adder, fault-tolerant QCA SRAM cell, fault-tolerant QCA subtractor and fault-tolerant QCA multiplier are presented in this part.

This comprehensive book serves as an invaluable resource for both quantum computing researchers, professionals and students. Given the scarcity of books in this particular field, it fills an important gap and provides a wealth of knowledge. Whether you're a beginner or an advanced reader, this book caters to a wide range of expertise levels, making it suitable for individuals at any stage of their quantum computing journey.

### Acknowledgments

I would like to express my sincerest gratitude and particular appreciation to the various researchers in the field of quantum computing. The contents in this quantum computing book have been compiled from a wide variety of research works, where the researchers are pioneers in their respective fields. All the research articles related to the contents are listed at the end of each chapter.

I am grateful to my parents and family members for their endless support. Most of all, I want to thank my lovely wife Mrs Sitara Roshan, my sweet daughter Ms Fariha Tasnim, and my sweet son Md Tahsin Hasan for their invaluable cooperation in completing this book.

Finally, I am also grateful to all of those who have provided immense support and their valuable time to finish this book, in particular my beloved students Nitish Biswas, Md Tareq Hasan, and Rownak Borhan Himel.

## Author biography

#### Dr Hafiz Md Hasan Babu

Dr Hafiz Md Hasan Babu is currently working as a Professor in the Department of Computer Science and Engineering as well as the Dean in the Faculty of Engineering and Technology of the University of Dhaka, Bangladesh. In addition, at present, he is a member (parttime) of the Bangladesh Accreditation Council, Ministry of Education of the Government of the People's Republic of Bangladesh. He is also the Director of the Board of Directors of the Bangladesh Submarine Cable Company Limited. Dr Hasan Babu was the Chairman of the Department of Computer Science and Engineering of the University of Dhaka from 2003 to 2006 and Pro-Vice-Chancellor of The National University of Bangladesh from 2016 to 2020. He was also a Professor and the founding Chairman of the Department of Robotics and Mechatronics Engineering, University of Dhaka, Bangladesh. Dr Hasan Babu obtained his PhD in Electronics and Computer Science in Japan under a Japanese Government Scholarship and received his MSc

degree in Computer Science and Engineering in the Czech Republic under a Czech Government Scholarship. He also received a DAAD Research Fellowship from Germany.

Dr Hafiz Md Hasan Babu was awarded the Dr M O Ghani Memorial Gold Medal by the Bangladesh Academy of Sciences in 2017 for his excellent research work in the progress of physical sciences in Bangladesh. In addition, he was awarded the UGC Gold Medal Award-2017 in the Mathematics, Statistics and Computer Science category for his research work on quantum multiplier-accumulator devices. He is currently an Associate Editor of the wellknown research journal IET Computers and Digital Techniques, published by the Institution of Engineering and Technology of the United Kingdom. He was a member of the Prime Minister's ICT Task Force in Bangladesh. Dr Hasan Babu was also the President of the Bangladesh Computer Society for the session 2017-20. At present, he is the President of the International Internet Society, Bangladesh chapter.

Professor Dr Hafiz Md Hasan Babu has published more than a hundred research papers. Three of his research papers have received top research awards at international conferences.

In addition, he has published the following four textbooks for graduate and post-graduate students with three wellknown publishers in the UK and USA :

- Hasan Babu H M 2020 *Quantum Computing: A Pathway* to *Quantum Logic Design* (Bristol: IOP Publishing)

- Hasan Babu H M 2021 *Reversible and DNA Computing* (Chichester: Wiley)

- Hasan Babu H M 2022 VLSI Circuits and Embedded Systems (Boca Raton, FL: CRC Press)

- Alam M J, Hu G, Hasan Babu H M and Xu H 2022 Control Engineering Theory and Applications (Boca Raton, FL: CRC Press)

### Acronyms

- ALU arithmetic logic unit

- CPLD complex programmable logic device

- CPU central processing unit

- CSM carry shift multiplication

- MSD most significant digit

- ODQ overflow detection qubit

- PLA programmable logic array

- PLD programmable logic device

- PNS partial numerator subtractor

- PPA partial product addition

- PPG partial product generation

- QCA quantum-dot cellular automata

- QCSA quantum carry skip adder

- QFS quantum full-subtractor

- QIP quantum information processing

- QPAL quantum programmable array logic

- RAM random access memory

## Part I

### Quantum logic

### An overview of quantum circuits

Quantum computation and quantum information are the study of the information processing tasks that can be accomplished using quantum mechanical systems. Quantum computation is an application of quantum mechanics, where the evolution of a quantum system is described by a quantum algorithm. This observation suggests that quantum computing can be used as an introduction to quantum mechanics, because quantum computation and quantum information offer an excellent conceptual laboratory for understanding the basic concepts and unique aspects of quantum mechanics.

Advancements in higher-level integration and fabrication processes have resulted in better logic circuits and energy loss has also been reduced dramatically over the last few decades. This trend of the reduction of heat in computation also has its physical limit. It is well understood that in logic computation every bit of information loss generates  $kT \, \ln 2$  joules of heat energy, where k is Boltzmann's constant of  $1.38 \times 10^{-23}$  J K $^{-1}$  and T is the absolute temperature of the environment. At room temperature, the dissipating heat is around  $2.9 \times 10^{-21}$  J. The energy loss limit is also important as it is likely that the growth of heat generation as a cause of information loss will be noticeable in the future.

Quantum computing is an emerging technology that has the potential to change the perspectives and applications of computing in general. A wide range of applications can be enabled, from faster algorithmic solutions of still-difficult theoretically problems classical to more secure communication protocols. A quantum computer uses the quantum mechanical effects of particles or particle-like systems, and a major similarity between quantum and classical computers is that both are abstracted as information processing machines. Whereas a classical computer operates on classical digital information, a quantum computer processes quantum information, which shares similarities to analog signals. One of the central differences between the two types of information is that classical information is more fault-tolerant compared to its quantum counterpart.

It is possible to visualize a quantum circuit as a series of gates acting on the qubits which are abstracted as wires. The wires do not have a direct physical representation, but are associated with a temporal axis. The inputs are on the left of the diagram, the outputs on the right, and in each time step a quantum gate is applied to a qubit's state abstracted by the wire. It is standard to assume that the inputs are being initialized in the computational basis | 0 >, and it will be indicated if the case is otherwise.

Reliable quantum circuits are the result of designing operate directly quantum circuits that on encoded information, but the circuit's reliability is also increased by supplemental redundancies, such as sub-circuit repetitions. Reliable quantum circuits have not been widely used, and one of the major obstacles is their vast associated resource however, overhead, recent quantum computing architectures show promising scalabilities. Consequently, the number of particles used for computing can be

increased more easily and the classical control hardware (inherent for quantum computation) is also more reliable.

The number of output bits is relatively small compared to the number of input bits in most computing tasks. For example, in a decision problem, the output is only one bit (yes or no) and the input can be as large as desired. However, computational tasks in quantum computing require that all of the information encoded in the input should be preserved in the output. One might expect to obtain further speed-ups by adding instructions to allow the computation of a quantum circuit.

communication computation Ouantum and study information transmission and processing as physical phenomena that follow the laws of quantum mechanics. quantum mechanics Considering introduces new possibilities, such as private communication with quantum cryptography or efficient factoring algorithms. Most guantum information protocols and algorithms can be explained as a sequence of transformations applied to a known initial state and a final measurement stage. The intermediate evolution is usually the key to the procedure. This state evolution can be studied from different perspectives.

This part of the book starts with some background and quantum and preliminary studies on loaic some characteristics, as well as the evolution of quantum computers, which are discussed in chapter 1. Many of the quantum gates are included in multiple chapters. Basic definitions of the different efficiency parameters of quantum logic which are needed to design quantum circuits are in chapter 2. described Chapter 3 presents the characteristics and design procedure of a quantum bit string comparator. The designs for a quantum full-adder and quantum subtractor circuits are shown in chapter 4. In this chapter, the design techniques for a guantum full-adder as well as a quantum half-subtractor and full-subtractor are

described. The design for a quantum multiplexer and quantum demultiplexer are discussed in chapter 5. In this chapter, a quantum 2-to-1 multiplexer, a quantum 4-to-1 multiplexer, and a quantum  $2^{n}$ -to-1 multiplexer are shown. In addition, a guantum 1-to-2 demultiplexer, a guantum 1to-4 demultiplexer, and a guantum 1-to- $2^n$  demultiplexer are also provided in this chapter. Chapter 6 presents the design of a quantum adder circuit which is optimized in terms of quantum cost. The four-bit quantum carry skip adder and eight-bit quantum carry skip adder circuits are described in this chapter. The design for a quantum multiplier accumulator is described in chapter 7. The reduction of garbage outputs and ancillary inputs of quantum circuits is also described in this chapter. Chapter 8 presents the guantum divider circuit. The tree-based guantum division technique is also described in this chapter.

The design procedure and analysis of the properties of a quantum binary coded decimal (BCD) priority encoder circuit are introduced in chapter 9. Chapter 10 describes the design procedure and analysis of the properties of a quantum decoder circuit. The quantum square root circuit is described in chapter 11. In this chapter, the design of a guantum adder/subtractor circuit is also shown. The designs for a quantum SR latch, quantum D latch, quantum T latch, and quantum J-K latch are discussed in chapter 12. The quantum asynchronous and quantum synchronous counters are also introduced in this chapter. Chapter 13 presents the design of a quantum controlled ternary barrel shifter circuit. In this chapter, quantum ternary Peres gates and quantum ternary modified Fredkin gates are used. The construction procedure of quantum random access memory is shown in chapter 14. The construction procedure for a quantum memory unit is also given in this chapter. Three approaches for designing a quantum arithmetic logic unit are described in chapter 15. Chapter 16 presents the quantum programmable logic devices such as quantum PAL, quantum PLA, quantum FPGA, quantum CPLD and chapter 17 presents the details of quantum processor circuit. Finally, several real-life applications of quantum computing technology are given in chapter 18.

#### **IOP** Publishing

### Quantum Computing (Second Edition)

A pathway to quantum logic design Hafiz Md Hasan Babu

## Chapter 1

### Quantum logic

#### Learning objectives

- Learn about quantum computers and quantum logic.

- Describe the operation of a quantum computer.

- Study the superposition of the states that a qubit can represent.

- Understand how quantum and reversible logic interact with one another.

- Discuss the significance of quantum computers.

- Know the benefits and drawbacks of quantum computers.

- Obtain information about the background of a quantum computer.

- Understand the differences between conventional and quantum computers.

age of developing nanotechnology, In the quantum computing can play an incredibly important role in developing more compact and lower power consumption computers. The main appeal of quantum logic originates in its reflection of the physical law of energy conservation, in which the creation or destruction of energy is impossible, and only transformation from one form to another is possible. Hence, the fundamental law of energy

conservation is incorporated into the logic design of circuits and systems by the quantum logic. The motivation to implement circuits and systems using quantum computing is the fact that, theoretically, the internal computations in quantum logic systems consume no power.

## **1.1 Overview**

Quantum computing is a technology which consumes less power and for which the design is compact. In irreversible logic, energy dissipation is a common phenomenon since every bit loss causes energy loss in the irreversible operation. Quantum logic circuits are necessarily reversible and hence there is no dissipation of energy while processing a bit in quantum computation.

Quantum technology is one of the most promising nanotechnologies which are useful for designing modern circuits. Logic design with quantum logic is of great interest in recent technologies which allow scaling to atomistic dimensions. In this particular logic design approach, quantum cells are arranged in a particular fashion to define the logic. A classical gate cannot handle the superposition of states represented by a qubit (discussed in the section 2.1 of chapter 2). Thus, this forms the special case of the quantum device.

Quantum registers, which are necessary for the implementation of a quantum electronics device, combine n qubits to form larger Hilbert spaces  $H_n$  using the tensor product ( $\otimes$ ) operator to form

$$|\Psi

angle = | |\Psi_1

angle \otimes | |\Psi_2

angle \otimes \cdots \otimes | |\Psi_n

angle = \sum_{i=0}^n | |lpha_i| |i

angle;$$

where  $lpha_i \in C, \mid \Psi_i

angle$  represents a qubit and  $\sum_{i=0}^n \mid lpha_i \mid^2 = 1.$

High-speed multiplication has always been a fundamental requirement of high-performance processors and systems. processing (OSP) signal applications. In quantum multiplication is one of the most utilized arithmetic operations. Improving multiplier design directly benefits the embedded high-performance processors and OSP applications used in consumer and industrial electronic products. Moreover, quantum information processing (QIP) is a high-impact research area in quantum information science to construct a guantum computer. The main goal of OIP is to harness the fundamental laws of quantum aspects mechanics to all improve (e.g. acquisition, transmission, and processing) of information processing dramatically as well as to enhance the performance of quantum computers.

There are several tasks for which a quantum computer will be useful. The first, which is mentioned most frequently, is that quantum computers will be able to read secret messages communicated over the Internet using current technologies such as Rivest-Shamir-Adleman (RSA), Diffie-Hellman, and other cryptographic protocols; these protocols are based on the difficulty of number theoretic problems such as factoring and discrete logarithms. In addition, quantum computers are also useful for scientists conducting virtual experiments and searching huge amounts of data.

# **1.2 Motivations towards quantum computing**

Quantum logic is a great achievement for very-large-scale integrated (VLSI) circuit design, and can work faster than classical logic circuits. Quantum circuits are used to build quantum super computers and can solve complex problems in polynomial time. Quantum algorithms are used to implement quantum circuits.

important property Ouantum bits have the of superposition, which means that the values of quantum bits can stay in more than one position at the same time, which is impossible in the case of the classical logic designs. Reversible computation supports binary (0, 1) values, whereas quantum logic can hold multiple values (binary, ternary, guaternary, etc). The multi-value support makes quantum circuits more compact and efficient with optimal delay. Unlike the two fixed values 0 or 1 of classical logic, guantum bits can take the values of a linear combination of 0 and 1. Quantum circuits are inherently reversible and there is no dissipation of energy in quantum circuits. Thus these circuits prevent the loss of information, since energy dissipation causes bit or information loss. The abovementioned properties of quantum logic circuits have motivated researchers to design circuit components using quantum logic.

# **1.3 The relationship between reversible and quantum logic**

Reversible logic circuits have one-to-one mapping between inputs and outputs. In other words, if the number of outputs in a logic circuit is equal to the number of inputs, and any input pattern may map to a unique output pattern, it is called a reversible logic circuits.

All reversible circuits can be represented by quantum logic gates. Quantum circuits maintain the rules of reversible logic. Quantum logic circuits must have a one-toone relationship between the input and output vectors like reversible logic. Quantum logic gates have unique unitary matrices which are also present in reversible logic. However, there are also differences between these two types of logic. Unlike in quantum logic, the superposition of bits and multiple values is not possible in reversible logic. Thus both similarities and differences exist between reversible and quantum logic.

Reversible circuits have broad applications in nanocomputing. Nanoelectronics engineering that would enable device scaling down to a molecular levels will almost surely imply a cellular architecture with near-neighbor connectivity. The scheme which has been developed to physically realize such a concept is called the quantum-dot cellular automaton (QCA). QCA have drawn a lot of attention for their very small feature size and ultra-low power consumption, which make them one candidate suitable for complementary metal-oxide replacing semiconductor (CMOS) technology.

#### **1.4 Quantum computers**

In 1959, Richard Feynman noted that 'as electronic components begin to reach microscopic scales, effects projected by guantum mechanics occur'. He advised that it might be used in the design of more powerful computers. In particular, guantum researchers hope to bind the superposition. In the quantum mechanical world, objects do not necessarily have visibly defined states. A traditional digital computer works with binary digits that can be in one of two states, denoted as 0 and 1; thus, for example, a fourbit computer register can hold any one of 16 ( $2^4$ ) possible numbers. However, a quantum bit (qubit) exists in a wavelike superposition of values from 0 to 1; thus, for example, a four-gubit computer register can hold 16 different numbers concurrently. In theory, a quantum computer can therefore control many values in parallel, so that a 30-gubit guantum computer would be equivalent to a

digital computer proficient at performing 10 trillion floatingpoint operations per second.

During the 1980s and 1990s, the theory of quantum computers advanced considerably beyond Feynman's early assumptions. In 1985, David Deutsch designated the structure of quantum logic gates for a universal quantum computer. In 1994, Peter Shor established an algorithm to factor numbers with a quantum computer that would involve six qubits (although more qubits would be essential for factoring large numbers in a rational time).

In 1998, Isaac Chuang, Neil Gershenfeld, and Mark Kubinec produced the first quantum computer (two-qubit) that could be burdened with data and output a result. Although their system was rational for only a few nanoseconds and slight from the perspective of solving meaningful problems, it verified the principles of quantum computation. This type of quantum computer can be prolonged by using molecules with more individually addressable elements. In March 2000, Emanuel Knill, Raymond Laflamme, and Rudy Martinez reported that they had generated a seven-qubit quantum computer. However, many researchers are skeptical about extending magnetic techniques much beyond 10 to 15 qubits because of diminishing consistency among the elements.

Quantum computers established on semiconductor technology are yet another opportunity. In a collective approach a discrete number of free electrons (qubits) reside within incredibly small sections known as quantum dots. Although relying on decoherence, such quantum computers are constructed on well-established, solid-state procedures and offer the prospect of readily applying integrated circuit 'scaling' technology. In addition, large groups of identical quantum dots could theoretically be contrived on a single silicon chip. The chip controls an external magnetic field that controls the electron spin states, while neighboring electrons are weakly coupled through quantum mechanical effects. An array of covered wire electrodes allows individual quantum dots, which have been discussed.

### **1.5 The working principles of quantum computers**

The huge amount of processing power created by computer designers has not yet been able to satisfy the desire for speed and computing ability. In 1947, Howard Aiken claimed that only six electronic digital computers would satisfy the computing needs of the United States. Others have made similar inaccurate predictions about the amount of computing power that would satisfy the increasing needs of technological. Of course, Aiken did not take into account the large amounts of data produced by scientific research, the explosion of personal computers, or the appearance of the Internet, which further driven the need for computing power.

Scientists have already constructed basic quantum computers that can carry out certain calculations. Quantum computers will harness the power of atoms and molecules to achieve memory and processing activities. Quantum computers have the potential to achieve certain controls significantly faster than any silicon-based computer. In this book, the reader will learn what the design mechanisms of a quantum computer and just how they will be adapted for the next era of computing.

It is not necessary to look back too far to find the origins of quantum computing, as it was first conceived of less than 30 years ago. On the other hand, classical computers have been used, with many difficulties, for a comparatively long time. Paul Benioff is credited with being the first to apply quantum theory to computers, in 1981, when he posited creating a quantum Turing machine.

# **1.6 The evolution of quantum computers**

Quantum computing is still in its emerging stages. There is a long way to go before a functionally running quantum computer can be built, let alone brought to the market. However, progress in this new technology is occurring regularly and no chronological record can ever be complete. What follows is a brief timeline clarifying key areas of progress in quantum computing. Much of the technical development has been achieved in this century, while most of the primary theoretical perspectives were laid down in the late twentieth century.

In 1980, Paul Benioff was the first to design a computer which operated under guantum mechanical principles. His idea of a quantum computer was based on Alan Turing's famous paper tape computer, described in his article published in 1936. In 1981, Feynman proved that it was impossible to simulate quantum systems on a classical computer. His argument hinged on Bell's theorem, written in 1964. In 1985, David Deutsch published a report describing the world's first universal quantum computer. He showed how such a quantum machine could reproduce any realizable physical system. Enthusiasm for creating the first quantum computer was stimulated by Paul Shor's algorithm in 1994. Shor described a method for factorizing large integers. This had serious implications for cryptography, which relies on this operation being difficult in order to keep codes secure. Shor's algorithm searched for periodicities in long integer-sequences of repeated digits. It used the quantum principles of superposition to scour for periodicities in the astonishingly fast time of a few minutes. To perform this same computation on a classical computer would take longer than the age of the Universe. In 1996, Lov Grover used guantum mechanics to solve an old unstructured

search problem. For example, if someone wants to match a large database of names with a long list of telephone numbers, a classical computer could only solve this problem by querying each name with a telephone number until it found the right one, which is not fewer than O(N). Grover's quantum algorithm, however, produces the output value using only  $O(\sqrt{N})$  evaluations of the function.

In 2000, the first working five-qubit nuclear magnetic resonance (NMR) computer was put through its paces at the Technical University of Munich. Shortly after, the Los Alamos National Laboratory surpassed this feat with a working seven-qubit NMR quantum computer.

The year 2001 is known for the demonstration of Shor's algorithm. A team at the IBM Almaden Research Center in California succeeded in factorizing the integer 15 into 5 and 3. They used a thimbleful of a bespoke liquid containing billions of molecules. The molecules were constructed from five fluoride and two carbon atoms, each with their own nuclear spin state. The molecules worked as a seven-qubit quantum computer when pulsed with electromagnetic waves and monitored using NMR.

In 2006, researchers offered a new functioning standard by monitoring a 12-qubit quantum system with only minimal decoherence. NMR quantum information processors were used to decrypt the computation. These quantum controls led to the hope that higher-qubit quantum computers might be available one day. The same year, scientists took a step closer to the building of a quantum gate, the quantum representation of a mathematical rule. Also in 2006, scholars created molecules of quantum-dot pairs. These have great potential for quantum computers, in particular if more complex elements can be created.

This book focuses on how quantum gates and quantum representations of different circuits are to be designed to make a complete quantum computer. Readers will be motivated to design such circuits and to make quantum representations of different sequential and logical circuits of their own with different examples and designs of the circuit.

### **1.7 Why pursue quantum computing?**

Despite the most remarkable wave of technological inventions, there are definite computational problems that the digital revolution still cannot seem to solve, even though some of these computational problems could be solved by scientific advances. Although conventional computers have doubled in processing speed and power nearly every two years for decades, they still do not appear to be fast enough to solve these enduring problems. In the long run, to solve world's computing problems the most tenacious competently, we will need to turn to an utterly new and more capable machine: the quantum computer.

Finally, the dissimilarity between a classical computer and a quantum computer is not like the difference between an old car and a new one. Instead, it is like the difference between a horse and a hawk: while one can run, the other can fly. Classical computers and quantum computers certainly have that difference. In this chapter we have taken a careful look at where the key differences lie and have take a profound plunge into what makes quantum computers unique.

### **1.8 Summary**

This chapter mainly introduces researchers to quantum logic and simply delineates why future generations will choose quantum computing instead of conventional computers. In this chapter, the relation between reversible and quantum logic, the salient principles of quantum computers, their evolution, and necessity are described briefly.

#### **Critical thinking questions**

- 1. Why do quantum computers perform better than conventional computers?

- 2. Give an explanation of the distinction between bits and qubits in terms of quantum computing and conventional computing.

- 3. How do reversible and quantum logic relate to each other?

- 4. What makes quantum computing superior to conventional computers for future generations?

### References

- [1] Bonsor K and Strickland J 2000 How quantum computers work *How Stuff Works* https://computer.howstuffworks.com/quantum-computer.htm (Accessed: 4 December 2018)

- [2] Wikipedia Quantum cellular automaton https://en.wikipedia.org/wiki/Quantum\_cellular\_automaton (Accessed: 4 December 2018)

- [3] Holton W C Quantum computer *Encyclopædia Britannica* https://www.britannica.com/technology/quantum-computer (Accessed: 4 December 2018)

- [4] Timeline of quantum computers *Quantum Computing* 101 http://quantumly.com/timeline-of-quantum-computing-history-of-quantumcomputers//-dates.html (Accessed: 4 December 2018)

- [5] Akbar E P A, Haghparast M and Navi K 2011 Novel design of a fast reversible Wallace sign multiplier circuit in nanotechnology *Microelectron*. J. 42 973-81

- [6] Barenco A, Bennett C H, Cleve R, DiVincenzo D P, Margolus N, Shor P, Sleator T, Smolin J A and Weinfurter H 1995 Elementary gates for quantum computation *Phys. Rev.* A 52 3457

- [7] Cai X-D, Wu D, Su Z-E, Chen M-C, Wang X-L, Li L, Liu N-L, Lu C-Y and Pan J-W 2015 Entanglement-based machine learning on a quantum computer *Phys. Rev. Lett.* **114** 110504

- [8] Cohen D W 2012 An Introduction to Hilbert Space and Quantum Logic (Berlin: Springer)

- [9] Dibbo S V, Babu H M H and Jamal L 2016 An efficient design technique of a quantum divider circuit IEEE Int. Symp. on Circuits and Systems (ISCAS) (Piscataway, NJ: IEEE) pp 2102–5

- [10] Kitaev A Y 1997 Quantum computations: algorithms and error correction Russ. Math. Surv. 52 1191-249

- [11] Landaurer R 1961 Irreversibility and heat generation in the computational process *IBM J. Res. Dev.* **5** 183–91

- [12] Li D-F, Wang R-J, Zhang F-L, Deng F-H and Baagyere E 2015 Quantum information splitting of arbitrary two-qubit state by using four-qubit cluster state and bell-state *Quantum Inf. Process.* **14** 1103–16

- [13] Nielsen M A and Chuang I 2002 *Quantum Computation and Quantum Information* 10th edn (Leiden: Cambridge University Press)

- [14] Schubert M and Rana F 2006 Analysis of terahertz surface emitting quantum-cascade lasers *IEEE J. Quantum Electron.* **42** 257–65

- [15] Tóth G, Timler J and Lent C S 1998 Quantum computing with quantum-dot cellular automata using coherence vector formalism *Proc IEEE Int. Workshop on Computational Electronics (IWCE-6)*

#### **IOP** Publishing

### Quantum Computing (Second Edition)

A pathway to quantum logic design Hafiz Md Hasan Babu

# Chapter 2

# Basic definitions of quantum logic

#### Learning objectives

- Discuss quantum qubits.

- Understand how the gate's area affects the circuit's size.

- Define several quantum gates.

- Acquire knowledge of the strength, depth, and delay of any quantum circuit.

- Obtain information about the garbage outputs and constants inputs.

- Determine the cost of a quantum circuit and the complexity of quantum gates.

Quantum computing was advanced as a technological attempt to build a propositional structure that would permit relating the events of interest in quantum mechanics. Quantum computing seeks to replace the Boolean structure which, although appropriate for addressing classical physics, is insufficient for representing atomic elements. The scientific structure of the propositional linguistics of classical systems is a power set, partly ordered by set enclosure, with a pair of operations that denote conjunction and disjunction.

During the progress of quantum computing, numerous lines of study have tried to address quantum mechanics from a logical viewpoint. This book offers a map of these multiple methods in order to familiarize the reader with the very different approaches and problems deliberated in the quantum computing literature. When possible, redundant theories, algorithms, and examples are avoided in order to provide an instinctive understanding of the ideas before designing or presenting the associated mathematics.

The procedure of a two-qubit 'controlled-NOT' quantum logic gate has been designed which, in concurrence with simple single-qubit operations, forms a common quantum logic gate for quantum computation. The two quantum qubits placed in the internal and external degrees of freedom of a single trapped element which is first laser cooled to the zero-point energy. Decoherence properties are acknowledged for the operation, and the prospect of expanding the system to more qubits seems favorable.

## 2.1 The quantum qubit

A quantum bit (qubit) is typically derived from the state of a two-level quantum system, such as the ground and excited states of an atom or the vertical and horizontal polarizations of a single photon. A qubit, represented by  $|A\rangle$ , is the basic unit of information in a quantum computer, which can hold two states, 0 or 1, simultaneously or at different times. A qubit can also be a superposition (both states at the same time) of these two states, i.e. a linear combination of the binary values  $|1\rangle$  and  $|0\rangle$  ( $\alpha |0\rangle_i + \beta |1\rangle_i$ , where  $\alpha$  and  $\beta$  are the probabilities of being in the  $|1\rangle$  and  $|0\rangle$  states, respectively), whereas classical bits or binary bits are in one of two possible states, labeled 1 and 0.

### 2.2 The quantum gate

A quantum gate is a basic quantum circuit operating on a small number of qubits. Previously, various quantum gates

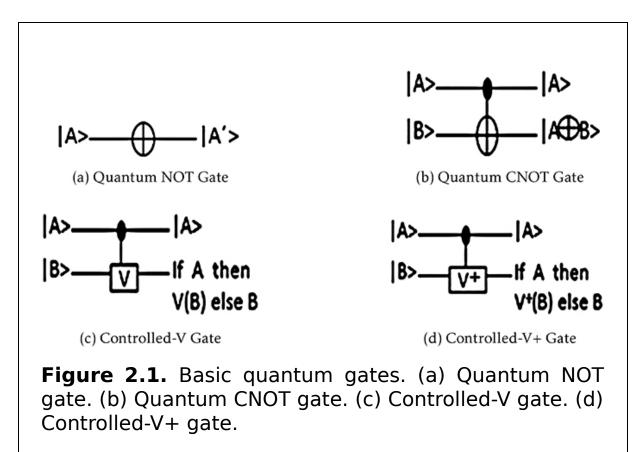

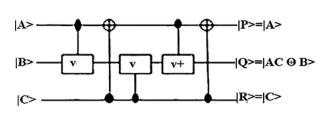

with different functionalities have been designed. Among them, the NOT, CNOT, controlled-V, and controlled-V<sup>+</sup> gates represent an important class of quantum gates. These gates are shown in figure 2.1. In this figure the control, target, and contact qubits are represented by the  $\bullet$ ,  $\oplus$ , and | symbols, respectively. In a quantum gate the number of outputs must be equal to the number of inputs.

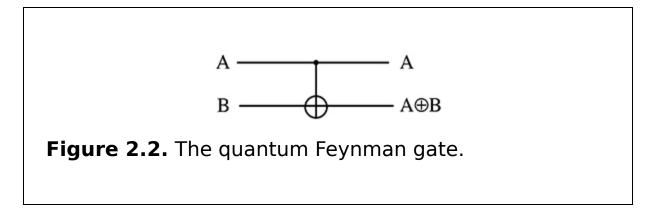

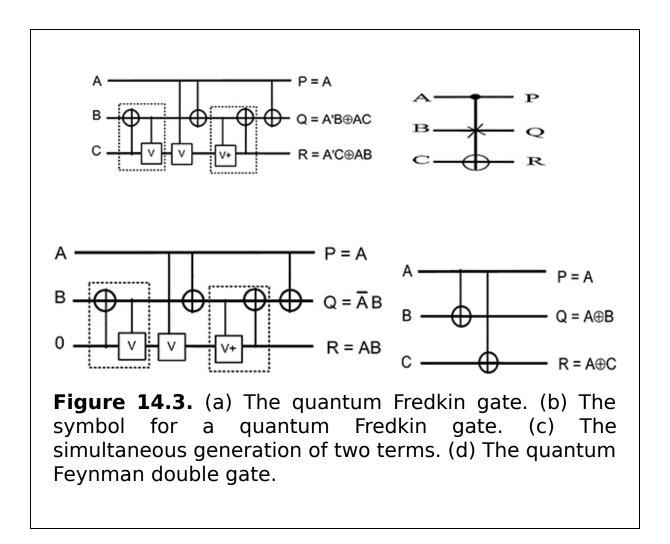

#### 2.2.1 The quantum Feynman gate

The quantum Feynman gate is a 2 × 2 quantum gate which implements the logical functions of P = A and  $Q = A \oplus B$ , and is illustrated in figure 2.2. The quantum Feynman gate can be used for copying a bit. When B is set to zero, then the output vector will be P = A and Q = A, which ensures copying of the input A.

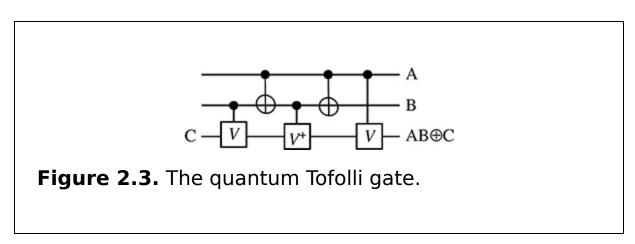

#### 2.2.2 The quantum Tofolli gate

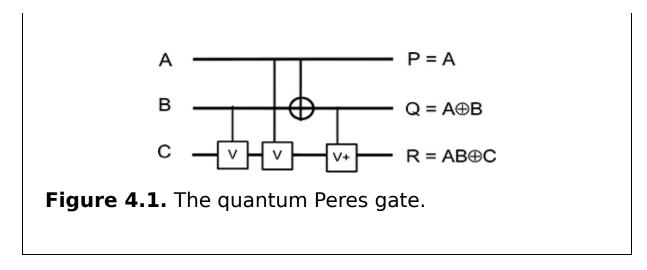

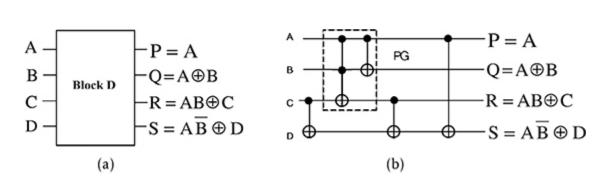

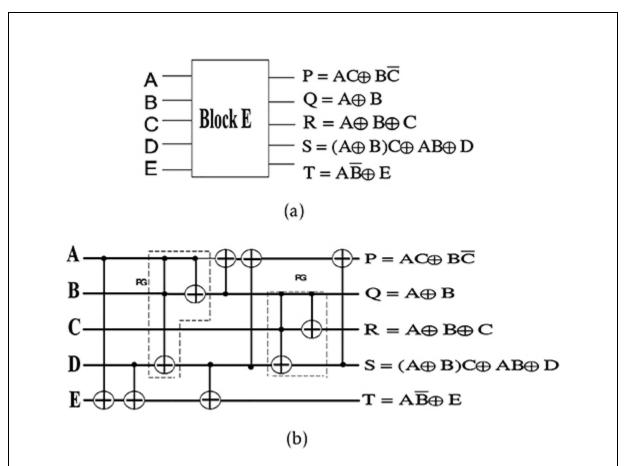

The quantum Tofolli gate is a 3 × 3 gate in which A, B, and C are input vectors and the output vectors are P = A, Q = B, and  $R = AB \oplus C$  logical functions. The quantum Tofolli gate can implement the 'AND' operation when C is set to zero. The quantum Tofolli gate is presented in figure 2.3. The Tofolli gate is an important quantum gate and is widely applied in the construction of quantum circuits.

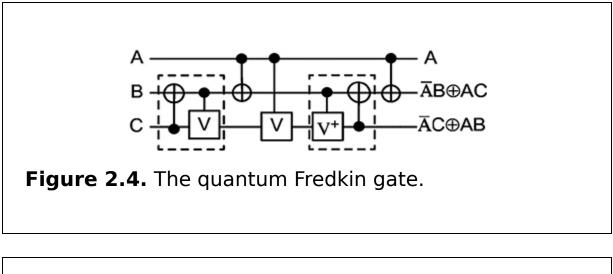

#### 2.2.3 The quantum Fredkin gate

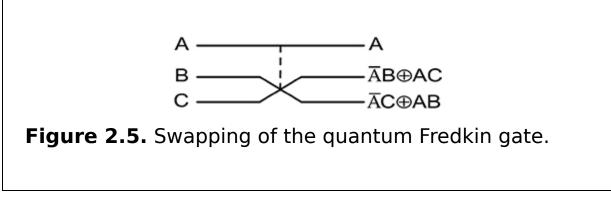

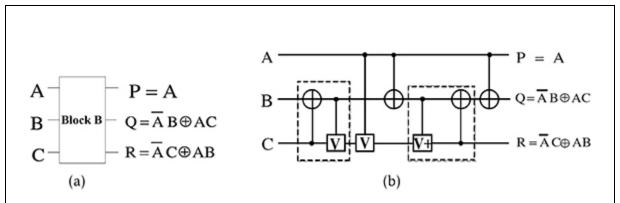

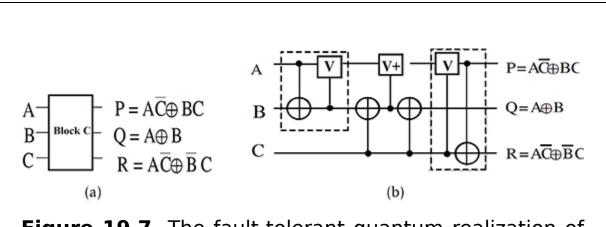

The quantum Fredkin gate is illustrated in figure 2.4, which is a 3 × 3 quantum gate in which A, B, and C are the input vectors and the output vectors are P = A,  $Q = \overline{A}B \oplus AC$ , and  $R = \overline{A}B \oplus AB$  logical functions. One of the important applications of the quantum Fredkin gate is swapping. The input bit A is used as a control bit which decides whether the other two bits will swap or not, which is illustrated in figure 2.5. It shows that the quantum Fredkin gate can swap the values when A is set to 1.

## 2.3 Garbage outputs

In a quantum gate the number of outputs must be equal to the number of inputs. As a consequence, there are usually some outputs which are not required further. They are called garbage outputs. Each garbage output incurs a heavy price. In figure 2.1(b), the output  $|A\rangle$  is the garbage output for the CNOT quantum gate.

## **2.4 Constant inputs**

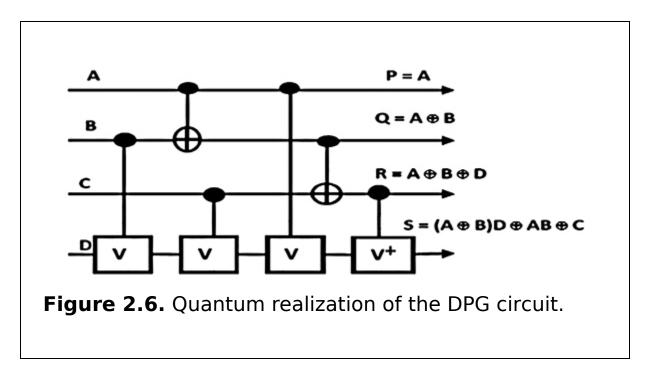

Constant inputs are the inputs which are added to a function to make the one-to-one mapping between inputs and outputs. For example, to perform the adder operation using a double Peres gate (DPG) quantum circuit, the *C* input bit in figure 2.6 has to remain 0 and this input is called the constant input.

### 2.5 Area

The area of a gate is defined by the circuit size. This size varies according to the number of quantum gates of the circuit. As the basic quantum gates are fabricated with quantum dots with size ranging from several to tens of nanometers ( $10^{-9}$  m) in diameter, the size of basic quantum gates ranges from 50 Å-300 Å. The angstrom (Å) is a unit equal to  $10^{-10}$  m (one ten-billionth of a meter) or 0.1 nm. Its symbol is the Swedish letter Å. Quantum circuits can be implemented with the basic quantum gates and the quantum cost of a gate depends on the number of basic quantum gates needed to implement it. Thus the area of a

gate can be defined as follows:  $A = N_q \times S_q$ , where A = area,  $N_q =$  number of quantum gates, and  $S_q =$  size of basic quantum gates. According to the circuit size, the area of the quantum Toffoli gate is ((50 × 5) Å-(300 × 5) Å) = (250 Å-1500 Å), where the number of quantum gates of the quantum Toffoli gate is five.

### 2.6 Power

The power of a gate is defined by the energy consumed. The energy of basic quantum gates is 142.3 meV (microelectronvolts). Quantum circuits can be implemented with basic quantum gates and the quantum cost of a gate depends on the number of basic quantum gates needed to implement it. Thus the power of a gate can be defined as follows, for example: the energy of the Toffoli gate is (5  $\times$  142.3) meV = 711.5 meV, where the number of quantum gates of the quantum Toffoli gate is five.

### 2.7 Delay

The delay represents the critical delay of the circuit. In delay calculations, the logical depth is used as the measure of the delay. The delays of all  $1 \times 1$  and  $2 \times 2$  quantum gates are taken as the unit delay, designated by  $\Delta$ . Any quantum gate can be designed from  $1 \times 1$  and  $2 \times 2$  quantum gates, such as the CNOT quantum, controlled-V, or Controlled-V<sup>+</sup> gates. Thus the delay of a quantum gate can be computed by calculating its logical depth when it is designed using smaller  $1 \times 1$  and  $2 \times 2$  quantum gates. Each  $2 \times 2$  quantum gate in the logic depth contributes to  $1\Delta$  delay. For example, the quantum Toffoli gate requires  $5\Delta$  delay, as shown in figure 2.3.

## 2.8 Depth

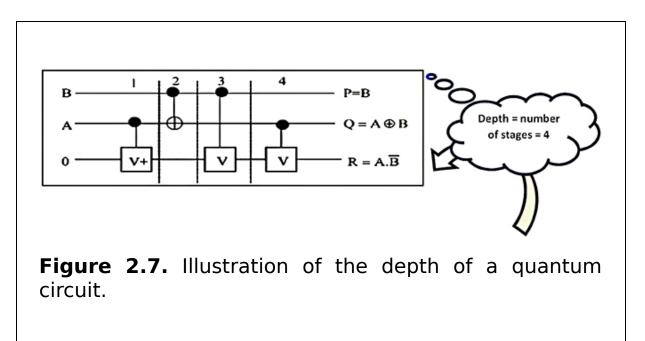

The depth of a quantum circuit is the maximum number of stages or slices where each stage or slice represents a quantum gate or a number of quantum gates along the same vertical line.

A quantum circuit is constructed using different quantum gates. These quantum gates are placed in different input lines. To find the depth of any quantum circuit, it is necessary to divide it into some slices. There may be more than one quantum gate in any slice. The maximum number of slices is considered as the depth of that quantum circuit. For example, consider the Thapliyal Ranganathan (TR) gatebased half subtractor, shown in figure 2.7. This quantum circuit needs four quantum gates to be implemented. Now, to find the depth of this circuit, it will be divided into stages according to the guantum gates. The vertical lines are used to split the circuit into slices. In the first slice there is a controlled- $V^+$  gate, in the second slice there is a CNOT gate, and in the third and fourth slices there are controlled-V gates. This circuit has a maximum of four slices, as numbered in the figure. Thus it can be said that the depth of the circuit is 4.

# 2.9 Quantum cost

The quantum cost of a quantum circuit is the number of basic quantum gates in the circuit. Quantum cost is an important measure of the performance of a quantum circuit. The quantum cost of the basic quantum gates, such as the NOT, CNOT, controlled-V, and controlled-V<sup>+</sup> gates, is considered to be 1. The quantum circuit in figure 2.7 consists of four basic quantum gates and thus the quantum cost of this circuit is 4.

# 2.10 Quantum gate calculation complexity

The quantum gate calculation complexity refers to the number of quantum gates (NOT, CNOT, controlled-V, and controlled-V<sup>+</sup>) used to synthesize the given circuit, with  $\rho$  being the NOT quantum gate calculation complexity,  $\sigma$  the CNOT quantum gate calculation complexity, and  $\Omega$  the controlled-V (controlled-V<sup>+</sup>) gate calculation complexity. For example, the DPG quantum circuit has two CNOT quantum gates and four controlled-V (controlled-V<sup>+</sup>) gates. Therefore, the quantum gate calculation complexity of the DPG quantum circuit is  $2\sigma + 4\Omega$ , which is depicted in figure 2.6.

## 2.11 Summary

Quantum gates and quantum networks offer a very useful language for constructing any quantum computer or quantum multi-particle circuits (which are basically the same). Now the question is, whether it possible to build quantum logic gates or not.

Single-qubit quantum gates are viewed as comparatively easy to implement. For example, a classic quantum optical realization uses elements as qubits and switches their states with laser light pulses of appropriately selected frequency, strength, and duration; any recommended superposition of two selected logical states can be prepared in this way.

Research into quantum computation and all of its all possible variations has become vigorously active and any comprehensive review of the field cannot help but be obsolete as soon as it is written. Here, only some of the very basic knowledge has been provided, hoping that this will serve as a good starting point to enter into the field.

#### Critical thinking questions

- 1. What are the characteristics of qubits?

- 2. How can qubits be controlled?

- 3. How much more powerful is a qubit than a bit?

- 4. How many qubits are there in a quantum computer?

- 5. Design circuits for implementing the quantum AND and quantum OR operations using the basic quantum gates. Write descriptions of the circuits implementing quantum AND and quantum OR operations.

### References

- [1] Oxford quantum http://oxfordquantum.org/ (Accessed: 5 December 2018)

- [2] Balandin A A and Wang K L 1999 Implementation of quantum controlled-not gates using asymmetric semiconductor quantum dots *Quantum Computing* and *Quantum Communications* (Berlin: Springer) pp 460–7

- [3] Landaurer R 1961 Irreversibility and heat generation in the computational process *IBM J. Res. Dev.* **5** 183–91

- [4] Li X, Steel D, Gammon D and Sham L J 2004 Quantum information processing based on optically driven semiconductor quantum dots Opt. Photonics News 15 38-43

- [5] Mohammadi M and Eshghi M 2009 On figures of merit in reversible and quantum logic designs *Quantum Inf. Process.* **8** 297–318

- [6] Monroe C, Meekhof D M, King B E, Itano W M and Wineland D J 1995 Demonstration of a fundamental quantum logic gate *Phys. Rev. Lett.* 75 4714

- [7] Nielsen M A and Chuang I L 2000 *Quantum Computation and Quantum Information* 10th edn (Leiden: Cambridge University Press)

- [8] Shende V V, Prasad A K, Markov I L and Hayes J P 2003 Synthesis of reversible logic circuits *IEEE Trans. Comput.-Aided Des. Integr. Circuits* Syst. 22 710–22

- [9] Toffoli T 1980 Reversible computing International Colloquium on Automata, Languages, and Programming (Berlin: Springer) pp 632-44

- [10] Zhou R-G, Li Y-C and Zhang M-Q 2014 Novel designs for fault tolerant reversible binary coded decimal adders *Int. J. Electron.* **101** 1336–56

**IOP** Publishing

#### Quantum Computing (Second Edition)

A pathway to quantum logic design Hafiz Md Hasan Babu

### Chapter 3

#### The quantum qubit string comparator

#### Learning objectives

- Understand the characteristics of a quantum comparator.

- Understand how a circuit for a two-qubit quantum comparator is built.

- Learn how to use a quantum magnitude comparator.

- Study the comparison between different algorithms for an *n*-qubit string comparator.

- Learn how to construct an *n*-qubit quantum comparator.

- Mention applications of a quantum comparator.

The quantum qubit string comparator enables the implementation of a quantum algorithm using conditional statements, a fundamental structure for designing algorithms. This widens the number of applications where quantum algorithms can be used and at the same time it brings quantum programmers close to some of the successful techniques used in classical computation based on comparisons. For example, constructing a database composed of only prime numbers is possible using the quantum qubit string comparator.

#### **3.1 Characteristics of a quantum comparator**

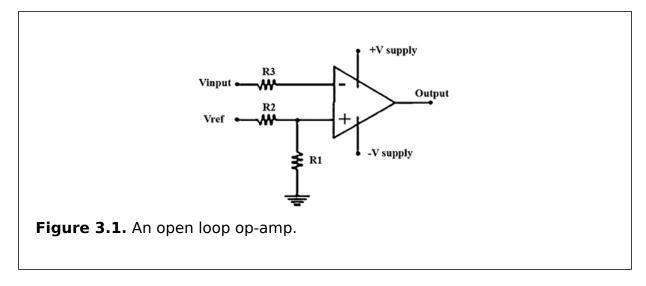

A comparator, as the name suggests, compares a signal on one input of an opamp, as shown in figure 3.1, with a known voltage called the reference voltage on the other input. The comparator is nothing other than an open loop op-amp with two analog inputs (differential input) and one digital output (signal ended output). The op-amp has a very large gain used in an open loop. Hence the output may be in the positive or negative saturation voltage depending upon which input is larger. An op-amp is perfectly suited for comparator applications because of its high input impedance and large open loop gain.

The important characteristics of a quantum comparator are:

- 1. Speed of operation.

- 2. Accuracy.

- 3. Compatibility of output.

#### **3.2 The quantum magnitude comparator**

A quantum magnitude comparator is a logic circuit that first compares the sizes of A and B and then determines the result among A > B, A < B, and A = B. When the two numbers in the comparator circuit are two one-gubit numbers, the result will be only one bit from 0 and 1. Thus the circuit is called a one-gubit magnitude comparator, which is the basis of comparison of the two numbers of the *n* qubits. A quantum qubit string comparator is designed for the quantum qubit string comparator circuit. In this chapter two quantum states are identified by providing a comparison status, such as equality or larger or smaller, after performing a comparison between these states. In addition, this chapter shows that the quantum qubit string comparator enables the implementation of conditional statements in quantum computation, which is a basic structure for designing a comparison algorithm. However, the design requires a huge number of quantum gates, garbage outputs, and constant inputs. Moreover, the design does not show the area and power requirements of the circuit. A quantum comparator circuit is designed by using quantum dot cellular automata. The design requires a huge number of quantum gates and garbage outputs.

An ASIC implementation of a low power area efficient folded binary comparator circuit was invented in 2014. This comparator consists of a precomputation unit and an encoder block. The basic principle is to group the binary inputs into digit sets. The digit sets are sent to the pre-computation unit starting from the most significant digit (MSD) to check for equality, and the computations in the pre-computation unit are stopped at the first digit set which produces a 1 as the output. The corresponding digit set is then sent to the carry look-ahead (CLA) encoder block to find the greater of the two inputs. However, as this is an irreversible comparator circuit, this circuit has huge dynamic power dissipation.

#### 3.3 The design of a quantum comparator

There are two important properties to define a quantum gate, which are as follows:

#### Property 3.1.

Each quantum gate has an unique unitary matrix. A complex square matrix U is *unitary* only if

$$U^*U = UU^* = I,$$

where I is the identity matrix and  $U^*$  is the conjugate transpose of U.

#### Property 3.2.

A quantum state is represented by a state vector in a Hilbert space over complex numbers.

The matrices for the controlled-E and controlled-E<sup>+</sup> gates are

$$M_{ ext{controlled-E}} = egin{pmatrix} -i/2 & -i/2 \ -i/2 & i/2 \end{pmatrix}; \quad M_{ ext{controlled-E}^+} = egin{pmatrix} i/2 & i/2 \ i/2 & -i/2 \end{pmatrix},$$

The conjugate transpose of  $M_{\text{controlled-E}}$  is  $M_{\text{controlled-E}^+}$  and vice versa. After multiplying  $M_{\text{controlled-E}}$  and  $M_{\text{controlled-E}^+}$ , an identity matrix is obtained which is

$$M_{ ext{controlled-E} imes} \; M_{ ext{controlled-E}^+} = egin{pmatrix} -i/2 & -i/2 \ -i/2 & i/2 \end{pmatrix} imes egin{pmatrix} i/2 & i/2 \ i/2 & -i/2 \end{pmatrix} = egin{pmatrix} 1 & 0 \ 0 & 1 \end{pmatrix} = I.$$

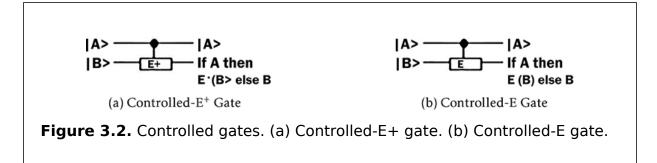

The controlled-E and controlled- $E^+$  gates have a unique matrix which is unitary. Figures 3.2(a) and (b) show diagrams of the controlled-E and controlled- $E^+$  gates.

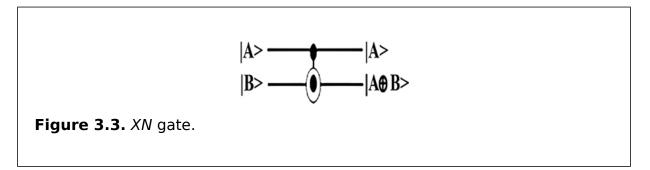

The matrices for the XN ( $M_{\rm XN}$ ) gate and its conjugate transpose ( $M_{\rm XN}{}^{*}$ ) are given below:

| $M_{XN} =$ | $0\ 1\ 0\ 0$    | $M_{XN^*} =$ | $0\ 1\ 0\ 0$    |

|------------|-----------------|--------------|-----------------|

|            | $1 \ 0 \ 0 \ 0$ |              | $1 \ 0 \ 0 \ 0$ |

|            | $0 \ 0 \ 1 \ 0$ |              | $0 \ 0 \ 1 \ 0$ |

|            | $0 \ 0 \ 0 \ 1$ |              | $0 \ 0 \ 0 \ 1$ |

After multiplying  $M_{XN}$  and  $M_{XN}^{*}$ , an identity matrix is obtained which is given below:

Thus the XN gate has a unique matrix which is unitary. Figure 3.3 shows a diagram of the XN gate.

Algorithm 3.1 describes the computational process for the designed method for the proof of the time complexity. The technique of comparison of the comparator has four basic steps. First, sort the two numbers and also calculate their middle bit position. Second, find Ex-OR of the middle bit position and decide based on that value whether to go to the left half or to the right half of the numbers. Third, repeat the second step after entering into the left or right half and also calculate Ex-OR of the other bits at the same time. Finally, take a decision if any value of Ex-OR is  $|1\rangle$  as to which number is greater, otherwise carry out Ex-NOR to find whether they are equal or not.

#### Property 3.3.

Algorithm for the comparison technique for an *n*-quantum bit string comparator which requires a time complexity of  $O(2(2 + \log n))$ .

*Proof.* Let *n* be the number of qubits of two strings. To sort two strings of *n* qubits in parallel using merge sorting, the total time complexity in the best case is  $O(\log n)$ . Now each string is divided into half (*n*/2) of the original string when the comparison technique works in each time. Thus it reduces the working space by half. In the worst case, the comparison technique operations need to be

executed on both the left and right halves of the two *n*-qubit strings, where the time required for one half is the run time  $(T(\mid n/2 \mid))$  for half (n/2) of the *n*-qubit string using the comparison technique, and the time required for the other half is the same, which is treated as the time for copying the same operations in the other half of the string. In contrast, in the best case only the left/right half operations need to be executed. The positions of the qubit strings are stored in two different arrays. When comparing two qubits, the two arrays containing the qubit positions need to be accessed in parallel and the complexity of an array access is O(1). According to the algorithm, Ex-OR of the midpoint of the sorted strings is used for comparison. Hence we need to access the two unsorted arrays of strings again and this also has time complexities. Thus the recurrence of the comparison technique in the best case can be specified as

$$T(n) = T(\mid n/2 \mid) + 1,$$

where T(n) denotes the run time of the comparison technique, T(|n/2|) is the time required to perform operations on the left/right half of the *n*-qubit strings, *n* is the length of the qubit strings, and a constant 1 (one) is the time for midpoint qubit operation of the qubit string.

```

INPUT: INPUT: Two n-qubits strings |A\rangle = |A_n\rangle |A_{n-1}\rangle \dots |A_0\rangle and |B\rangle =

|B_n>|B_{n-1}> \dots |B_0>

OUTPUT: |A>> |B> or |A>< |B> or |A>= |B>

1: Begin

2: |A[i] > = Array containing nqubits of first string

3: |B[i]>=Array containing nqubits of second string

4: |SA[i] > =Sorted |A[i] >

5: |SB[i]\rangle=Sorted |B[i]\rangle

6: n=Size of array

7: mid = |\frac{n}{2}|

8: Ex - O\overline{R}[mid] = |SA[mid] > \oplus |SB[mid] >

9:

If .Ex-OR[mid]=0 then

Find Ex-OR values of left half of |SA[i]> and |SB[i]>s.t.i<mid

10:

If Ex-OR of left side |SA[i]> and |SB[i]> is 0 then

11:

Find Ex-OR values of left half of |A[i]> and |B[i]>s.t.i<mid

12:

If Ex-OR of any position is 1 and |A[i] >> |B[i] >, then

13:

|A>>|B>

14:

Else If Ex-OR of any position is 1 and |A[i]\rangle < |B[i]\rangle, then

15:

|B>>|A>

16:

17:

Else goto Step 19

End If

18:

Repeat Steps12 to 16 for right side, i.e., mid<i<=n

19:

Else goto Step26

20:

End If

21:

End If

22.

23: Else

Repeat Steps 10-20 for right half of the numbers |SA[i]> and

24:

|SB[i]>s.t.i>mid

25: End Else

26: If X-NOR of both halves of |A[i]> and |B[i]> is 1, where |SA[mid]>\oplus

|SB[mid]>=0, then

|A> = |B>

27:

28: End If

29: End

```

Algorithm 3.1. Algorithm of the comparison technique.

#### Guess

It is assumed that the solution of the recurrence is  $T(n) = O(\log n)$ , i.e. it is true iff  $T(n) \leq c(\log(n))$ , where c > 0 is a constant.

Proof by substitution. Assume that this bound holds for all positive m < n in the particular  $m = \lfloor n/2 \rfloor$ , where n is the number of qubits and m is a constant term. It yields that

$$T(n/2) \leqslant c(\log(\mid n/2 \mid)).$$

By substituting into the recurrence,

$$egin{aligned} T(n) \leqslant c(\log(\mid n/2 \mid)) + 1 \ &= c(\log(n)) - c(\log(2)) + 1 \ &= c(\log(n)) - c + 1 \ &\leqslant c(\log(n)) ext{ as long as } c \geqslant 1. \end{aligned}$$

Thus,  $T(n) \leq c(\log(n))$ , that is,  $T(n) = O(\log n)$ . Therefore, the total time complexity of the comparison algorithm in the best case is sorting time + comparison time + array of position access time + array of unsorted qubits access time:

$$= O(\log n) + O(\log n) + O(2) + O(2) \\= O(2(2 + \log n)).$$

Thus this completes the proof and the property 3.3 is true.

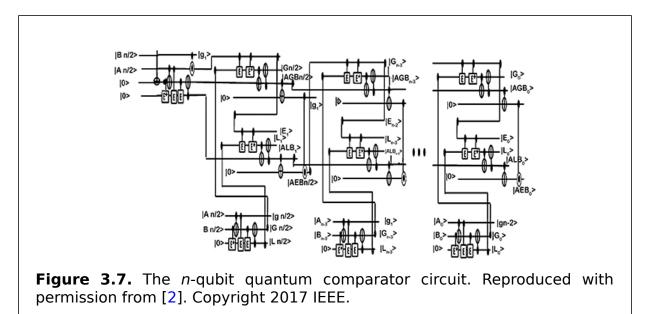

The design of a quantum comparator consists of two circuits: the midpoint qubit comparison (MQC) circuit and rest qubit comparison (RQC) circuit. First, the most significant quantum bits are compared using the MQC circuit. Second, the rest of the qubits are compared using the RQC circuit, where each qubit comparison is performed by one RQC circuit. In figure 3.4 the MQC circuit consists of two controlled-E gates, one controlled-E<sup>+</sup> gate, three CNOT gates, and one *XN* gate. This circuit generates the following three outputs and produces one garbage output which is  $|g_1\rangle$ :

$$egin{aligned} &| E_{n/2}

angle &= | A_{n/2}

angle \odot | B_{n/2}

angle \ &| G_{n/2}

angle &= | A_{n/2} \overline{B_{n/2}} \ &| L_{n/2}

angle &= | \overline{A_{n/2}} B_{n/2}

angle. \end{aligned}$$

.1)

IB(n/2)>

IA(n/2)>

IO>

IO>

IO>

IEFEE

IEFUIT IL(n/2)>

IL(n/2)>

Figure 3.4. The MQC circuit. Reproduced with permission from [2].

Copyright 2017 IEEE.

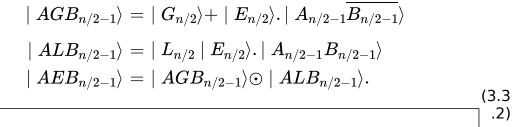

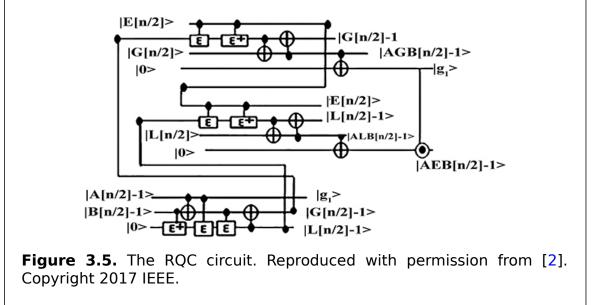

In figure 3.5 the RQC circuit consists of four controlled-E gates, three controlled-E<sup>+</sup> gates, one *XN* gate, and eight CNOT gates. This circuit generates three outputs, and it produces two garbage outputs which are  $|g_1\rangle$  and  $|g_2\rangle$ :

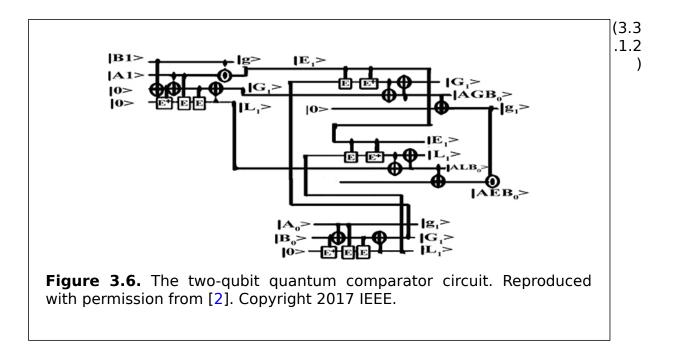

#### 3.3.1 Example

To construct a two-qubit quantum comparator circuit, one MQC circuit and one RQC circuit are needed to perform the greater than, less than, and equality operations. In figure 3.6 the detailed quantum circuit for a two-qubit comparator is shown. The midpoint is the qubits in position 1. At first, the midpoint qubits  $|A_1\rangle$  and  $|B_1\rangle$  are applied in an MQC circuit to generate the following outputs:

$$| E_1

angle = | A_1

angle \odot | B_1

angle$$

$| G_1

angle = | A_1 B_1

angle 3$

$| L_1

angle = | A_1 B_1

angle.$  (3.3)

Then the outputs of the MQC circuit ( $|E_1\rangle$ ,  $|G_1\rangle$ ,  $|L_1\rangle$ ) and the rest of the .1.1 qubits ( $|A_0\rangle$ ,  $|B_0\rangle$ ) are used as inputs to the next circuit which is the RQC ) circuit. This circuit produces the final outputs

$$egin{array}{ll} |AGB_0

angle = |~G_1

angle + |~E_1

angle. |~A_0(B_0)

angle \ |~ALB_0

angle = |~L_1

angle + |~E_1

angle. |~(A_0)B_0

angle \ |~AEB_0

angle = |~AGB_0

angle \odot |~ALB_0

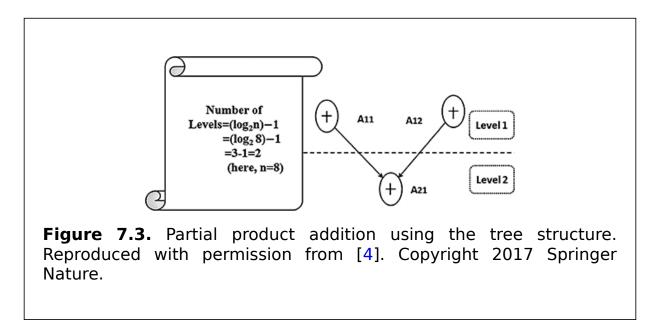

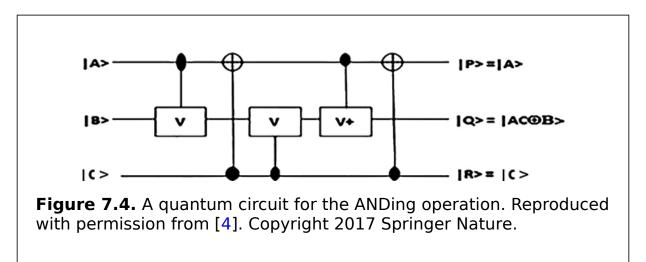

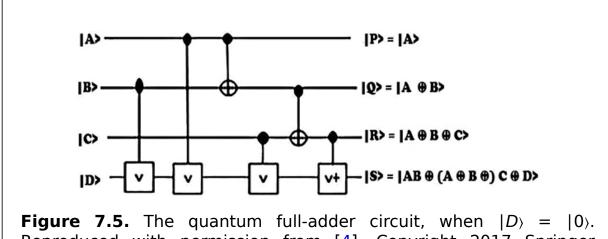

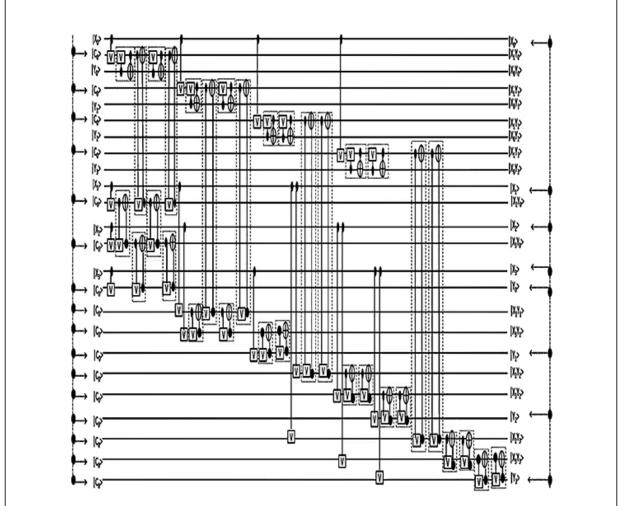

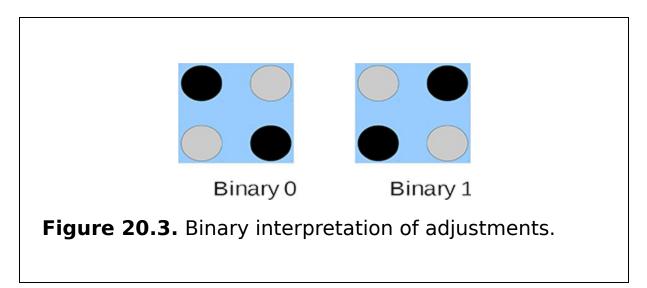

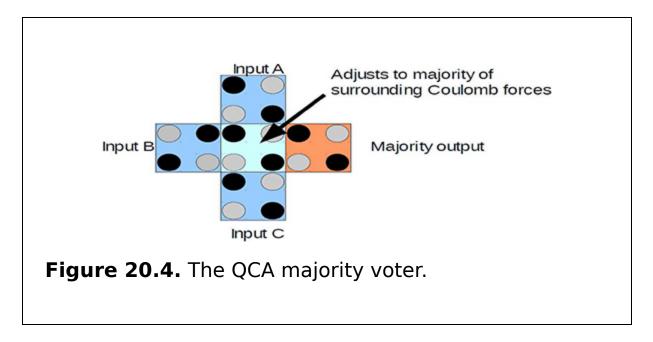

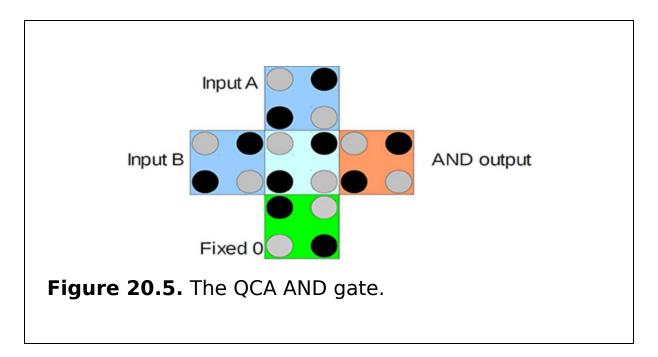

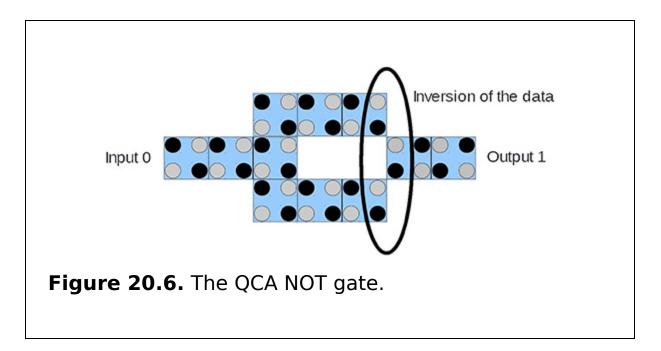

angle. \end{array}$$