# Machine Learning for VLSI Chip Design

#### Scrivener Publishing

100 Cummings Center, Suite 541J Beverly, MA 01915-6106

Publishers at Scrivener Martin Scrivener (martin@scrivenerpublishing.com) Phillip Carmical (pcarmical@scrivenerpublishing.com)

# Machine Learning for VLSI Chip Design

Edited by Abhishek Kumar Suman Lata Tripathi and K. Srinivasa Rao

This edition first published 2023 by John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, USA and Scrivener Publishing LLC, 100 Cummings Center, Suite 541J, Beverly, MA 01915, USA © 2023 Scrivener Publishing LLC

For more information about Scrivener publications please visit www.scrivenerpublishing.com.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, except as permitted by law. Advice on how to obtain permission to reuse material from this title is available at http://www.wiley.com/go/permissions.

#### Wiley Global Headquarters

111 River Street, Hoboken, NJ 07030, USA

For details of our global editorial offices, customer services, and more information about Wiley products visit us at www.wiley.com.

#### Limit of Liability/Disclaimer of Warranty

While the publisher and authors have used their best efforts in preparing this work, they make no representations or warranties with respect to the accuracy or completeness of the contents of this work and specifically disclaim all warranties, including without limitation any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives, written sales materials, or promotional statements for this work. The fact that an organization, website, or product is referred to in this work as a citation and/or potential source of further information does not mean that the publisher and authors endorse the information or services the organization, website, or product may provide or recommendations it may make. This work is sold with the understanding that the publisher is not engaged in rendering professional services. The advice and strategies contained herein may not be suitable for your situation. You should consult with a specialist where appropriate. Neither the publisher nor authors shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages. Further, readers should be aware that websites listed in this work may have changed or disappeared between when this work was written and when it is read.

#### Library of Congress Cataloging-in-Publication Data

ISBN 9781119910398

Front cover images supplied by Pixabay.com Cover design by Russell Richardson

Set in size of 11pt and Minion Pro by Manila Typesetting Company, Makati, Philippines

Printed in the USA

10 9 8 7 6 5 4 3 2 1

# Contents

| Lis                    | st of C                                                                                                                                | Contributors                                               | xiii |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|--|--|--|

| Pr                     | eface                                                                                                                                  |                                                            | xix  |  |  |  |

| 1                      | Applications of VLSI Design in Artificial Intelligence<br>and Machine Learning<br>Imran Ullah Khan, Nupur Mittal and Mohd. Amir Ansari |                                                            |      |  |  |  |

|                        |                                                                                                                                        | Introduction                                               | 2    |  |  |  |

|                        | 1.2                                                                                                                                    | Artificial Intelligence                                    | 4    |  |  |  |

|                        | 1.3 Artificial Intelligence & VLSI (AI and VLSI)                                                                                       |                                                            |      |  |  |  |

|                        |                                                                                                                                        | Applications of AI                                         | 4    |  |  |  |

| 1.5 Machine Learning   |                                                                                                                                        |                                                            |      |  |  |  |

| 1.6 Applications of ML |                                                                                                                                        |                                                            |      |  |  |  |

|                        |                                                                                                                                        | 1.6.1 Role of ML in Manufacturing Process                  | 6    |  |  |  |

|                        |                                                                                                                                        | 1.6.2 Reducing Maintenance Costs and Improving Reliability | 6    |  |  |  |

|                        |                                                                                                                                        | 1.6.3 Enhancing New Design                                 | 7    |  |  |  |

|                        |                                                                                                                                        | Role of ML in Mask Synthesis                               | 7    |  |  |  |

|                        | 1.8                                                                                                                                    | Applications in Physical Design                            | 8    |  |  |  |

|                        |                                                                                                                                        | 1.8.1 Lithography Hotspot Detection                        | 9    |  |  |  |

|                        |                                                                                                                                        | 1.8.2 Pattern Matching Approach                            | 9    |  |  |  |

|                        |                                                                                                                                        | Improving Analysis Correlation                             | 10   |  |  |  |

|                        |                                                                                                                                        | Role of ML in Data Path Placement                          | 12   |  |  |  |

|                        |                                                                                                                                        | Role of ML on Route Ability Prediction                     | 12   |  |  |  |

|                        | 1.12                                                                                                                                   | Conclusion                                                 | 13   |  |  |  |

|                        |                                                                                                                                        | References                                                 | 14   |  |  |  |

| 2                      |                                                                                                                                        | gn of an Accelerated Squarer Architecture Based            |      |  |  |  |

|                        | on Yavadunam Sutra for Machine Learning                                                                                                |                                                            |      |  |  |  |

|                        | A.V. Ananthalakshmi, P. Divyaparameswari and P. Kanimozhi                                                                              |                                                            |      |  |  |  |

|                        |                                                                                                                                        | Introduction                                               | 20   |  |  |  |

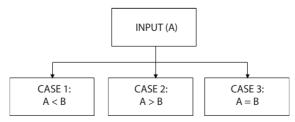

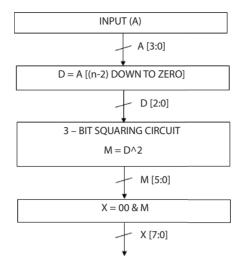

|                        | 2.2                                                                                                                                    | Methods and Methodology                                    | 21   |  |  |  |

|                        |                                                                                                                                        | 2.2.1 Design of an n-Bit Squaring Circuit Based            |      |  |  |  |

|                        |                                                                                                                                        | on (n-1)-Bit Squaring Circuit Architecture                 | 22   |  |  |  |

|   |                            | 2.2.1.1 Architecture for Case 1: A < B                | 22 |  |  |

|---|----------------------------|-------------------------------------------------------|----|--|--|

|   |                            | 2.2.1.2 Architecture for Case 2: A > B                | 24 |  |  |

|   |                            | 2.2.1.3 Architecture for Case 3: $A = B$              | 24 |  |  |

|   | 2.3                        | Results and Discussion                                | 25 |  |  |

|   | 2.4                        | Conclusion                                            | 29 |  |  |

|   |                            | References                                            | 30 |  |  |

| 3 | Ma                         | chine Learning-Based VLSI Test and Verification       | 33 |  |  |

|   | Jyot                       | ti Kandpal                                            |    |  |  |

|   | 3.1                        | Introduction                                          | 33 |  |  |

|   | 3.2                        | The VLSI Testing Process                              | 35 |  |  |

|   |                            | 3.2.1 Off-Chip Testing                                | 35 |  |  |

|   |                            | 3.2.2 On-Chip Testing                                 | 35 |  |  |

|   |                            | 3.2.3 Combinational Circuit Testing                   | 36 |  |  |

|   |                            | 3.2.3.1 Fault Model                                   | 36 |  |  |

|   |                            | 3.2.3.2 Path Sensitizing                              | 36 |  |  |

|   |                            | 3.2.4 Sequential Circuit Testing                      | 36 |  |  |

|   |                            | 3.2.4.1 Scan Path Test                                | 36 |  |  |

|   |                            | 3.2.4.2 Built-In-Self Test (BIST)                     | 36 |  |  |

|   |                            | 3.2.4.3 Boundary Scan Test (BST)                      | 37 |  |  |

|   |                            | 3.2.5 The Advantages of VLSI Testing                  | 37 |  |  |

|   | 3.3                        | Machine Learning's Advantages in VLSI Design          | 38 |  |  |

|   |                            | 3.3.1 Ease in the Verification Process                | 38 |  |  |

|   |                            | 3.3.2 Time-Saving                                     | 38 |  |  |

|   |                            | 3.3.3 3Ps (Power, Performance, Price)                 | 38 |  |  |

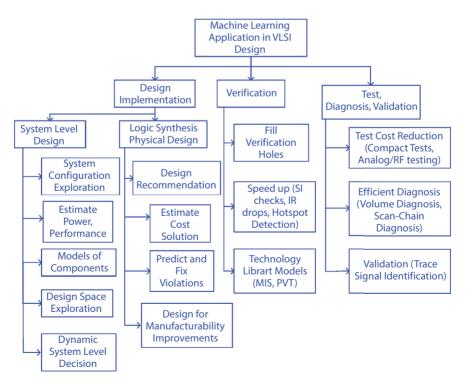

|   | 3.4                        | Electronic Design Automation (EDA)                    | 39 |  |  |

|   |                            | 3.4.1 System-Level Design                             | 40 |  |  |

|   |                            | 3.4.2 Logic Synthesis and Physical Design             | 42 |  |  |

|   |                            | 3.4.3 Test, Diagnosis, and Validation                 | 43 |  |  |

|   | 3.5                        | Verification                                          | 44 |  |  |

|   | 3.6                        | Challenges                                            |    |  |  |

|   | 3.7                        | Conclusion                                            | 47 |  |  |

|   |                            | References                                            | 48 |  |  |

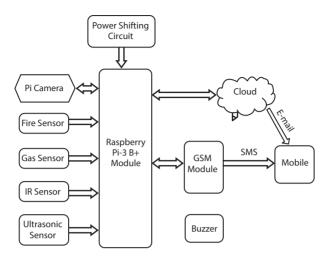

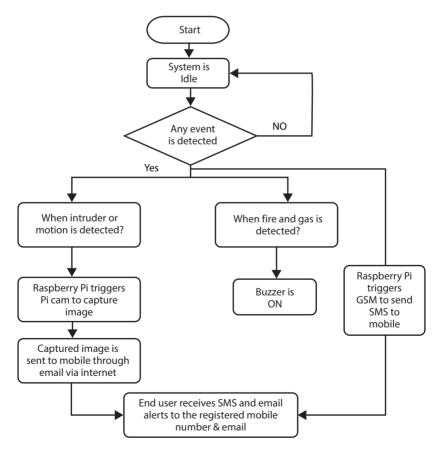

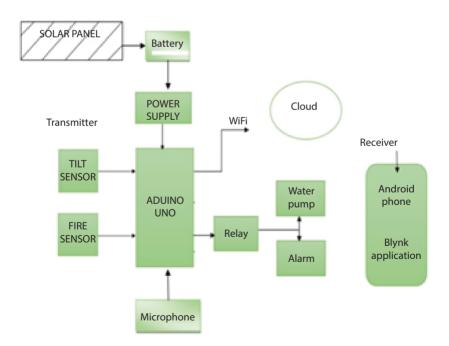

| 4 |                            | IoT-Based Smart Home Security Alert System            |    |  |  |

|   | for Continuous Supervision |                                                       |    |  |  |

|   | Raj                        | Rajeswari, N. Vinod Kumar, K. M. Suresh, N. Sai Kumar |    |  |  |

|   | and                        | l K. Girija Sravani                                   |    |  |  |

|   | 4.1                        | Introduction                                          | 52 |  |  |

|   | 4.2                        | Literature Survey                                     | 53 |  |  |

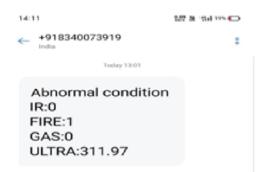

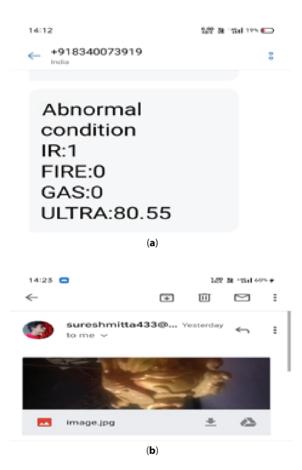

|   | 4.3                        | Results and Discussions                               | 54 |  |  |

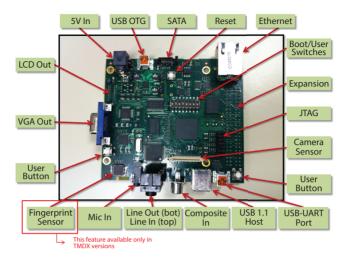

|   |             | 4.3.1   | Raspberry Pi-3 B+Module                              | 54  |

|---|-------------|---------|------------------------------------------------------|-----|

|   |             | 4.3.2   | Pi Camera                                            | 56  |

|   |             | 4.3.3   | Relay                                                | 56  |

|   |             | 4.3.4   | Power Source                                         | 56  |

|   |             | 4.3.5   | Sensors                                              | 56  |

|   |             |         | 4.3.5.1 IR & Ultrasonic Sensor                       | 56  |

|   |             |         | 4.3.5.2 Gas Sensor                                   | 56  |

|   |             |         | 4.3.5.3 Fire Sensor                                  | 57  |

|   |             |         | 4.3.5.4 GSM Module                                   | 57  |

|   |             |         | 4.3.5.5 Buzzer                                       | 57  |

|   |             |         | 4.3.5.6 Cloud                                        | 57  |

|   |             |         | 4.3.5.7 Mobile                                       | 57  |

|   | 4.4         |         | lusions                                              | 62  |

|   |             | Refer   | ences                                                | 62  |

| 5 | A D         | etailed | Roadmap from Conventional-MOSFET                     |     |

|   |             |         | re-MOSFET                                            | 65  |

|   | <i>P. K</i> | iran Ki | umar, B. Balaji, M. Suman, P. Syam Sundar,           |     |

|   | Е. Р        | admaj   | a and K. Girija Sravani                              |     |

|   | 5.1         | Intro   | duction                                              | 66  |

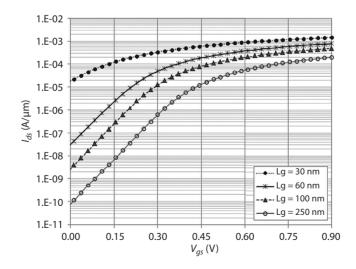

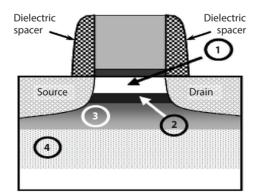

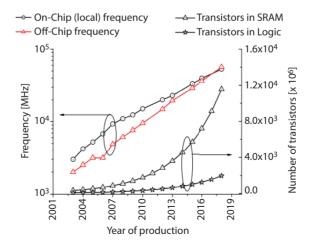

|   | 5.2         | Scalin  | ng Challenges Beyond 100nm Node                      | 67  |

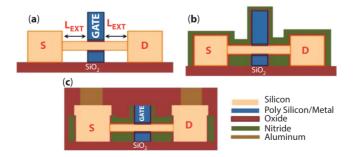

|   | 5.3         | Alteri  | nate Concepts in MOFSETs                             | 69  |

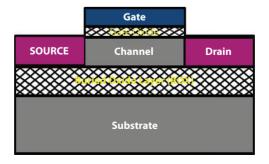

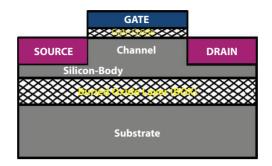

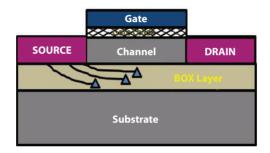

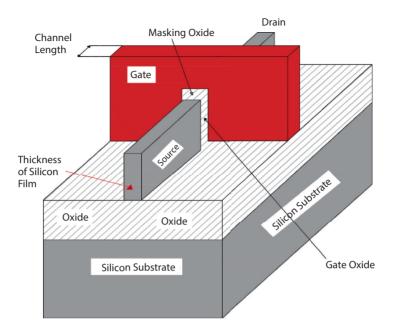

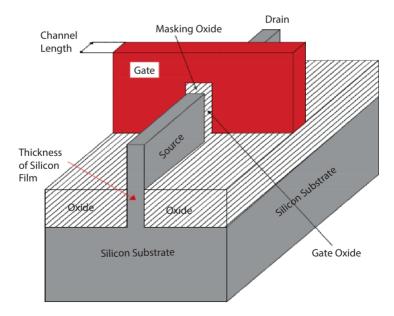

|   | 5.4         | Thin-   | Body Field-Effect Transistors                        | 70  |

|   |             | 5.4.1   | 0                                                    | 71  |

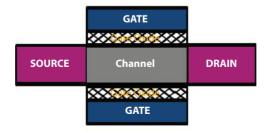

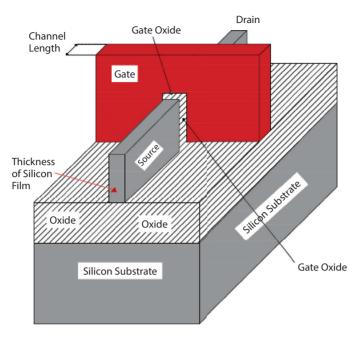

|   |             |         | Multiple-Gate Ultrathin-Body Field-Effect Transistor | 73  |

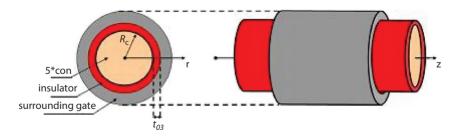

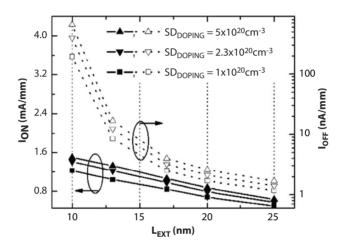

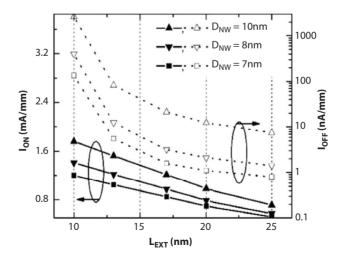

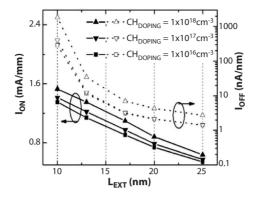

|   | 5.5         |         | ET Devices                                           | 74  |

|   | 5.6         | GAA     | Nanowire-MOSFETS                                     | 77  |

|   | 5.7         |         | lusion                                               | 86  |

|   |             | Refer   | ences                                                | 86  |

| 6 | Gat         | e All A | round MOSFETs-A Futuristic Approach                  | 95  |

|   | Ritu        | ı Yadav | and Kiran Ahuja                                      |     |

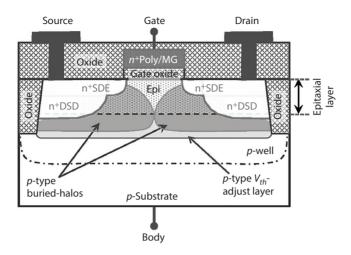

|   | 6.1         | Intro   | duction                                              | 95  |

|   |             | 6.1.1   | Semiconductor Technology: History                    | 96  |

|   | 6.2         | Impo    | rtance of Scaling in CMOS Technology                 | 98  |

|   |             |         | Scaling Rules                                        | 99  |

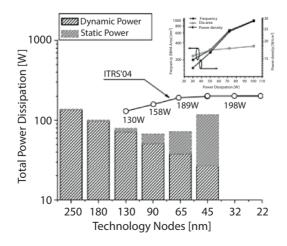

|   |             |         | The End of Planar Scaling                            | 100 |

|   |             | 6.2.3   | Enhance Power Efficiency                             | 101 |

|   |             | 6.2.4   | Scaling Challenges                                   | 102 |

|   |             |         | 6.2.4.1 Poly Silicon Depletion Effect                | 102 |

|   |             |         | 6.2.4.2 Quantum Effect                               | 103 |

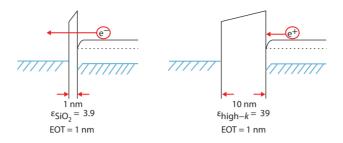

|   |                                                         |         | 6.2.4.3   | Gate Tunneling                           | 103 |  |  |

|---|---------------------------------------------------------|---------|-----------|------------------------------------------|-----|--|--|

|   |                                                         | 6.2.5   | Horizor   | ntal Scaling Challenges                  | 103 |  |  |

|   |                                                         |         | 6.2.5.1   | Threshold Voltage Roll-Off               | 103 |  |  |

|   |                                                         |         | 6.2.5.2   | Drain Induce Barrier Lowering (DIBL)     | 103 |  |  |

|   |                                                         |         | 6.2.5.3   | Trap Charge Carrier                      | 104 |  |  |

|   |                                                         |         | 6.2.5.4   | Mobility Degradation                     | 104 |  |  |

|   | 6.3                                                     | Reme    |           | caling Challenges                        | 104 |  |  |

|   |                                                         | 6.3.1   | By Chai   | nnel Engineering (Horizontal)            | 104 |  |  |

|   |                                                         |         | 6.3.1.1   | Shallow S/D Junction                     | 105 |  |  |

|   |                                                         |         | 6.3.1.2   | Multi-Material Gate                      | 105 |  |  |

|   |                                                         | 6.3.2   | By Gate   | Engineering (Vertical)                   | 105 |  |  |

|   |                                                         |         | 6.3.2.1   | High-K Dielectric                        | 105 |  |  |

|   |                                                         |         | 6.3.2.2   | Metal Gate                               | 105 |  |  |

|   |                                                         |         | 6.3.2.3   | Multiple Gate                            | 105 |  |  |

|   | 6.4                                                     |         |           | C in CMOS Miniaturization                | 106 |  |  |

|   | 6.5                                                     | Curre   | ent Mosfe | t Technologies                           | 108 |  |  |

|   | 6.6                                                     | Conc    | lusion    |                                          | 108 |  |  |

|   |                                                         | Refer   | ences     |                                          | 109 |  |  |

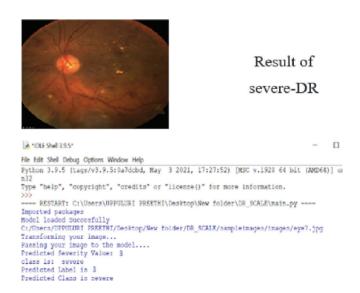

| 7 | Investigation of Diabetic Retinopathy Level Based       |         |           |                                          |     |  |  |

|   |                                                         |         |           | ural Network Using Fundus Images         | 113 |  |  |

|   | <i>K</i> . <i>S</i>                                     | Sasi Bh | ushan, U. | Preethi, P. Naga Sai Navya, R. Abhilash, |     |  |  |

|   |                                                         |         |           | rija Sravani                             |     |  |  |

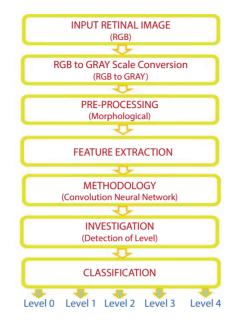

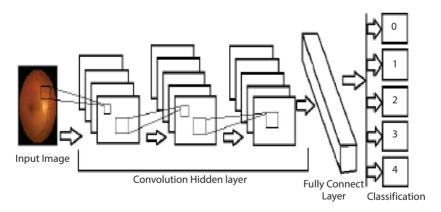

|   | 7.1                                                     |         | duction   |                                          | 114 |  |  |

|   | 7.2                                                     | The P   | roposed   | Methodology                              | 115 |  |  |

|   | 7.3                                                     |         |           | ption and Feature Extraction             | 116 |  |  |

|   |                                                         | 7.3.1   |           | on of Datasets                           | 116 |  |  |

|   |                                                         |         | Preproc   | 0                                        | 116 |  |  |

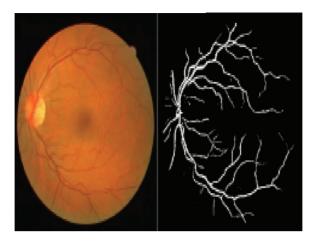

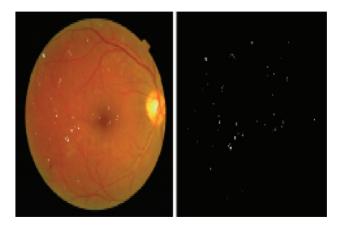

|   |                                                         | 7.3.3   | Detectio  | on of Blood Vessels                      | 117 |  |  |

|   |                                                         |         |           | neurysm Detection                        | 118 |  |  |

|   | 7.4                                                     | Resul   | ts and Di | scussions                                | 120 |  |  |

|   | 7.5                                                     |         | lusions   |                                          | 123 |  |  |

|   |                                                         | Refer   | ences     |                                          | 123 |  |  |

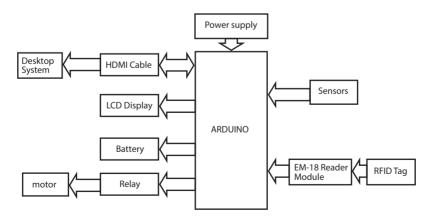

| 8 | Anti-Theft Technology of Museum Cultural Relics         |         |           |                                          |     |  |  |

|   | Using RFID Technology                                   |         |           |                                          |     |  |  |

|   | <b>B. R</b>                                             | Ramesh  | Reddy, F  | K. Bhargav Manikanta,                    |     |  |  |

|   | P.V.V.N.S. Jaya Sai, R. Mohan Chandra, M. Greeshma Vyas |         |           |                                          |     |  |  |

|   |                                                         |         | ija Srava | ni                                       |     |  |  |

|   | 8.1                                                     | Intro   | duction   |                                          | 128 |  |  |

|   | 8.2                                                          | Litera       | iture Survey                         | 128        |  |  |

|---|--------------------------------------------------------------|--------------|--------------------------------------|------------|--|--|

|   | 8.3                                                          | Softw        | are Implementation                   | 129        |  |  |

|   | 8.4                                                          |              | ponents                              | 130        |  |  |

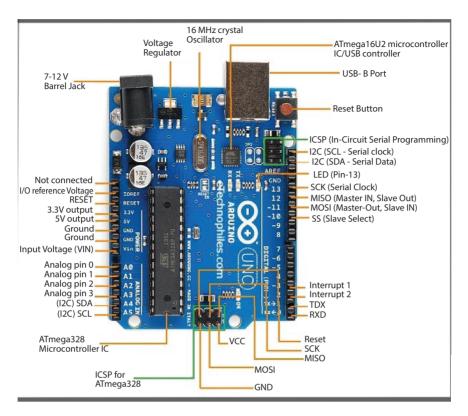

|   |                                                              | 8.4.1        | Arduino UNO                          | 130        |  |  |

|   |                                                              | 8.4.2        | EM18 Reader Module                   | 130        |  |  |

|   |                                                              | 8.4.3        | RFID Tag                             | 131        |  |  |

|   |                                                              | 8.4.4        | LCD Display                          | 131        |  |  |

|   |                                                              | 8.4.5        | Sensors                              | 132        |  |  |

|   |                                                              |              | 8.4.5.1 Fire Sensor                  | 132        |  |  |

|   |                                                              |              | 8.4.5.2 IR Sensor                    | 132        |  |  |

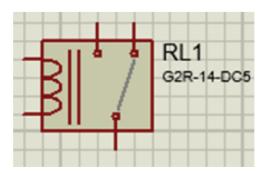

|   |                                                              | 8.4.6        | Relay                                | 133        |  |  |

|   | 8.5                                                          | Work         | ing Principle                        | 134        |  |  |

|   |                                                              |              | Working Principle                    | 134        |  |  |

|   | 8.6                                                          |              | ts and Discussions                   | 135        |  |  |

|   | 8.7                                                          | Conc         | lusions                              | 137        |  |  |

|   |                                                              | Refer        | ences                                | 138        |  |  |

| 9 | Sma                                                          | art Irrig    | gation System Using Machine Learning |            |  |  |

| - |                                                              | 139          |                                      |            |  |  |

|   | Techniques<br>B. V. Anil Sai Kumar, Suryavamsham Prem Kumar, |              |                                      |            |  |  |

|   | Kon                                                          |              |                                      |            |  |  |

|   |                                                              | Introduction |                                      |            |  |  |

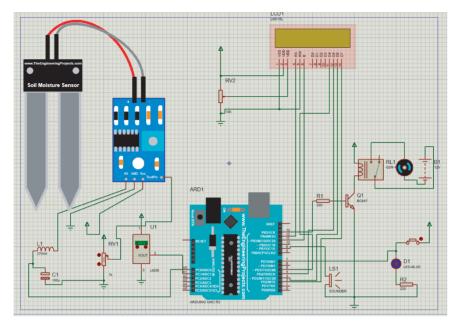

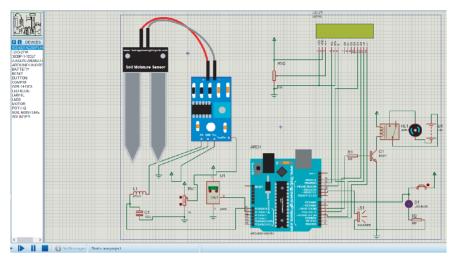

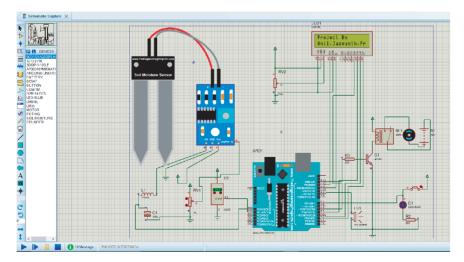

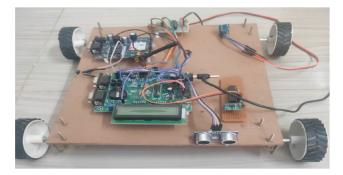

|   | 9.2                                                          | Hardy        | ware Module                          | 139<br>141 |  |  |

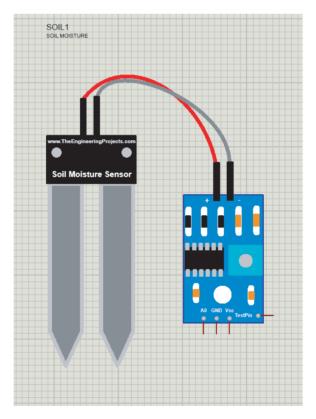

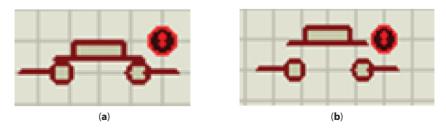

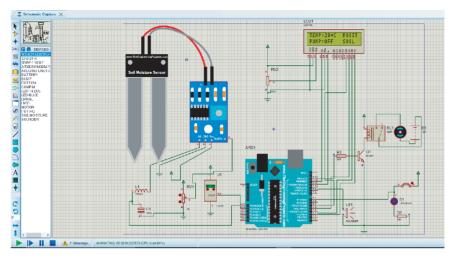

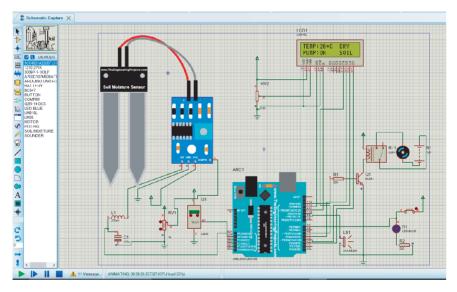

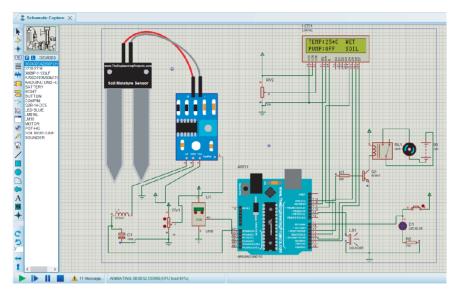

|   |                                                              | 9.2.1        | Soil Moisture Sensor                 | 141        |  |  |

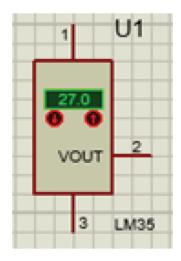

|   |                                                              | 9.2.2        | LM35-Temperature Sensor              | 143        |  |  |

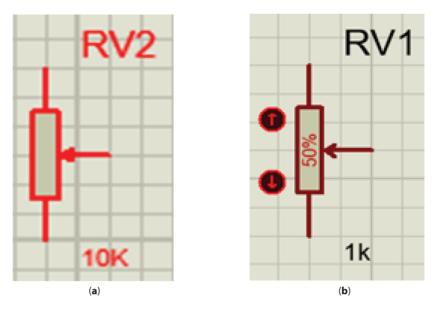

|   |                                                              |              | POT Resistor                         | 143        |  |  |

|   |                                                              | 9.2.4        | BC-547 Transistor                    | 143        |  |  |

|   |                                                              | 9.2.5        | Sounder                              | 144        |  |  |

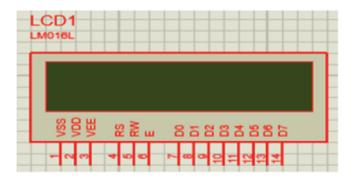

|   |                                                              | 9.2.6        | LCD 16x2                             | 145        |  |  |

|   |                                                              | 9.2.7        | Relay                                | 145        |  |  |

|   |                                                              | 9.2.8        | Push Button                          | 146        |  |  |

|   |                                                              | 9.2.9        | LED                                  | 146        |  |  |

|   |                                                              | 9.2.10       | Motor                                | 147        |  |  |

|   | 9.3                                                          | Softw        | rare Module                          | 148        |  |  |

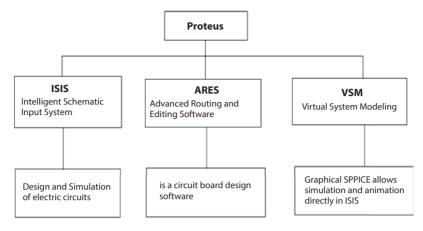

|   |                                                              | 9.3.1        | Proteus Tool                         | 148        |  |  |

|   |                                                              | 9.3.2        | Arduino Based Prototyping            | 149        |  |  |

|   | 9.4                                                          | Mach         | ine Learning (Ml) Into Irrigation    | 155        |  |  |

|   | 9.5                                                          | Conclusion   |                                      |            |  |  |

|   |                                                              | References   |                                      |            |  |  |

**x** Contents

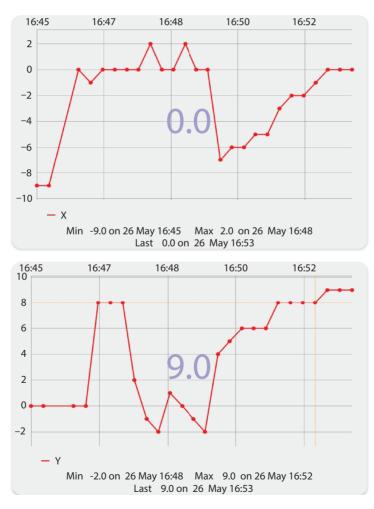

| 10 | Desig                                                    | gn of Smart Wheelchair with Health Monitoring System | 161 |  |  |  |  |

|----|----------------------------------------------------------|------------------------------------------------------|-----|--|--|--|--|

|    | Narendra Babu Alur, Kurapati Poorna Durga, Boddu Ganesh, |                                                      |     |  |  |  |  |

|    | Manda Devakaruna, Lakkimsetti Nandini, A. Praneetha,     |                                                      |     |  |  |  |  |

|    | T. Satyanarayana and K. Girija Sravani                   |                                                      |     |  |  |  |  |

|    | 10.1 Introduction                                        |                                                      |     |  |  |  |  |

|    | 10.2                                                     | Proposed Methodology                                 | 163 |  |  |  |  |

|    | 10.3                                                     | The Proposed System                                  | 164 |  |  |  |  |

|    | 10.4                                                     | Results and Discussions                              | 168 |  |  |  |  |

|    | 10.5                                                     | Conclusions                                          | 169 |  |  |  |  |

|    |                                                          | References                                           | 169 |  |  |  |  |

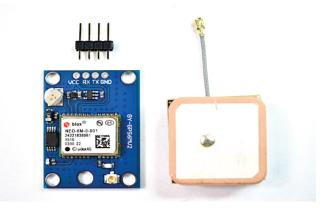

| 11 | Desig                                                    | gn and Analysis of Anti-Poaching Alert System        |     |  |  |  |  |

|    | for R                                                    | ed Sandalwood Safety                                 | 171 |  |  |  |  |

|    | K. Rı                                                    | ani Rudrama, Mounika Ramala,                         |     |  |  |  |  |

|    | Poor                                                     | na sasank Galaparti, Manikanta Chary Darla,          |     |  |  |  |  |

|    | Siva S                                                   | Sai Prasad Loya and K. Srinivasa Rao                 |     |  |  |  |  |

|    | 11.1                                                     | Introduction                                         | 172 |  |  |  |  |

|    | 11.2                                                     | Various Existing Proposed Anti-Poaching Systems      | 173 |  |  |  |  |

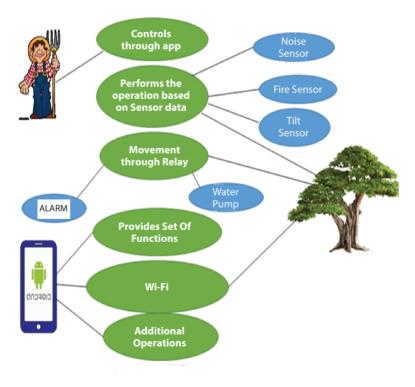

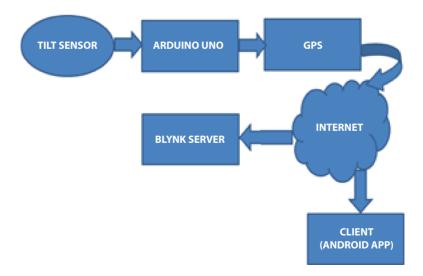

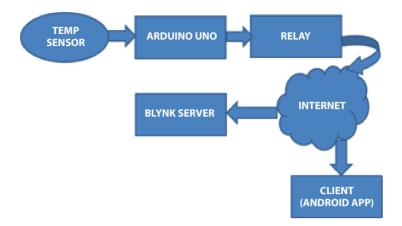

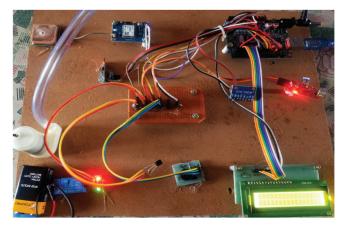

|    |                                                          | System Framework and Construction                    | 174 |  |  |  |  |

|    | 11.4                                                     | Results and Discussions                              | 176 |  |  |  |  |

|    | 11.5                                                     | Conclusion and Future Scope                          | 182 |  |  |  |  |

|    |                                                          | References                                           | 182 |  |  |  |  |

| 12 | Tum                                                      | or Detection Using Morphological Image               |     |  |  |  |  |

|    | Segm                                                     | entation with DSP Processor TMS320C6748              | 185 |  |  |  |  |

|    | T. Anil Raju, K. Srihari Reddy, Sk. Arifulla Rabbani,    |                                                      |     |  |  |  |  |

|    | G. Su                                                    | resh, K. Saikumar Reddy and K. Girija Sravani        |     |  |  |  |  |

|    | 12.1                                                     | Introduction                                         | 186 |  |  |  |  |

|    | 12.2                                                     | Image Processing                                     | 186 |  |  |  |  |

|    |                                                          | 12.2.1 Image Acquisition                             | 186 |  |  |  |  |

|    |                                                          | 12.2.2 Image Segmentation Method                     | 186 |  |  |  |  |

|    | 12.3                                                     | TMS320C6748 DSP Processor                            | 187 |  |  |  |  |

|    | 12.4                                                     | Code Composer Studio                                 | 188 |  |  |  |  |

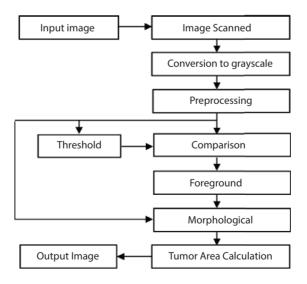

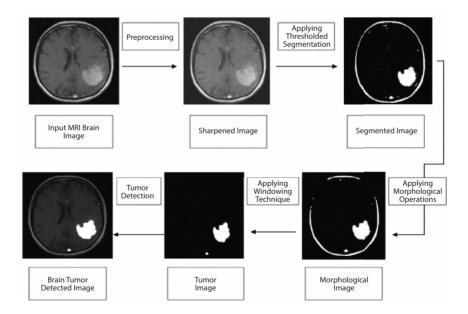

|    | 12.5                                                     | Morphological Image Segmentation                     | 188 |  |  |  |  |

|    |                                                          | 12.5.1 Optimization                                  | 190 |  |  |  |  |

|    | 12.6                                                     | Results and Discussions                              | 192 |  |  |  |  |

|    | 12.7                                                     | Conclusions                                          | 193 |  |  |  |  |

|    |                                                          | References                                           | 193 |  |  |  |  |

| 13 |                                                          | gn Challenges for Machine/Deep Learning Algorithms   | 195 |  |  |  |  |

|    | Raje                                                     | sh C. Dharmik and Bhushan U. Bawankar                |     |  |  |  |  |

|    | 13.1                                                     | Introduction                                         | 196 |  |  |  |  |

|    | 13.2                                                     | Design Challenges of Machine Learning                | 197 |  |  |  |  |

|          | 13.2.1   | Data of Low Quality                           | 197 |

|----------|----------|-----------------------------------------------|-----|

|          | 13.2.2   | Training Data Underfitting                    | 197 |

|          | 13.2.3   | Training Data Overfitting                     | 198 |

|          | 13.2.4   | Insufficient Training Data                    | 198 |

|          | 13.2.5   | Uncommon Training Data                        | 199 |

|          | 13.2.6   | Machine Learning Is a Time-Consuming Process  | 199 |

|          | 13.2.7   | Unwanted Features                             | 200 |

|          | 13.2.8   | Implementation is Taking Longer Than Expected | 200 |

|          | 13.2.9   | Flaws When Data Grows                         | 200 |

|          | 13.2.10  | The Model's Offline Learning and Deployment   | 200 |

|          | 13.2.11  | Bad Recommendations                           | 201 |

|          | 13.2.12  | Abuse of Talent                               | 201 |

|          | 13.2.13  | Implementation                                | 201 |

|          | 13.2.14  | Assumption are Made in the Wrong Way          | 202 |

|          |          | Infrastructure Deficiency                     | 202 |

|          | 13.2.16  | When Data Grows, Algorithms Become Obsolete   | 202 |

|          | 13.2.17  | Skilled Resources are Not Available           | 203 |

|          |          | Separation of Customers                       | 203 |

|          |          | Complexity                                    | 203 |

|          |          | Results Take Time                             | 203 |

|          | 13.2.21  | Maintenance                                   | 204 |

|          | 13.2.22  | Drift in Ideas                                | 204 |

|          | 13.2.23  | Bias in Data                                  | 204 |

|          | 13.2.24  | Error Probability                             | 204 |

|          | 13.2.25  | Inability to Explain                          | 204 |

| 13.3     | Commo    | only Used Algorithms                          |     |

|          |          | nine Learning                                 | 205 |

|          |          | Algorithms for Supervised Learning            | 205 |

|          |          | Algorithms for Unsupervised Learning          | 206 |

|          | 13.3.3   | Algorithm for Reinforcement Learning          | 206 |

| 13.4     | Applica  | tions of Machine Learning                     | 207 |

|          |          | Image Recognition                             | 207 |

|          | 13.4.2   | Speech Recognition                            | 207 |

|          |          | Traffic Prediction                            | 207 |

|          |          | Product Recommendations                       | 208 |

|          | 13.4.5   | Email Spam and Malware Filtering              | 208 |

| 13.5     | Conclu   |                                               | 208 |

|          | Referen  | ices                                          | 208 |

| About th | e Editor | s                                             | 211 |

| Index    |          |                                               | 213 |

# **List of Contributors**

#### Imran Ullah Khan

Dept. of Electronics and Communication Engineering, Integral University, Lucknow, India

#### Nupur Mittal

Dept. of Electronics and Communication Engineering, Integral University, Lucknow, India

#### Mohd. Amir Ansari

Dept. of Electronics and Communication Engineering, Integral University, Lucknow, India

#### A.V. Ananthalakshmi

Department of ECE, Puducherry Technological University, Puducherry, India

#### P. Divyaparameswari

Department of ECE, Puducherry Technological University, Puducherry, India

#### P. Kanimozhi

Department of ECE, Puducherry Technological University, Puducherry, India

#### Jyoti Kandpal

Dept. of Electronics and Communication Engineering, NIT Arunanchal Pradesh, India

#### Rajeswari

Department of ECE, Lakireddy Bali Reddy College of Engineering, Mylavaram, India

#### N. Vinod Kumar

Department of ECE, Lakireddy Bali Reddy College of Engineering, Mylavaram, India

#### K. M. Suresh

Department of ECE, Lakireddy Bali Reddy College of Engineering, Mylavaram, India

#### N. Sai Kumar

Department of ECE, Lakireddy Bali Reddy College of Engineering, Mylavaram, India

#### K. Girija Sravani

Department of ECE, KL University, Green Fields, Guntur-522502, Andhra Pradesh, India

#### P. Kiran Kumar

Koneru Lakshmaiah Educational Foundation (Deemed to be University), Guntur, Andhra Pradesh-522502, India

#### B. Balaji

Koneru Lakshmaiah Educational Foundation (Deemed to be University), Guntur, Andhra Pradesh-522502, India

#### M. Suman

Koneru Lakshmaiah Educational Foundation (Deemed to be University), Guntur, Andhra Pradesh-522502, India

#### P. Syam Sundar

Koneru Lakshmaiah Educational Foundation (Deemed to be University), Guntur, Andhra Pradesh-522502, India

#### E. Padmaja

Koneru Lakshmaiah Educational Foundation (Deemed to be University), Guntur, Andhra Pradesh-522502, India

#### **Ritu Yadav**

ECE Department, I K Gujaral Punjab Technical University, Jalandhar, India

#### Kiran Ahuja

ECE Department, DAVIET, Jalandhar, India

#### K. Sasi Bhushan

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India, 521230

#### U. Preethi

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India, 521230

#### P. Naga Sai Navya

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India, 521230

#### R. Abhilash

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India, 521230

#### T. Pavan

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India, 521230

#### B. Ramesh Reddy

Department of Electronics and Communication Engineering, LBR College of Engineering, Mylavaram, Krishna District, Andhra Pradesh

#### K. Bhargav Manikanta

Department of Electronics and Communication Engineering, LBR College of Engineering, Mylavaram, Krishna District, Andhra Pradesh

#### P.V.V.N.S. Jaya Sai

Department of Electronics and Communication Engineering, LBR College of Engineering, Mylavaram, Krishna District, Andhra Pradesh

#### R. Mohan Chandra

Department of Electronics and Communication Engineering, LBR College of Engineering, Mylavaram, Krishna District, Andhra Pradesh

#### xvi List of Contributors

#### M. Greeshma Vyas

Department of Electronics and Communication Engineering, LBR College of Engineering, Mylavaram, Krishna District, Andhra Pradesh

#### B. V. Anil Sai Kumar

School of Electronics and Electrical Engineering, Lovely Professional University, Punjab, India

#### Suryavamsham Prem Kumar

School of Electronics and Electrical Engineering, Lovely Professional University, Punjab, India

#### Konduru Jaswanth

School of Electronics and Electrical Engineering, Lovely Professional University, Punjab, India

#### Kola Vishnu

School of Electronics and Electrical Engineering, Lovely Professional University, Punjab, India

#### Abhishek Kumar

School of Electronics and Electrical Engineering, Lovely Professional University, Punjab, India

#### Narendra Babu Alur

Department of Electronics and Communication Engineering, and Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### Kurapati Poorna Durga

Department of Electronics and Communication Engineering, and Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### Boddu Ganesh

Department of Electronics and Communication Engineering, and Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### Manda Devakaruna

Department of Electronics and Communication Engineering, and Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### Lakkimsetti Nandini

Department of Electronics and Communication Engineering, and Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### A. Praneetha

Department of Computer Science Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### T. Satyanarayana

Department of Electronics and Communication Engineering, and Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### K. Rani Rudrama

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### Mounika Ramala

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### Poorna sasank Galaparti

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### Manikanta Chary Darla

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### xviii List of Contributors

#### Siva Sai Prasad Loya

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering (Autonomous), Mylavaram, Krishna District, AP, India

#### K. Srinivasa Rao

Department of Electronics and Communication Engineering, KLEF, Vaddeswaram, Green Fields, 522502, Andhra Pradesh, India

#### T. Anil Raju

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering, Mylavaram

#### K. Srihari Reddy

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering, Mylavaram

#### Sk. Arifulla Rabbani

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering, Mylavaram

#### G. Suresh

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering, Mylavaram

#### K. Saikumar Reddy

Department of Electronics and Communication Engineering, Lakireddy Bali Reddy College of Engineering, Mylavaram

#### Rajesh C. Dharmik

Department of Information Technology, Yeshwantrao Chavan College of Engineering, Nagpur

#### Bhushan U. Bawankar

Department of Information Technology, Yeshwantrao Chavan College of Engineering, Nagpur

# Preface

Machine Learning (ML) has touched all corners of human life and industry. Databased learning intelligence supports are the scalability of present technology and architecture. The current ML and deep learning (DL) algorithms require huge consumption of data and power. The industry is looking for an efficient VLSI circuit that can meet the demands of the AI-ML-DL universe. ML can pioneer different sectors throughout design methodologies from RTL design, synthesis, and verification. One of the deepest challenges of chip design is the time-consuming iterative process. Thanks to the learning model, time is considerably reduced. VLSIbased solutions and innovation of AI-ML-DL applications are growing in demand. Internet of Things–based solutions address the various challenges in society that require chips. This new book covers the latest AI/ML techniques, VLSI chip design, and systems to address societal challenges.

# Applications of VLSI Design in Artificial Intelligence and Machine Learning

Imran Ullah Khan, Nupur Mittal\* and Mohd. Amir Ansari

Dept. of Electronics and Communication Engineering, Integral University, Lucknow, India

#### Abstract

In our advanced times, complementary metal-oxide semiconductor (CMOS) based organizations like semiconductor and gadgets face extreme scheduling of products and other different pressures. For resolving this issue, electronic design automation (EDA) must provide "design-based equivalent scaling" to continue the critical industry trajectory. For solving this problem machine learning techniques should be used both inside and "peripherally" in the design tools and flows. This article reviews machine learning opportunities, and physical implementation of IC will also be discussed. Cloud intelligence-enabled machine learning-based data analytics has surpassed the scalability of current computing technologies and architectures. The current methods based on deep learning are inefficient, require a lot of data and power consumption, and run on a data server with a long delay. With the advent of self-driving cars, unmanned aerial vehicles and robotics, there is a huge need to analyze only the necessary sensory data with low latency and low power consumption on edge devices. In this discussion, we will talk about effective AI calculations, for example, fast least squares, binary and tensor convolutional neural organization techniques, and compare prototype accelerators created in field preogrammable gate array (FPGA) and CMOS-ASIC chips. Planning on future resistive random access memory (RRAM) gadgets will likewise be briefly depicted.

Keywords: VLSI, AI, ML, CAD & AVM

<sup>\*</sup>Corresponding author: mittal@iul.ac.in

Abhishek Kumar, Suman Lata Tripathi, and K. Srinivasa Rao (eds.) Machine Learning for VLSI Chip Design, (1–18) © 2023 Scrivener Publishing LLC

## 1.1 Introduction

Rapid growth in IC technology is catching up with IC design capabilities, mainly due to the significant advancement in artificial intelligence. The computational tasks assigned to very large-scale integration (VLSI) are time-consuming processes but when AI is implemented to perform the same computational tasks, the required time will be reduced. As technology advances rapidly, VLSI developers must observe and implement this growth to augment design tools. Improved design methods, features, and capabilities bring the promise of AI to VLSI design. Although artificial intelligence brings many features and methods, it still has certain limitations to bring solutions to various problems. As a result, the advent of machine learning (ML) opens up a slew of new possibilities for collaboration and particular sectors of VLSI and computer-based design. By using AI, chips are designed and implemented. It is seen as the premier application of artificial intelligence. Currently, computer-based design tools are commonly utilised in conjunction with information learned from introductory AI classes. Previously, chips were mostly hand-designed, the chip size was too large, and the performance was slow. Validating those chips based on hand-designed designs is a complex task. These complexities lead to the development of automated tools. The automation tool has been upgraded for other tasks assigned to it. Researchers bring new design methods from time to time, such as memory combinations, new programs in computing tasks, etc., in the design process, which must be mechanised. For these objectives, companies such as Intel, IBM, and others have in-house computer-aided design (CAD) capabilities [1-4]. Cadence, Synopsys, Mentor Graphics, and a slew of other companies sell CAD software, which can be thought of as artificial intelligence applied to chip design. For identifying patterns, documents retrieved or gathered from clusters is sometimes required. Such patterns can be detected by concentrating on things like classifying diverse items, forecasting points of interest, input-output linkages based on their complexity, and deep neural networks with numerous other layers for each pattern, object, and speech recognition application. In the domains mentioned above, technology is of tremendous importance. DNNs must respond to new information by comparing it to previously proposed information or procedures. This has to be expanded to the most recent development level. If the system is non-stationary, the decision-making process must be tweaked in order to enhance the increasing efficiency, which is a result of machine learning [5, 6].

In former times, huge computers made up of large-size vaccum tubes were used. Even though they were heralded as the world's fastest computers at the time, they were no match for current machines. With each passing second, modern computers become smaller, faster, cheaper, more powerful, and more efficient. But what is causing this shift? With the introduction of Bardeen's (1947–48) semiconductor transistor and Shockley's (1949) bipolar transistor at Bell Labs, the entire computing field entered a new era of electronic downsizing. The development span of microelectronics is shorter than the average human lifespan, but it has seen as many as four generations. Small-scale integration (SSI) was a term used in the early 1960s to describe low-density manufacturing procedures in which the number of transistors was restricted to roughly ten.

In the late 1960s, this gave way to Medium-Scale Integration (MSI), which allowed for the placement of roughly 100 transistors on a single chip. The Transistor-Transistor Logic (TTL), which provided higher integration densities, outlasted other IC families' Emitter-Coupled Logic (ECL) and established the foundation for integrated circuit uprising. Texas Instruments, Fairchild, Motorola, and National Semiconductor all trace their roots back to the establishment of this family. The development of transistor counts to roughly 1,000 per chip, known as large-scale integration, began in the early 1970s (LSI). On a single chip the number of transistors had surpassed 1,000 by the mid-1980s, ushering in the era of very high-scale integration (VLSI). Despite the fact that significant advances have been achieved and transistor counts have increased, TTL was vanquished in the struggle against the MOS at this time, due to the same concerns that put the vacuum tube out of commission: power consumption and the number of gates that could be placed on a single die. With the introduction of the microprocessors, Intel's 4004 in 1972 and the 8080 in 1974, the second period of the integrated circuit revolution began. Texas Instruments, Infineon, Alliance Semiconductors, Cadence, Synopsys, Cisco, Micron, National Semiconductor, STMicroelectronics, Qualcomm, Lucent, Mentor Graphics, Analog Devices, Intel, Philips, Motorola, and many others are among the firms that make semiconductors today. Many aspects of VLSI have been demonstrated and committed to, including programmable logic devices (PLDs), hardware languages, design tools, embedded systems, and so on. As an example, the creation of an artificial neural network necessitates the use of several neural hubs as well as various amplifiers stages. With an increase in the number of neural hubs, a larger area is required to position such nodes, and the number of neural node interdependencies in diverse layers appears to be modest. It complicates cell networking in a small chip zone; therefore big area specifications for

speakers and storage devices limit the device's volume. Due to the device's unpredictable nature, using a fuzzy logic chip with a large number of information sources is impractical.

# 1.2 Artificial Intelligence

Artificial intelligence is a branch of computer emphasis on invention of technology that can engage in intelligent actions. Humans have been fascinated by the ability to construct sentient robots since ancient times, and today, thanks to the introduction of computers and 50 years of scientific research into machine intelligence development tools, that dream is becoming a reality. Researchers are developing computers that can think like humans, interpret speech, defeat human chess grandmasters, and perform a slew of other previously unimaginable tasks [2].

# 1.3 Artificial Intelligence & VLSI (AI and VLSI)

The field of expert systems functioning as design assistants is where artificial intelligence (AI) is thriving in silicon chip and printed circuit design schematics [3, 9]. However, AI is simply one facet of expert technology. VLSI designing is a difficult task. That complexity is also multi-dimensional. Self-design and the patterned origin of the construction process are two others. AI language aids in the resolution of such difficult issues. These language properties, when joined with intelligent systems, enable a critical first step in addressing extremely difficult issues, notably confirming the design's validity [3].

# 1.4 Applications of AI

Uses of AI are developing quickly. These are being sought after in college research as well as in modern conditions like in industries. The field of VLSI design is adapting AI rapidly [7, 8, 11]. The first important application is the expert system, an intelligent computer software that mimics the behaviour of a human by employing analytical techniques to a specific domain's knowledge base. Expert systems in the professional field should be capable of resolving instant and reasonably challenging situations. Each difficulty should have one or even more solutions provided by an expert system. These alternatives should be reliable. Expert systems differ from

regular computer programs in several important ways. "Intelligence" is specifically written into the code of traditional computer programmes. The code subsequently fixes the issue by using a well-known algorithm to do so. The "intelligence" part of expert systems is distinct from the controlling or reasoning part. Modification and improvements to the learning can be made without affecting the control portion [4]. The key aspect of artificial intelligence's knowledge-based techniques is that they ask human specialists what knowledge they use to solve certain tasks and then design multiple algorithms formats that can directly express that information. Researchers that have used this technology in a variety of VLSI applications have seen some advantages over simpler methods., such as those discussed in [4].

Making incremental improvements will be easier by using this method and it is easier for the system to describe what it is doing and why. For human experts it is easy to identify where the system's knowledge is incorrect or incomplete and describe how to solve it. It is easier to interact with human professionals' abilities.

In VLSI design these expert system are being used widely [7, 8, 10, 12]. Design Automation Assistant (DAA) was one of the first expertise solutions for VLSI design. In VLSI, it is very crucial. Researchers from Carnegie-Mellon University and AT&T Bell Labs collaborated to create it. The original DAA had rules describing several synthesis activities. Registers, operators, data routes, and control signals were used to represent production rules. Over the years, the DAA technology has been continually improved and expanded [3]. Its database contains over 500 rules that are utilised in the construction of various systems. NCR's Design Advisor serves as a professional help. The design advisor's job is to offer guidance in six areas for the creation of semi-custom CMOS devices using a library of functional blocks. Simulations, functions, timing, testability, design rules, and specification feasibility are all covered in the advisor.

#### 1.5 Machine Learning

Advanced systems are being used and developed that are capable of learning and adapting without explicit instructions by analysing and drawing inferences from data patterns utilising specific algorithms models [13]. Machine learning also includes Artificial intelligence. Machine learning covers a vast area in medicine, email filtering, speech recognition, and computer vision. For many uses, developing traditional algo is not possible. The solution is machine learning [14–16]. The use of machine learning in biological datasets is on the rise.

#### 6 MACHINE LEARNING FOR VLSI CHIP DESIGN

Computation analytics, which emphasizes the use of computers to generate predictions, is closely related to machine learning; however, not all algorithms are statistical learning. Unsupervised learning is the focus of data mining, which is a similar topic of research. Biological brains is also a very important application of machine learning [17, 18].

# 1.6 Applications of ML

#### 1.6.1 Role of ML in Manufacturing Process

A manufacturer can gain actual benefits with the use of ML, such as increased efficiency and lower costs. Machine learning can be used to improve the industry sector. In the case of Google, the company reduced its data center electricity usage by 40% by using custom ML. Google also tried to reduce it manually but that improvement was not acheived. Many other companies adopted ML. Using machine learning to improve internal operational efficiency, more than 80% say it helps them reduce costs.

#### 1.6.2 Reducing Maintenance Costs and Improving Reliability

Machine learning can be used to create optimized maintenance schedules based on actual equipment usage. In the same way, customers will also benefit, since they can be offered personalized maintenance plans.

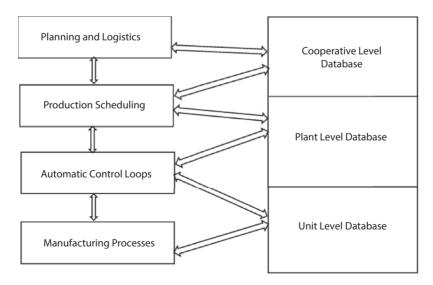

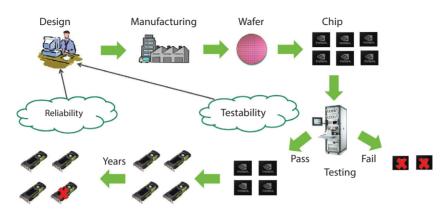

Figure 1.1 Machine learning in process industries.

Using machine learning to more accurately predict customer demand, a textile manufacturer was able to reduce inventory levels by 30%. By using ML, inventory levels and waste can also be reduced.

#### 1.6.3 Enhancing New Design

With the help of ML, the consumer exactly knows the application of the product. If the product fails, anyone can know the reason behind it. These problems can be fed back to the team, which will remove all the problems with the help of machine learning. By using ML researchers can enhance their R&D capabilities. Figure 1.1 shows the hierarchical applications of data analytics and machine learning in process industries.

### 1.7 Role of ML in Mask Synthesis

Various resolution enhancement techniques (RET), such as optical proximity correction (OPC), source mask co-optimization, and sub-resolution assist functions (SRAF), become necessary as technological nodes reach the limits of optical wavelengths. Machine learning will be used by various RETs to improve mask synthesis turnaround time.

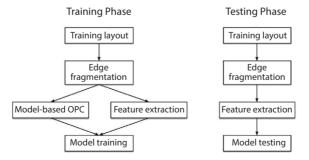

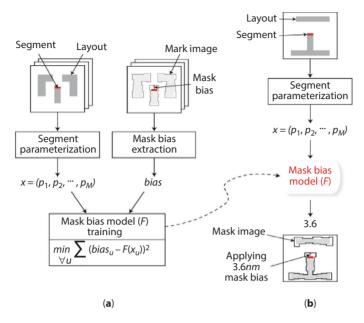

Figure 1.2 provides a structured mask synthesize flow in which source patterns (layout) are given and mask patterns are created after iterative optimization techniques such as SRAF generation, OPC, mask rule check (MRC), and lithography compliance check (LCC) [19]. A sub-resolution help function is included in SRAF generation to make target pattern printing easier. The target pattern's edge part is tailored for robust lithography in OPC. Mask manufacturing rules should be reviewed following these optimization techniques in MRC to assure mask fabrication friendliness. In Figure 1.3 to correct for image imperfections brought on by diffraction or other process effects,

Figure 1.2 Machine learning-based optical proximity correction flow [20].

Figure 1.3 Optical proximity correction [21].

photolithography enhancement techniques like optical proximity correction (OPC) are frequently used. Due to the limits of light, OPC is mostly required in the production of semiconductor devices in order to maintain the edge placement integrity of the original design after processing into the etched image on the silicon wafer. Inconsistencies in the projected images, such as lines that are larger or thinner than intended, can be corrected by altering the pattern on the photomask used for imaging to test printability. LCC runs lithography simulation under such a series of process windows.

As illustrated in Figure 1.2, varied focus and dosage conditions are used to develop printed contours, such as minimal, inner, and outer contours (b). Two metrics are presented to evaluate the methods; in particular, the spacing between the target pattern profile and the nominal profile is measured by Edge Placement Error (EPE), while the area between the inner and outer profiles is measured by Process Variation (PV) Band. Minimizing the EPE and PV bands is a common RET goal. The flow of machine learning–based optical proximity correction and how optical proximity correction is produced are depicted in Figures 1.2 and 1.3.

### 1.8 Applications in Physical Design

This part will incorporate a few critical utilizations of pattern matching and AI in physical design (counting physical verification).

#### 1.8.1 Lithography Hotspot Detection

A hotspot has been located by hotspot detection problem on a given layout with quick turnaround time. Pattern images using complicated lithography models have been obtained using conventional lithography simulation [22]. In spite of the fact that it is exact, full-chip lithography simulation is computationally costly and, in this way, we cannot give quick criticism to direct early physical design stages. Area of hotspot identification assumes a significant part in spanning the immense role among modeling and process aware physical design. A great deal of machine learning-based hotspot identification works. Machine learning methods build a relapse model in light of a bunch of preparing information. This strategy can normally recognize a past obscure hotspot. Be that as it may, it might produce a false alarm, and the hotspot recognized is not a genuine one. Step-by-step instructions to further develop the recognizing precision is the principal challenge while taking on machine learning methods. Numerous new methodologies use support vector machines (SVM) and artificial neural network (ANN) strategies to develop the hotspot discovery kernel. In [23], 2D distance change and histogram extraction on pixel-based design pictures for building SVMbased hotspot recognition are examined.

#### 1.8.2 Pattern Matching Approach

In hotspot identification, design matching-based techniques are also commonly used. [23] proposes a format diagram to represent pattern-related CD variety. Hotspots such as closed highlights, L-shaped pieces, and complex examples can be observed using the result graphic. Range design [24] is proposed to condense process-subordinate particulars, and [25] is improved to accommodate new types of hotspot. A reach design is a 2-D format of square forms with additional string-based criteria. Each reach design is linked to a grading system that displays the potentially hazardous places based on the yield effect. The hotspot designs are saved in a pre-defined library, and the location interaction searches for hotspots using string matching. Although this method is precise, developing a range pattern requires a grid-based format foundation, which can be time consuming when the number of grids is large. By extracting basic topological features and showing them as design guidelines, Yu, Y. T. et al. [24] propose a DRC-based hotspot recognition. When in doubt, hotspot detection can be seen by looking at the process through a DRC engine. A matching-based hotspot characterization conspire is proposed in [27]. Data mining techniques are used to group the hotspots into groups. Each bunch's delegate hotspot is then identified and saved in a hotspot library for future hotspot identification. [27] relies on a distance metric of several example tests, which is defined as a weighted integral across the region where a couple of hotspot designs contrast (XOR of examples). It is sensitive to little variations or movements. For hotspot grouping, [28] proposes an Improved Tangent Space (ITS) based measurement. It is a supplement to the widely used tangent space algorithms [29–31] in the field of computer vision. The L2 standard of the distinction of the comparing turning elements of the polygons is the ITS measurement, which characterises a distance metric of a couple of polygons [29, 30]. The turning capacity of a polygon calculates the angle of the counter clockwise tangent as a component of the standardised circular length, which is calculated from a polygon's reference point. The ITS-based measurement is simple to register and is forgiving of minor form variations or movements. The hotspot setup can achieve improved precision using ITS-based measurement.

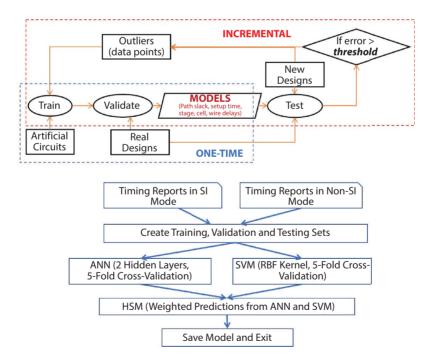

## 1.9 Improving Analysis Correlation

Examination miscorrelation exists when two unique devices return various outcomes for a similar investigation task (parasitic extraction, static timing analysis (STA), and so forth) even as they apply something very similar to "laws of physics" to similar information. As delineated in Figure 1.4, better precision generally comes at the expense of more calculation. Hence, miscorrelation between two examination reports is frequently the inescapable outcome of runtime effectiveness requirement. For instance, close down timing is excessively costly (device licenses, gradual examination speed, loops of timing window combination, query speed, number of corners, and so on) to be utilized inside close enhancement loop. Miscorrelation forces presentation of design protects groups as well as cynicism into the stream. For instance, if the place-and-route (P&R) instrument's STA report verifies that an endpoint has positive most terrible arrangement slack, while the signoff STA apparatus establishes that a similar endpoint has negative most obviously awful slack, a cycle (ECO fixing step) will be required. Then again, assuming the P&R instrument applies cynicism to guard band its miscorrelation to the sign off apparatus, this will cause unnecessary measuring, safeguarding or VT-swapping activities that cost region, power and design plan. Miscorrelation of timing examinations is especially unsafe: (i) timing conclusion can consume up to 60% of configuration time [32], and (ii) added guard bands do not just demolish power-speed-area compromises [33], but can likewise prompt non-convergence of the design signoff timer relationship. Relationship to signoff timing is the most significant objective for ML in back-end plan. Further developed correlations can give "better exactness for free" that moves the expense precision trade off (for example accomplishing the ML impact in Figure 1.4) and optimize iterations, completion time, overdesign, and instrument license uses along the whole way to definite design signoff. These models further develop precision of delay and slew assessments alongside by the timer correlation, with the end goal that less invocation of signoff STA are required during gradual gate sizing estimation [34]. [32] applies profound figuring out how to demonstrate and address difference between various STA apparatuses as for flip-flop setup time, cell arc delay, wire delay, stage deferral, and way slack at timing endpoints. The methodology accomplishes significant (various stage delays) decreases in miscorrelation. Both a one-time preparing strategy utilizing artificial and genuine circuit topologies, as well as a incremental training stream during production utilization, are portrayed (Figure 1.4). A mix of electrical, functional and topological boundaries are utilized to foresee the incremental progress times and arc/path delays because of SI impacts. From this and different works, a clear "easy decision" is to utilize

**Figure 1.4** Flow and results for machine learning of static timing analysis tool miscorrelation [32–35].

#### 12 MACHINE LEARNING FOR VLSI CHIP DESIGN

Hybrid Surrogate Modelling (HSM) [32] to join anticipated values from various ML models into definite predictions. The profit from venture for new ML applications would be higher when x is bigger. Next Targets. [23] recognizes two close term augmentations in the domain of timer examination correlation. (1) PBA from GBA. Timing examination cynicism is decreased with path-based analysis (PBA), at the expense of essentially more prominent runtime than conventional graph-based analysis (GBA). In GBA, most exceedingly awful (resp. best) changes (for max (resp. min) delay analysis) are engendered at each pin along a timing path, prompting moderate appearance time estimates. PBA computes path explicit change and appearance times at each pin, decreasing cynicism that can comfortably surpass a phase delay. Figure 1.4 represents flow and results for machine learning of static timing analysis tool miscorrelation.

#### 1.10 Role of ML in Data Path Placement

S. Ward et al. [12] suggested a programmed data path extraction in the accompanying new manner. Makes a decision about the various data path and afterward allots the positions to them to streamline it. This improvement is continued in an overall approach to driving or putting the data alongside new position stream as shown in Figure 1.5 [12]. SVM and ANN techniques are consolidated at the underlying training stage to segregate and pass judgment on the data path. When both procedures are used, the result is a competent model that is treated as a reduced model at run time. In the SVM model, a fault tolerance is determined by the arrangement of working data paths. In any event, ANN will generate choices from the training data, similar to how people organise their neurons. Whether it is a data path or a non-data path, accuracy of assessment is crucial. SVM and ANN are both capable of achieving this. Distinguishing data path design from opaque design is further improved, which can be addressed in the preparation stage of data learning models. To recognise the unique case, certain edge thresholds are set while involving SVM and AVM assessments.

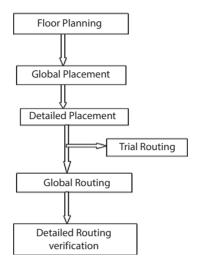

#### 1.11 Role of ML on Route Ability Prediction

The work [36–41] materials the main calculated study on route capacity forecast in light of Convolutional Neural Network. Subconsciously, that is clearly a promising course; however, it isn't all around concentrated beforehand. The method Route Net can just estimate general route ability

Figure 1.5 General physical design flow [36].

(Figure 1.5) in conditions of Design Rule Violation count thinking about macros [42]. Route Net accomplishes tantamount accuracy in contrast with that of worldwide routing; however, it is by and large significant degrees speedier really, assuming preparation period is regularly counted. Figure 1.5 shows general physical design flow to the best of our agreement; this is really the first route capacity predictor which incorporates both such extraordinary exactness and incredible speed. In anticipating DRC hotspot regions considering macros, it makes a huge improvement of half precision improvement versus worldwide routing. Moreover, Route Net remarkably outflanks SVM and calculated regression-centered expectation.

### 1.12 Conclusion

In this article, we have demonstrated the use of Artificial Intelligence in several aspects of the VLSI Logical and Physical Plan, such as assembly, miscorrelation, power inquiry, testing, mask synthesis, transition and connection delay, and CAD tools. However, AI has several applications in the VLSI design stages. Furthermore, the use of AI systems to VLSI backend design is still in its early stages. In the SRAF era, for example, pixel-by-pixel assumptions are necessary, and only direct models are utilised, limiting the usage of more complex models due to high computational costs. In general, OPC is only sensible to embrace direct models. Such advancement

#### 14 MACHINE LEARNING FOR VLSI CHIP DESIGN

concerns necessitate the creation of a new cover image in a specific format. It deserves more investigation. It is unclear whether a generic representation of arrangement data exists or whether a customised integrate decision can be made. Furthermore, unlike domains with extensive AI assessment, such as image confirmation, where a large proportion of data is open, obtaining appropriate data in VLSI plan for planning powerful and exact models is often arduous and costly. As a result, it is critical to develop approaches to enhance showing precision while reducing the need for massive data so that AI may be widely adopted. These issues will be further looked into in the future.

## References

- 1. Miller, A. (1989). From Expert Assistant to Design Verification: Applications of AI to VLSI Design, *Session 11Al, IEEE*, 2 (406–410).

- Steinberg, L. I., & Mitchell, T. M. (1984). A knowledge based approach to VLSI CAD the redesign system. In *Proceedings of the 21<sup>st</sup> Design Automation Conference* (412–418). IEEE Publications.

- 3. Kowalski, T. J., & Thomas, D. E. (1983). The VLSI design automation assistant prototype system. In *20th Design Automation Conference* (479–483). IEEE Publications.

- 4. Kelly, Van E. (1984). The CRITTER system: Automated critiquing of digital circuit designs. In *Proceedings of the 21st Design Automation Conference* (419–425). IEEE Publications.

- Steele, R. L. (1987). An expert system application in semicustom VLSI design. In A. O'Neill & D. Thomas (Eds.). *Proceedings of the 24th ACM/IEEE Design Automation Conference*, Acad. med. (679–688).

- 6. Farahat, H., Eldessouki, A., Mahmoud, M. Y., & Elsimary, H. (1989). An expert system for VLSI layout design, *International Conference on Systems Engineering* (529–532). IEEE Publications.

- Stefik, M., & Conway, L. (1982). Towards the principled engineering of knowledge. AI Magazine, 3(3), 4–16. (Reprinted in Readings from the AI Magazine, Volumes 1-5, 1980-1985, 135-147, 1988).

- 8. Kim, J., & McDermott, J. P. (1983). TALIB: An IC layout design assistant. In *Proceedings of the AAAI* (197–201).

- Rabbat, G. (1988). VLSI and AI are getting closer. *IEEE Circuits and Devices* Magazine, 4(1), 15–18. https://doi.org/10.1109/101.926

- Kowalski, T. J., Geiger, D. J., Wolf, W. H., & Fichtner, W. (1985). The VLSI design automation assistant: From algorithms to silicon. *IEEE Design and Test of Computers*, 2(4), 33–43. https://doi.org/10.1109/MDT.1985.294721

- 11. Engineers garage [Web]. http://www.engineersgarage.com/articles/vlsidesign-future, Retrieved September 30 2012.

- S. Ward, D. Ding, and D. Z. Pan, Pade: A high-performance placer with automatic datapath extraction and evaluation through high dimensional data learning, in DAC Design Automation Conference 2012, pp. 756–761, 2012.

- 13. Mitchell, T. (1997). *Machine learning*. McGraw-Hill. ISBN 0-07-042807-7, OCLC 36417892.

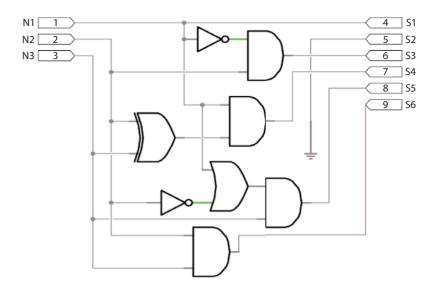

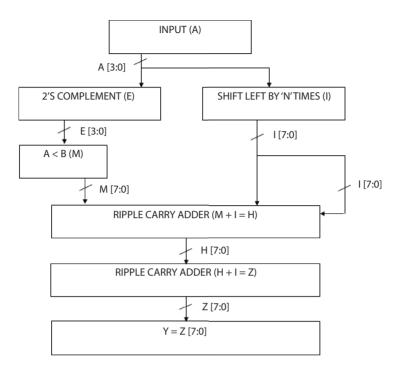

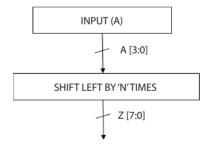

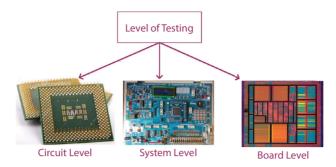

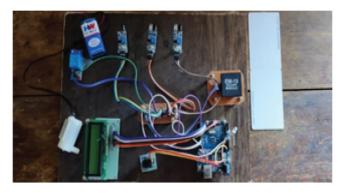

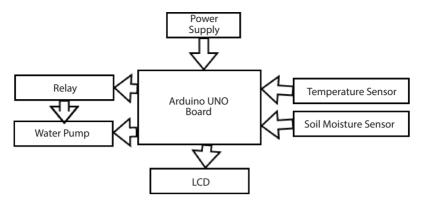

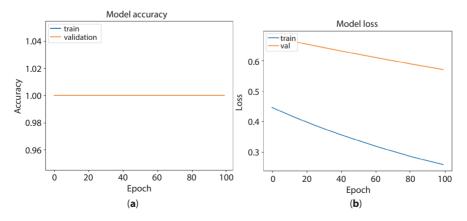

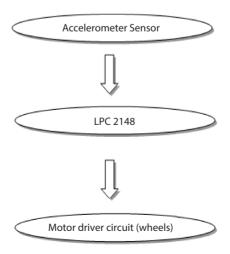

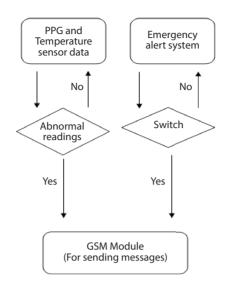

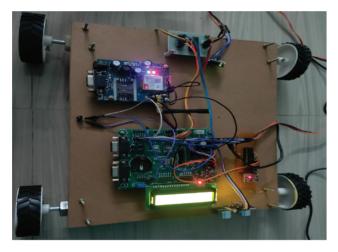

- Koza, J. R., Bennett, F. H., Andre, D., & Keane, M. A. (1996). Automated design of both the topology and sizing of analog electrical circuits using genetic programming. *Artificial intelligence in design* 1996. Springer, Dordrecht. 151–170. https://doi.org/10.1007/978-94-009-0279-4\_9